端口模式规则

wire类型:

wire类型通常用于描述连续赋值的信号,如组合逻辑的输出。- 在模块调用时,如果端口连接的是组合逻辑的输出或者是一个需要持续驱动的信号(如输入端口),则通常应声明为

wire类型。- 输入端口(

input)和双向端口(inout)在模块内部必须声明为wire类型,因为它们反映了外部信号的变化,并且不能保存这些信号的值

reg类型:

reg类型用于描述过程赋值语句(如initial和always块)中的信号。- 在模块调用时,如果端口连接的是时序逻辑的输出(如触发器的输出),或者是一个需要在过程块中赋值的信号,则通常应声明为

reg类型。- 输出端口(

output)在模块内部可以是wire或reg类型,这取决于该端口是否需要保存数值。如果需要保存数值(如在时序逻辑中),则应声明为reg类型。

子模块调用的两种方式:

直接端口映射:

在这种方式中,子模块的端口直接映射到父模块的相应信号上。端口类型(wire或reg)在父模块和子模块之间需要保持一致,或者至少需要确保信号在连接时能够正确传递。

参数化调用:

在这种方式中,子模块被例化为一个实例,并通过参数传递来改变子模块中的某些参数值。

参数化调用不影响端口类型的规则。端口的类型仍然需要根据信号的用途和连接方式来确定。

注意

在模块调用时,需要确保端口名称、类型和位宽在父模块和子模块之间保持一致。

如果子模块的端口在父模块中被用作不同的类型(例如,将子模块的output reg类型端口连接到父模块的input wire类型信号),则可能需要通过额外的逻辑来转换信号类型。

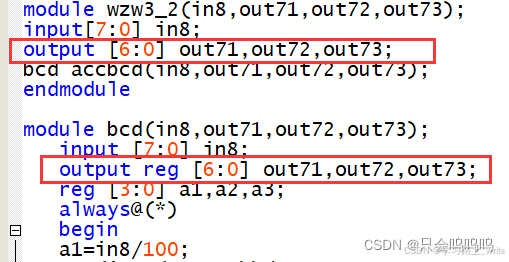

主模块的output不能加reg,只在子模块的output 加reg。

关于子模块调用,有两种调用方式。

可以参照这个例子,搬过来了:(在下面只会呜呜呜 前辈FPGA中的output or inout port xxx must be connected to a structural net expression错误-优快云博客![]() https://blog.youkuaiyun.com/m0_57079595/article/details/123858285

https://blog.youkuaiyun.com/m0_57079595/article/details/123858285

第一种是位置对应,如:bcd accbcd(in8,out71,ou72,out73),如上图所示。

第二种是信号名对应方式,此时不必按顺序。如:accbcd(.in8( in8 ),.out71(out72),.out72(out71),.out73(out73))。.xxx对应的是子模块中的变量,(xxx)括号内对应的是主模块的参数。

对于简单的代码来说,子模块和主模块写在同一Verilog HDL file内即可

3328

3328

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?