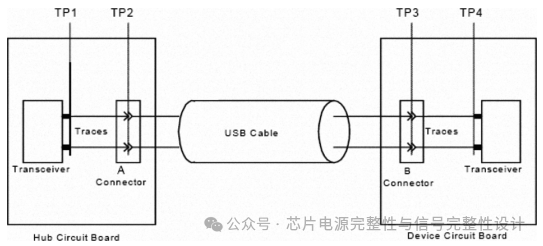

USB2.0连接的拓扑结构如图所示,在这种拓扑结构中,有HUB电路和Device电路。两个USB收发器通过USB电缆连接。接下来的仿真真中Hub电路被IC替换,基于当前的应用,信号观测点T2。

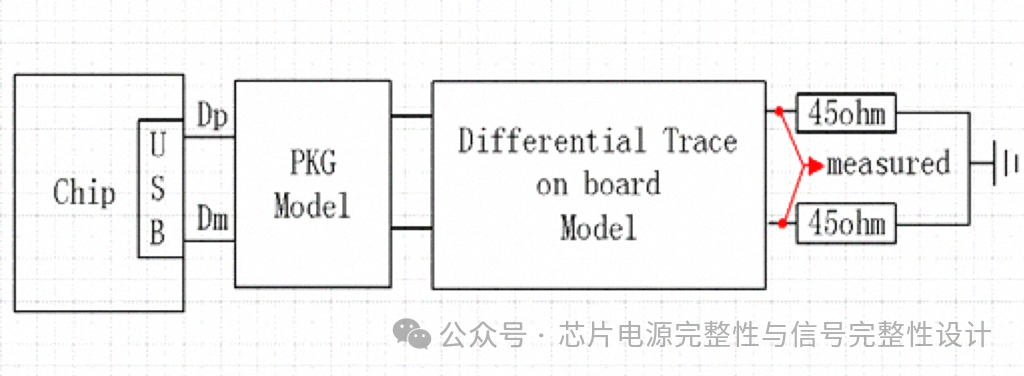

USB2.0 IO集成在某IC设备中,该芯片封装为标准QFP 28x28mm, 256引脚数封装。采用Down-bond技术,以减少封装总引脚数,降低成本,USB2.0总共10个pin连接到封装引脚上,包括电源、接地和差分对。仿真示意图如下图所示,仿真链中包括封装模型、PCB差分对模型,差分走线用两个45Ohm电阻端接。

如下图分别为PKG和PCB走线方式。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?