在高速数字系统中,门级电路的翻转速率不断提高,尽管DDR3的FLY-BY拓扑结构和FPGA内部优化的物理层I/O接口已经大幅提高了信号完整性,但是高速信号在经过(PCB上)无源的互连通道时会产生延迟、反射、衰减、串扰、SSN等,带来信号完整性及由此导致的信号畸变和时序违反等问题。在DDR3Leveling操作过程中数据选通(DQS)信号需要对时钟(CK)信号、数据(DQ)信号进行采样,所以仍需对相关信号的信号完整性进行分析,并考虑其时序的设计要求。下面对时钟和数据信号以及数据选通信号进行详细分析。

时钟和数据信号的建立、保持

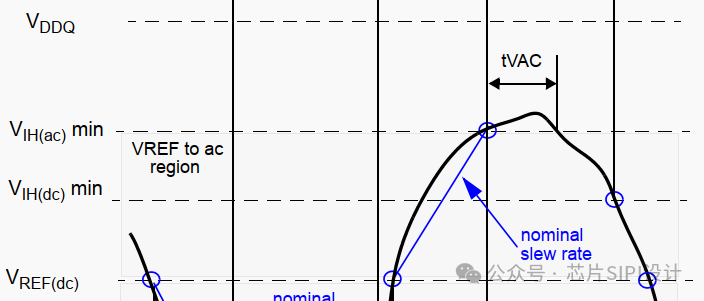

数据选通信号对时钟信号或数据信号进行采样时,需要充分考虑信号的建立时间和保持时间。而时钟或数据信号在电平翻转(沿跳变)时,任何干扰都会影响到建立时间和保持时间,进而使写入时信号到SDRAM芯片的固有延时发生变化。输入信号电平发生有效翻转后,信号必须在VIH(AC)以上或在VIL(AC)以下保持一定时间的电平才能称之为有效电平,这段时间叫做tVAC,它是跟信号翻转速率(slewrate)相关的,如下图所示。在DDR3中,即使时序裕量不能满足,也必须满足tVAC的要求。

JEDEC规范中明确定义了DDR3 SDRAM的控制、地址和数据信号的建立时间与保持时间需求。以数据信号为例(时钟信号与之类似),tDS=tDS(base)+ΔtDS,tDH=tDH(base)+ΔtDH,其中tDS和tDH分别为总的建立时间和保持时间,tDS(base)和tDH(base)分别为建立时间和保持时间的基本值,ΔtDS和ΔtDH分别为信号上升沿与下降沿翻转速率的补偿值。

1241

1241

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?