HDMI高速接口的发送端物理层电路在结构上通常比较固定,除了提供时钟的锁相环和必要的数字控制单元外,还设计串并转换器和末端驱动电路的设计。

发送端驱动电路

在高速接口的设计中,发送端的驱动电路通常有两种结构被经常使用,即LVDS型和CML 型驱动电路。

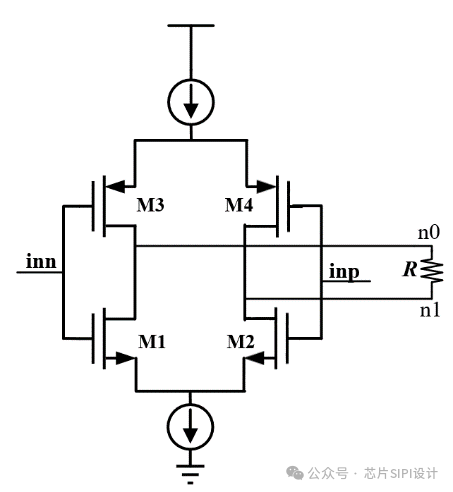

图是常见的LVDS驱动电路的电路图,电路的工作原理非常的简单,当输入信号inp为高电平,而输入信号inn为低电平时,晶体管M2和M3关闭,M1和M4打开,电流的流经方向为M4-n1-n0-M1,即电阻两端的电压差(n0-n1)为负,当输入信号inp为低电平,而输入信号inn为高电平时,晶体管M2和M3打开,M1和M4关闭,电流的流经方向为M3-n0-n1-M2,即电阻两端的电压差(n0-n1)为正,可以看到,只要电阻两端的电压差足够大,就可以以电阻两端的电压差正负表征逻辑“1”和逻辑“0”,由于摆幅并非数字电路中的轨至轨,因此非常适合用在高速电路中。

相比于传统的CMOS电路,CML电路能够高速地工作在低电压条件下,虽然它的功耗相对有所提高,但近几年随着相关技术的成熟,这一缺点已经有所改进,发展至今,由于其电路实现上的便利以及在高频时钟下的速度优势,CML电路及其衍生的电路结构被广泛地应用在各种高速电路中。

364

364

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?