url: https://www.bilibili.com/video/BV1du17YfE5G/?spm_id_from=333.337.search-card.all.click&vd_source=7a1a0bc74158c6993c7355c5490fc600

这堂课没有硬核的内容,基本就是介绍并行计算一些基本概念,还有硬件体系结构的一些基础知识。

笔记只记录我认为有用的部分。

基本概念

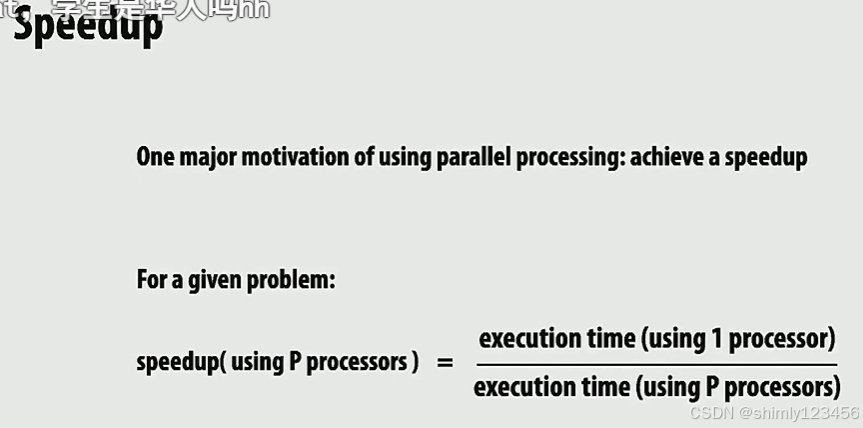

加速比计算公式:

超标量处理器

现代处理器:超标量处理器 (每单位时间可以执行大于 1 个指令的处理器)

不需要多核,只要多发射处理器就能做到,比如果壳处理器就有顺序双发射版本。

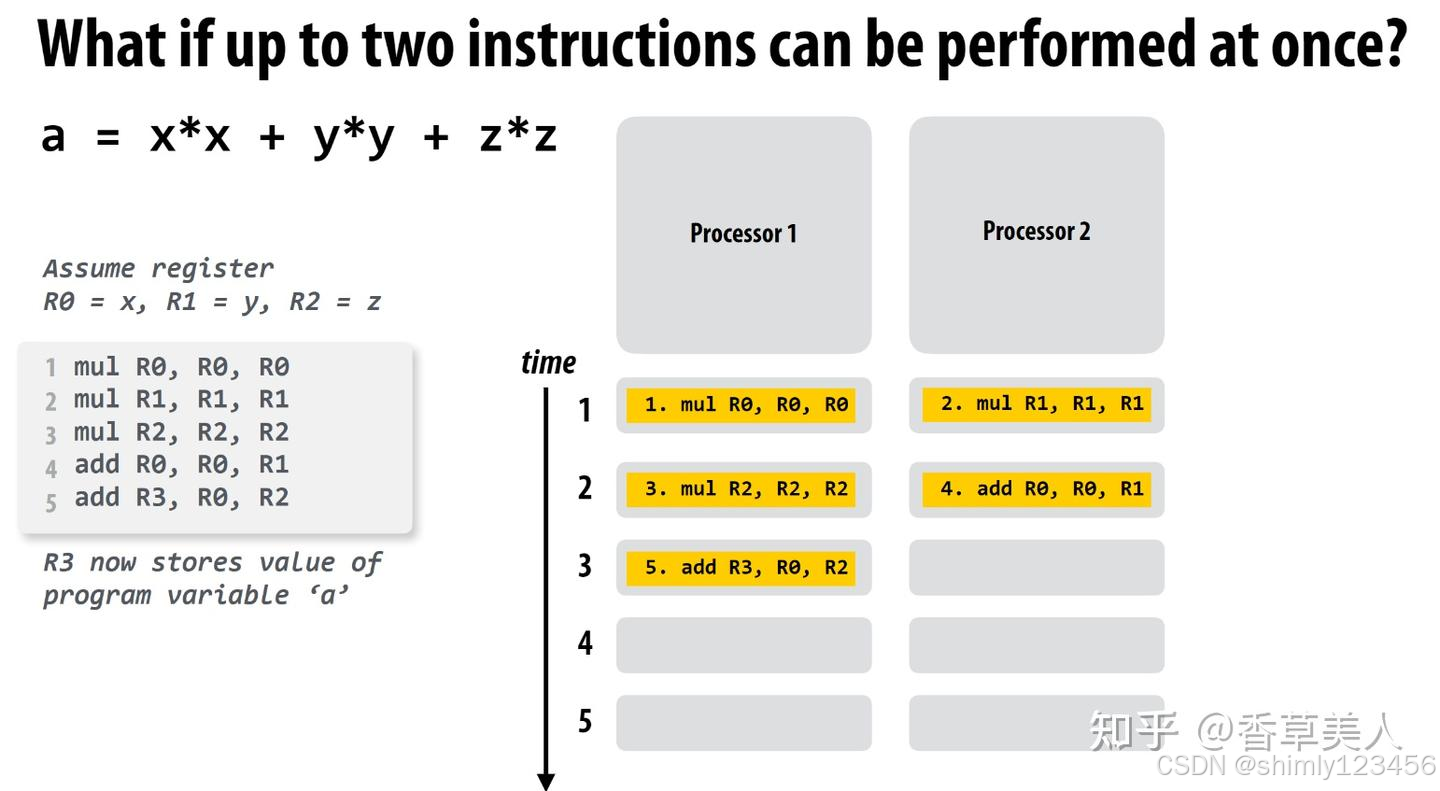

这个例子展示的核心思路就是将前后没有依赖关系的指令分配到不同的执行上下文中执行, 从而实现并行加速。

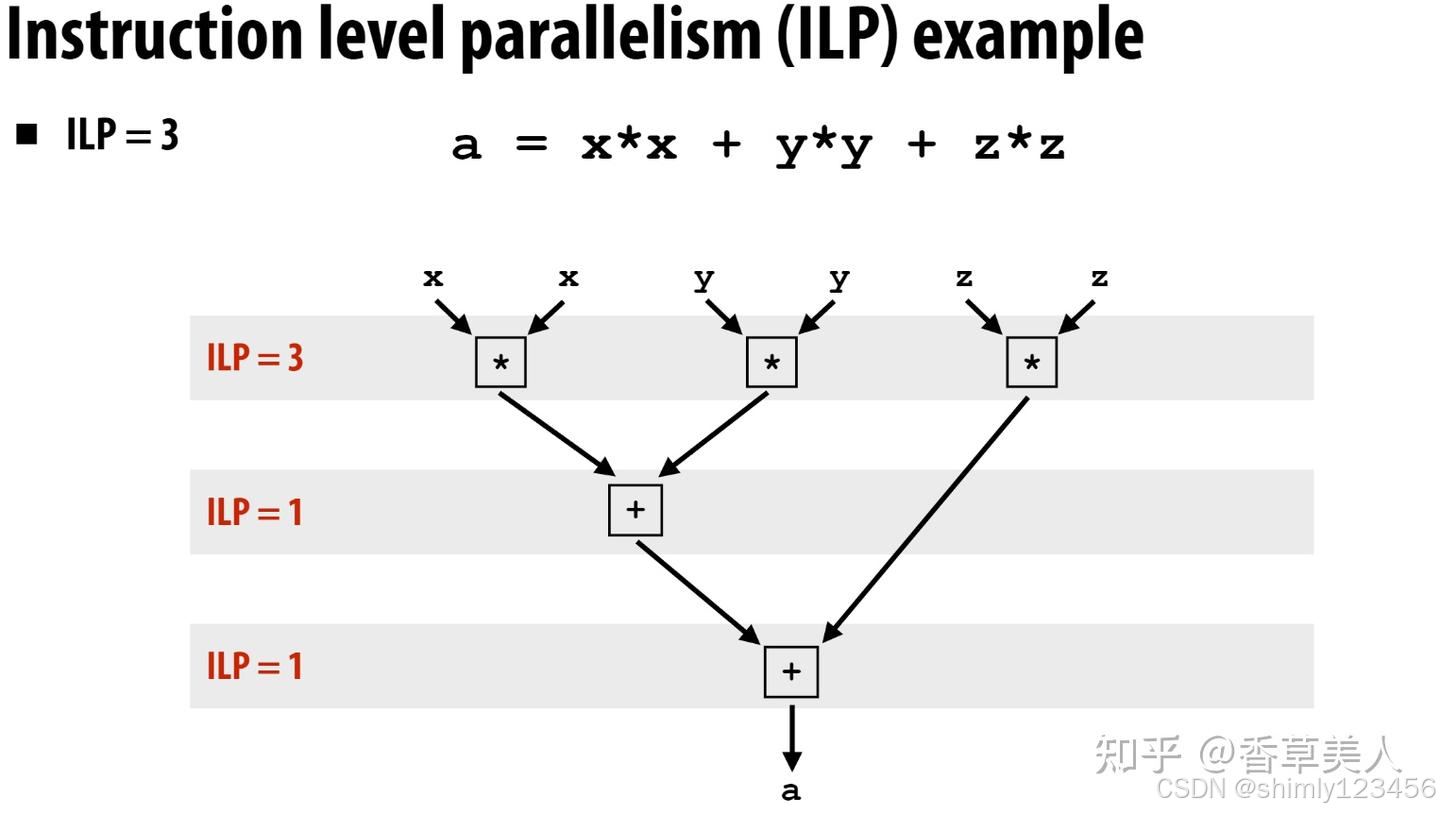

这里还引入了ILP的概念, 即Instruction Level Parallelism, ILP表示在同一时刻可以并行执行的指令数量。上述例子的ILP如下:

基于之前并行加速的例子的原理, 可以设计一种超标量处理器Superscalar execution, 其核心思想是:

- 能够自动发现指令序列中的独立指令

- 可以在多个执行单元上并行执行这些指令

- 在保证程序正确性的前提下实现并行

下面是这类处理器的简易结构图:

这里的Out-of-order control logic是现代处理器中的一个关键组件,负责管理指令的乱序执行。功能是分析指令间的依赖关系、识别可以并行执行的指令并动态调度指令的执行顺序。

指令停顿

1.什么是处理器停顿

- 当处理器无法执行指令流中的下一条指令时发生

- 原因是后续指令依赖于尚未完成的前序指令的结果

- 这种情况会导致处理器暂时无法继续执行

2.内存访问是主要停顿源 - 示例代码展示了典型的内存依赖: assembly ld r0 mem[r2] # 从内存加载数据到r0 ld r1 mem[r3] # 从内存加载数据到r1 add r0, r0, r1 # 需要等待前两条加载指令完成

- add指令必须等待两个内存加载操作完成才能执行

3.内存访问延迟问题 - 内存访问时间约为数百个时钟周期

- "访问时间"是衡量延迟的指标

- 这种长延迟会导致严重的性能损失

4.影响 - 降低处理器效率

- 影响指令级并行的效果

- 是处理器性能优化需要重点考虑的问题

这个问题也是为什么现代处理器设计中会采用多级缓存、预取等技术来减少内存访问造成的停顿。

缓存

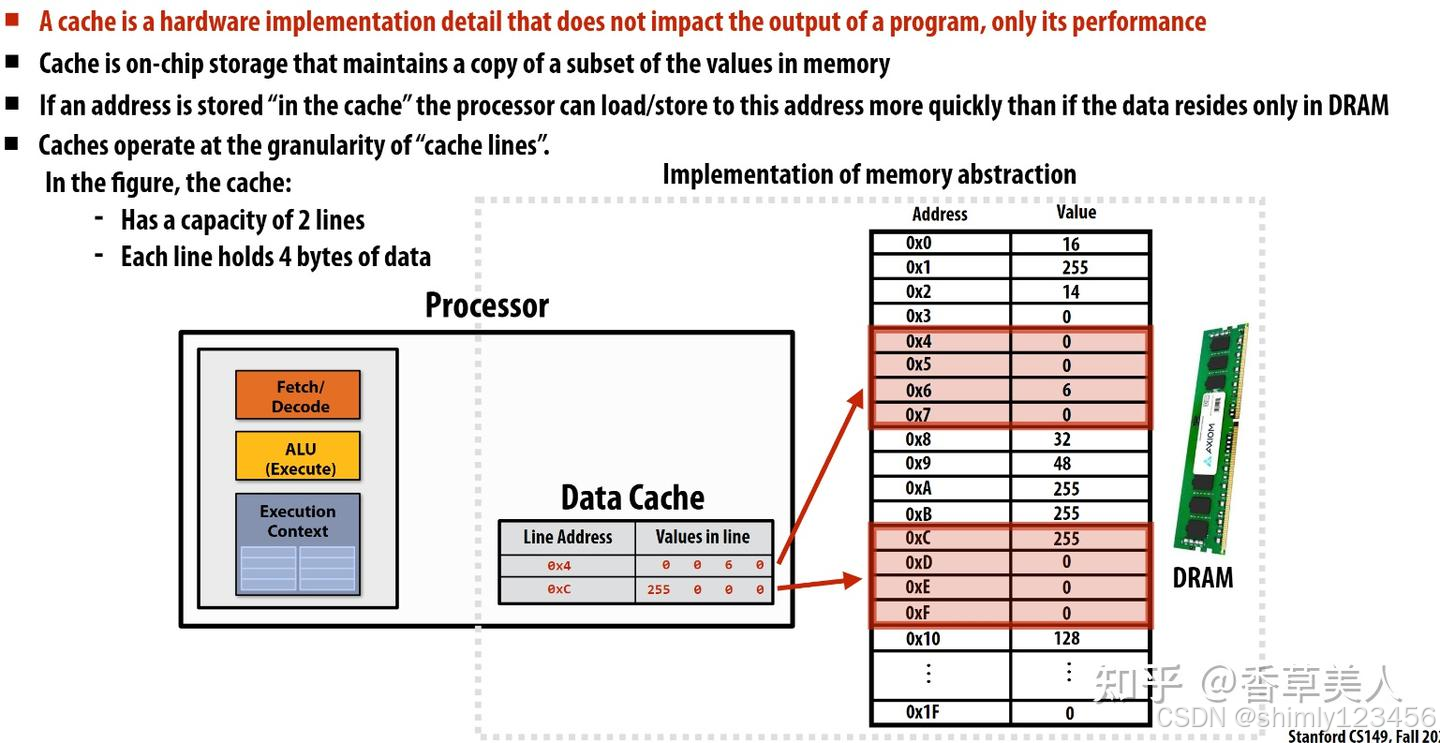

对于缓存的基本概念,学过CSAPP的同学应该对缓存有所了解, 这里就不多介绍了。 这里主要介绍以下什么是缓存行(Cache Line):

缓存行(Cache Line)是缓存系统的基本操作单位,其主要包含以下几个要点:

1.基本概念

- 是缓存中数据传输的最小单位

- 由连续的内存地址组成

- 通常大小是2的幂次字节(如32字节、64字节、128字节等)

2.组成部分 - 标记(Tag):用于标识数据来自哪个内存块

- 数据(Data):实际存储的内存数据

- 状态位:如有效位(Valid bit)、脏位(Dirty bit)等

3.示例中的缓存行特点 - Line Address | Values in line 0x4 | 0 0 6 0 0xC | 255 0 0

- 每行存储4字节数据

- 按照内存地址对齐

- 一次加载/存储整个缓存行

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?