Verilog 操作数与运算符

操作数

常数,参数,线网,变量,位选,部分选择,存储器和数组元素,函数调用

运算符

算术运算符,关系,相等,逻辑,按位,缩减,移位,条件,拼接和复制

注

注

- 相等运算符

= 赋值

== 判断是否等于

a=0101 b=1001

if(a==b) 假

if(a!= b) 真

=== 全等 0 1 x z 都会比较

- 逻辑运算符 与&& 或|| 非!

- 按位运算符

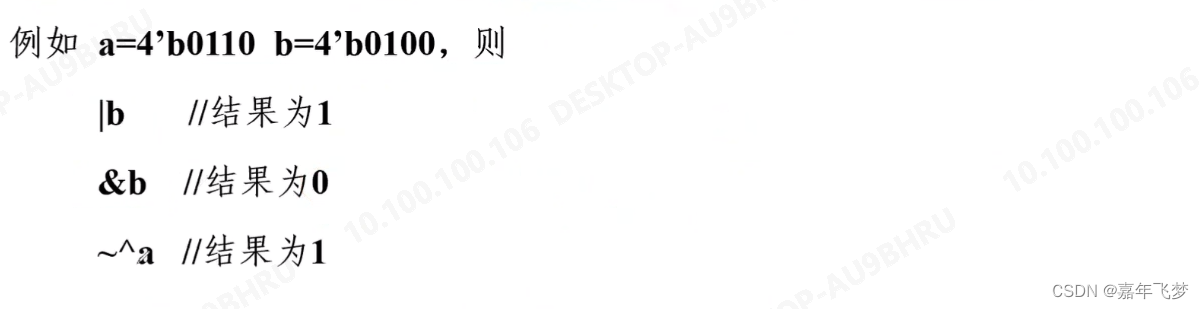

- 缩减运算符

对单一操作数上的所有位进行操作,产生1位的操作结果

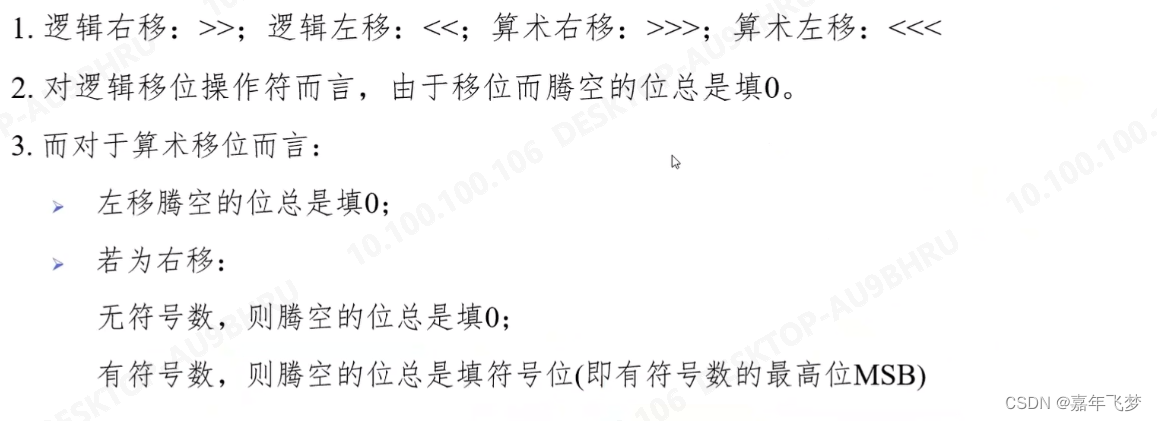

- 移位运算符

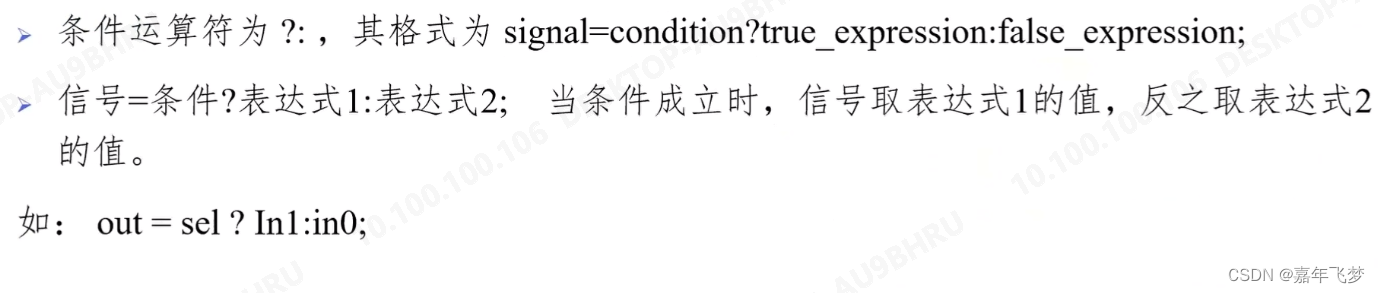

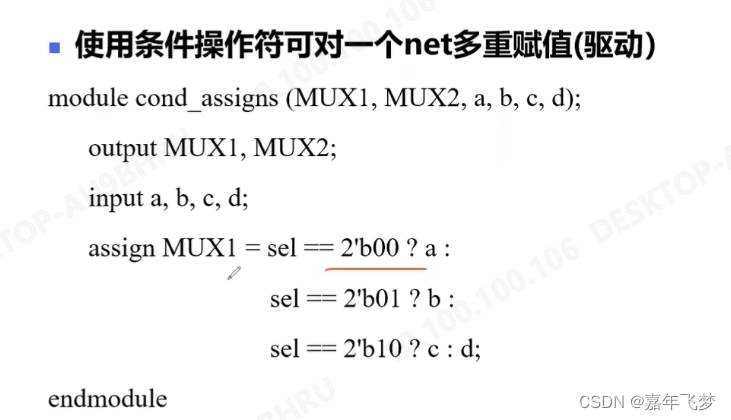

- 条件运算符

wire out

assign out=sel?in1:in0;

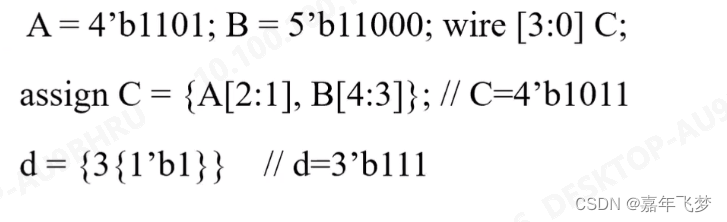

- 拼接与复制运算符

拼接{},复制{{}}

拼接运算符为将小表达式中的位拼接起来形成一个由多个位组成的大表达式;

复制运算符则通过指定重复的次数来执行

x=[127:0]

x={128{1`b1}}

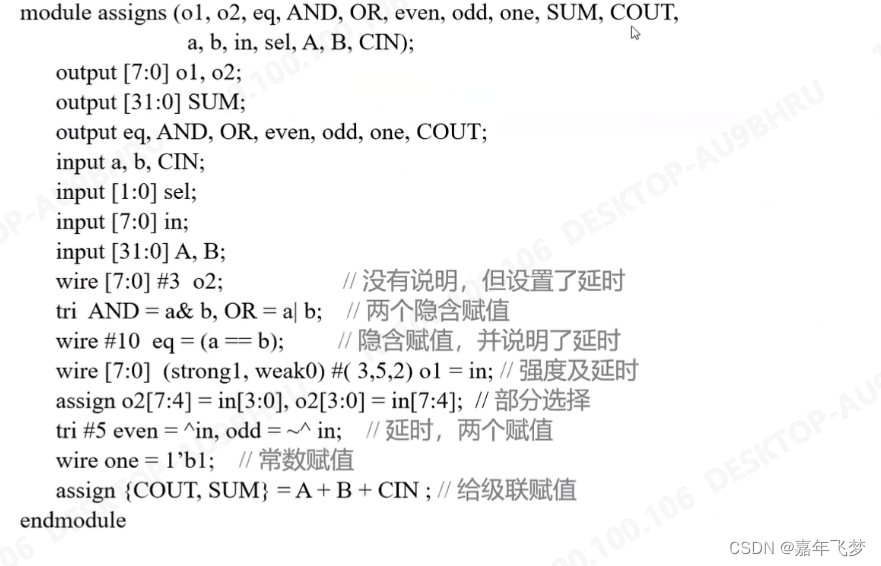

verilog连续赋值语句

- 数据流建模

根据数据在寄存器之间的流动和处理过程对电路进行描述 - 数据流描述使用连续赋值语句assign:

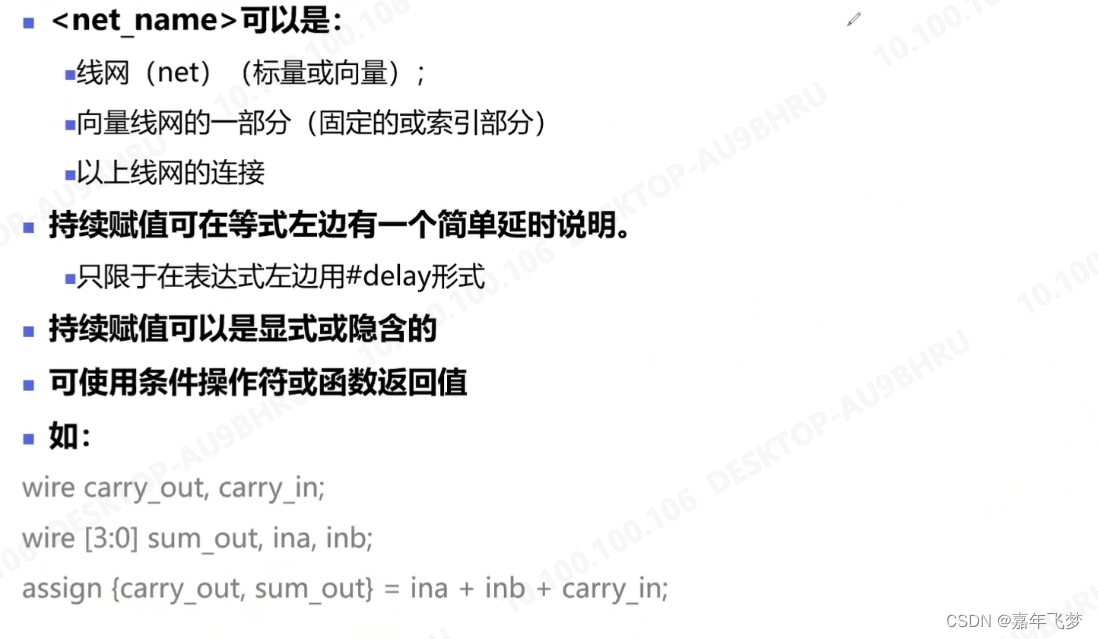

为线网型变量提供驱动的一种方法,使用表达式描述

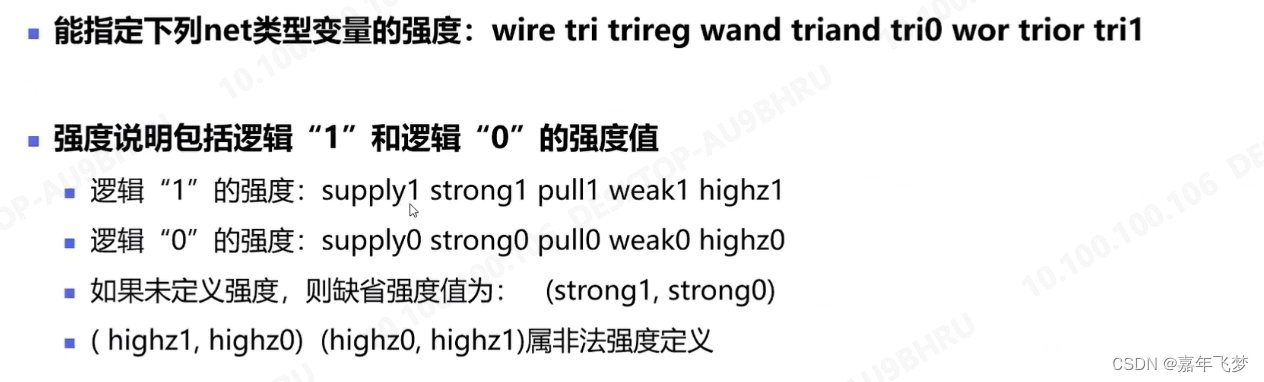

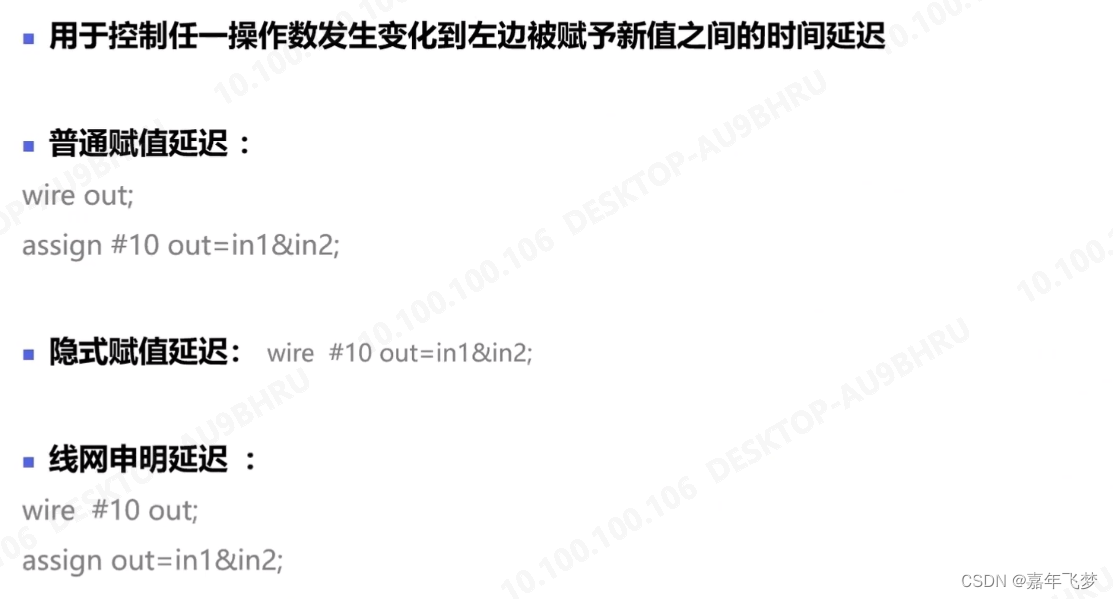

语法: [strength] [#delay] <net_name> = ;//[#delay] [strength]是可选项

注 :

assign只能用于驱动wire型变量,不能用于reg型变量

---------------------------------------------------------------------------------------------------------------------------------

---------------------------------------------------------------------------------------------------------------------------------

注 : #10 10个时间单位

Verilog操作数与运算符详解及连续赋值assign

Verilog操作数与运算符详解及连续赋值assign

本文介绍了Verilog中的操作数类型,包括常数、参数、线网、变量等,并详细讲解了各种运算符,如算术、关系、逻辑、按位等。同时,阐述了连续赋值语句`assign`在数据流建模中的应用,说明了其只能用于驱动wire型变量的特点。

本文介绍了Verilog中的操作数类型,包括常数、参数、线网、变量等,并详细讲解了各种运算符,如算术、关系、逻辑、按位等。同时,阐述了连续赋值语句`assign`在数据流建模中的应用,说明了其只能用于驱动wire型变量的特点。

748

748

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?