参数

参数化:参数用来定义时延和变量的宽度,以及状态的编码等

-

参数类型

parameter:通过例化传参,改变参数值

localparam: -

parameter

只能对参数赋值一次,使用defparam 实现

注 对于传多个参数时,如BUS_ADDR, M1 #(.BUS_WIDTH(64),.BUS_ADDR(32))U1(--------)

- localparam

局部参数,定义格式与parameter相同,localparam CODE=8`h2

在例化时,不同通过传递参数,或者defparam语句对局部参数进行修改

若局部参数是通过其它非局部参数定义的

parameter BYTE=8;

localparam NIBBLE=2*BYTE;

例1 采用参数定义的数据比较器

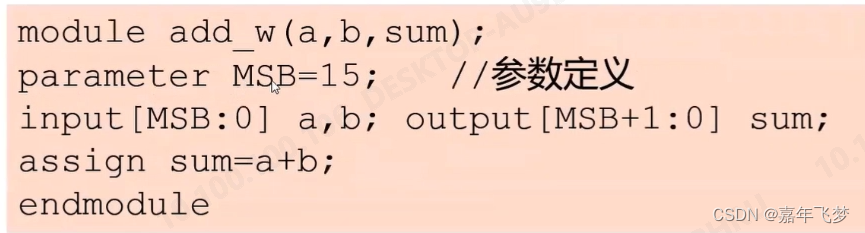

例2 采用参数定义的加法器

例3

本文介绍了Verilog中的参数化设计,包括parameter和localparam的使用。parameter用于定义时延、变量宽度和状态编码,可通过例化传参改变其值。而localparam作为局部参数,不可在例化时修改,但可用于定义复杂设计,如数据比较器和加法器等。

本文介绍了Verilog中的参数化设计,包括parameter和localparam的使用。parameter用于定义时延、变量宽度和状态编码,可通过例化传参改变其值。而localparam作为局部参数,不可在例化时修改,但可用于定义复杂设计,如数据比较器和加法器等。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1495

1495

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?