VGG16是一个典型的卷积神经网络,由13层卷积层,5层池化层和3层全连接层组成。且卷积层的计算时间在整个计算过程中占比极大,通过FPGA的并行运算可以有效的加快卷积层的计算速度。

一个卷积层可以有若干个卷积核,以第一层为例,该层对应的卷积核为64个3×3×3的卷积核,3×3是卷积核的尺寸,相当于将1个卷积核也按照RGB 分成3份(卷积核的通道数=输入图片的通道数),对其进行卷积也就是乘加运算。

以尺寸为7×7的3通道图片与2个3×3的3通道卷积核为例

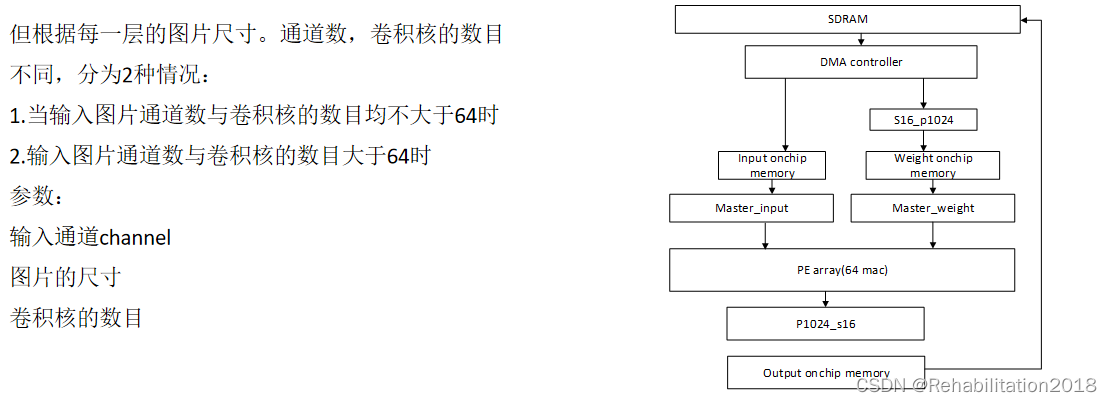

采用SoPC(ARM+FPGA),通过C语言将数据放置在片外SDRAM中,并向硬件中的卷积状态机传输地址,通道数,卷积核数等参数和一个卷积使能信号。通过FPGA来进行卷积运算。

第一层的数据在SDRAM中的排列顺序如下:

硬件架构如下图,卷积状态机conv_state控制全部的计算过程,当PE单元完成1次计算并输出后,状态机控制DMA加载数据继续计算,直至全部完成。

卷积层第一二层的计算流程图如下:

本文介绍了使用FPGA加速VGG16卷积神经网络的计算过程,通过并行运算提高卷积层效率。利用SoPC(ARM+FPGA)架构,数据存储在SDRAM中,卷积运算由FPGA硬件状态机控制,解决内存资源限制问题,通过循环输入处理大量权重数据。

本文介绍了使用FPGA加速VGG16卷积神经网络的计算过程,通过并行运算提高卷积层效率。利用SoPC(ARM+FPGA)架构,数据存储在SDRAM中,卷积运算由FPGA硬件状态机控制,解决内存资源限制问题,通过循环输入处理大量权重数据。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3955

3955

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?