DE1-SoC HPS CAN通信(中断方式)调试

实验目的:

利用Altera Cyclone V SoPC HPS集成的CAN总线控制器,采用中断方式,实现裸机下的CAN报文数据的收发。

实验环境:

硬件:DE1-SoC开发板,

软件:Quartus II 15.0和DS-5 18.1,Preloader,HPS裸机固件驱动库(18.1)。

实验流程:

1.硬件设计

2.软件设计

a. Preloader部分

b. HPS引导流程

c. CAN裸机中断收发程序流程

1. 主程序框架

2. 关键硬件资源的初始化

3. 中断收发服务函数实现及触发流程

1.硬件设计

HPS 中包含CAN 总线控制器,所以不需要添加 IP 核,只需从 HPS 中引出 CAN 的 tx、rx 的引脚,使其能够通过这两个引脚连接片外驱动电路并和外部进行通信。

具体步骤:

在 Qsys 系统组件 HPS 参数选项标签页设置 CAN 的外设引脚

注:CAN pin选择FPGA ,因为 HPS I/O Set 没有可以连接外部进行 CAN 通信的引脚

双击红色区域引出 CAN 的引脚

用 verilog 进行端口声明:

经过综合与分析后,在 Pin Planner 中就会看到上面声明的 CAN 端口

双击 Location进行引脚分配:

分配的引脚是从板上2个40pin GPIO中随意挑选的,但需要注意的是,由于 CAN 通信是差分信号输入到 CAN 总线上,所以挑选引脚复用时要选择 DIFFIO_RX DIFFIO_TX

电路连接如下:

需要注意的是,需要加一个电平转换器件,因为 TTL 电平标准和 CAN 的电平标准不同。

最终编译生成的.sof文件经由USB-Blaster下载到开发板中。

3.软件设计

硬件部分设计完成,但HPS 的配置信息还不知道,软件程序运行的环境没准备好,裸机程序还需加载,所以需要准备一个完成软硬件交互的文件,也就是preloader部分。

a.Preloader部分

最终需要生成 u-boot-spl 二进制文件进行相关硬件初始化,并且引导加载裸机程序

那么怎么得到u-boot-spl ?

首先,我们需要知道配置 HPS 的信息,如使能的外设,管脚的复用等

对此,可以编译上面说明的硬件设计,得到.sof文件(经由USB Blaster下载到板子中)和handoff文件夹,handoff文件夹中包含了这些信息

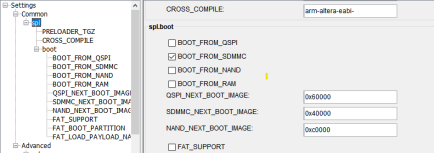

然后,经由 preloader 生成器,也就是bsp(板级支持包) editor 将 handoff 文件夹里的信息转换成源代码、 另外生成 preloader 设置文件、 preloader 调试脚本以及编译 preloader 所用的 makefile。

由此我们得到了源文件,但是和我们最终想要的二进制文件存在差异,需要借助 makefile进行编译。

Bsp editor支持多种型号板子的 preloader 配置信息的生成

generated文件夹可以看到许多头文件与C语言文件,这些文件是用来更新uboot中相关文件的,主要涉及到系统配置,IO复用,DDR初始化等

Makefile 制定了编译规则,生成最终的二进制文件,执行以下步骤:

1.把 generated文件夹下的相应文件拷贝到uboot-socfpga/board/altera/socfpga与下面sdram子目录

2.通过下面的变量设置

PRELOADER_UPDATE_DIR := $(PRELOADER_SRC_DIR)/board/altera/socfpga

SOCFPGA_BOARD_CONFIG := socfpga_$(DEVICE_FAMILY)_config

DEVICE_FAMILY := cyclone5

以及执行make $(board)_config 对工程进行配置,以确定特定于目标板的各个子目录和头文件。生成配置文件config.h(知道取用U-Boot源代码中的哪些相应文件)

3.配置完成后,就要进行编译 spl 得到 u-boot-spl.bin

uboot-socfpga目录下顶层文件Makefile有下面的语句

ALL-$(CONFIG_SPL) += $(obj)spl/u-boot-spl.bin

打开spl目录下的文件Makefile

在这里我们可以看到编译 spl 所需要用的各种配置文件、汇编文件和用到的链接器文件,下面是其中的一部分

LIBS-$(CONFIG_SPL_FRAMEWORK) += common/spl/libspl.o

LIBS-$(CONFIG_SPL_LIBCOMMON_SUPPORT) += common/libcommon.o

LIBS-$(CONFIG_SPL_LIBDISK_SUPPORT) += disk/libdisk.o

LIBS-$(CONFIG_SPL_I2C_SUPPORT) += drivers/i2c/libi2c.o

LIBS-$(CONFIG_SPL_GPIO_SUPPORT) += drivers/gpio/libgpio.o

LIBS-$(CONFIG_SPL_MMC_SUPPORT) += drivers/mmc/libmmc.o

LDSCRIPT := $(TOPDIR)/board/$(BOARDDIR)/u-boot-spl.lds

链接文件决定一个可执行程序的各个段的存储(加载)地址,以及运行(链接)地址。

b.HPS引导流程

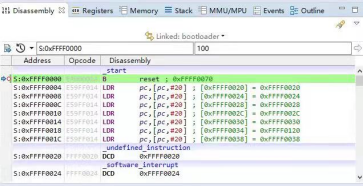

上电 reset 后,位于 HPS 中的 ROM 运行封装好的一段代码Boot ROM

Boot ROM代码的作用是确定所选的boot源,重置后初始化HPS,将 preloader 映像从 flash 加载到OCRAM然后跳转到 preloader 。

所选的 Flash 类型 SDMMC 在 bsp-editor spl boot 选项中设置

OCRAM 由地址 0xFFFF0000知

Preloader 在完成Clock Reconfiguration、初始化SDRAM接口、配置HPS I/O引脚及复用、初始化加载下一阶段程序的接口后,将裸机程序引导映像从引导设备复制到SDRAM。并执行

SDRAM 地址0x0010

本文详细介绍了如何在DE1-SoC开发板上使用Altera Cyclone V SoPC的HPS集成CAN控制器进行中断方式的CAN通信调试。实验涉及硬件设计,包括端口分配和电平转换,以及软件设计,涵盖Preloader部分、HPS引导流程和CAN裸机中断收发程序。在软件设计中,通过Preloader初始化硬件,引导裸机程序,并配置中断服务函数来处理CAN数据的收发。

本文详细介绍了如何在DE1-SoC开发板上使用Altera Cyclone V SoPC的HPS集成CAN控制器进行中断方式的CAN通信调试。实验涉及硬件设计,包括端口分配和电平转换,以及软件设计,涵盖Preloader部分、HPS引导流程和CAN裸机中断收发程序。在软件设计中,通过Preloader初始化硬件,引导裸机程序,并配置中断服务函数来处理CAN数据的收发。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1502

1502

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?