layout: post

title: “基础(寄存器-栈-中断向量表)”

date: 2024-1-16 15:39:08 +0800

tags: Cotex-M3

基础(寄存器-栈-中断向量表)

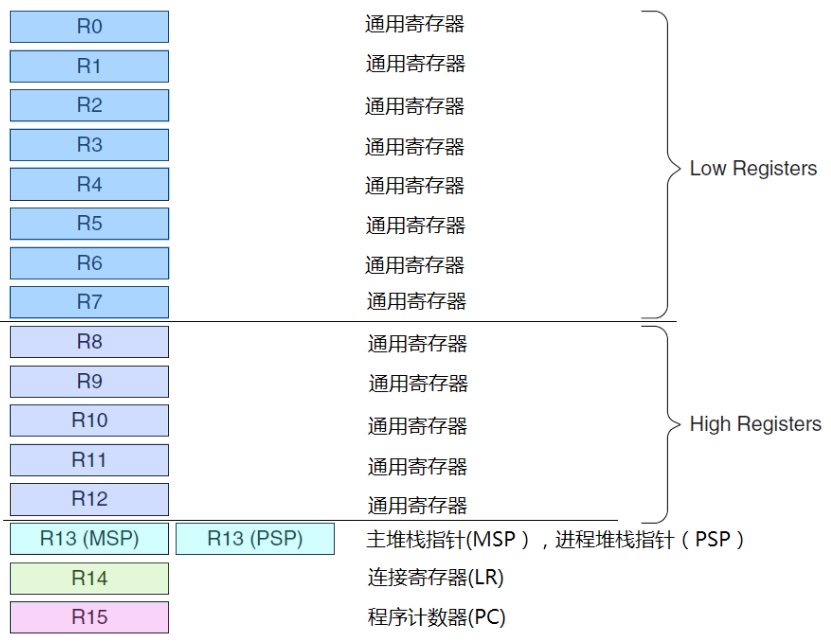

寄存器

普通寄存器

R0 -R7也被称为低组寄存器。所有指令都能访问它们。它们的字长全是32位,复位后的初始值是不可预料的

R8 -R12也被称为高组寄存器。这是因为只有很少的16位Thumb指令能访问它们,32位的thumb-2指令则不受限制。它们也是32位字长,且复位后的初始值是不可预料的。

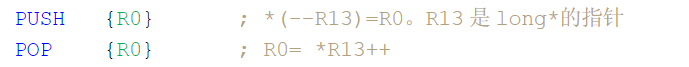

当引用R13(或写作SP)时,引用到的是当前正在使用的那一个,另一个必须用特殊的指令来访问(MRS,MSR指令)

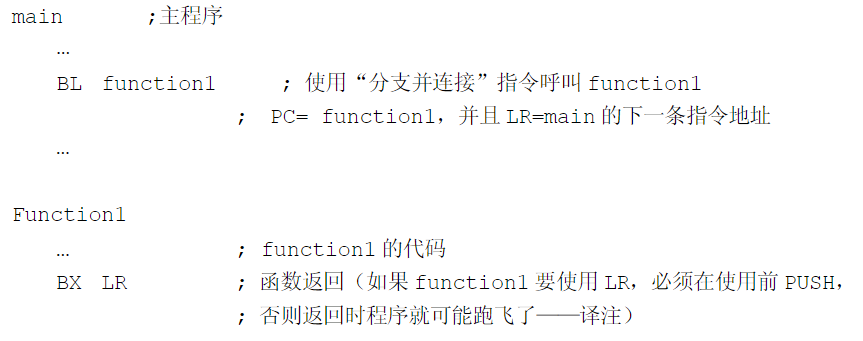

R14是连接寄存器(LR)。在一个汇编程序中,你可以把它写作both LR和R14。LR用于在调用子程序时存储返回地址。例如,当你在使用BL(分支并连接,Branch and Link)指令时,就自动填充LR的值。

LR的LSB却是可读可写的。这是历史遗留的产物。在以前,由位0来指示ARM/Thumb状态。因为其它有些ARM处理器支持ARM和Thumb状态并存,为了方便汇编程序移植,CM3需要允许LSB可读可写

R15是程序计数器,在汇编代码中一般我们都都叫它的外号“PC”。 因为CM3内部使用了指令流水线,读PC时返回的值是当前指令的地址+4

CM3中的指令至少是半字对齐的,所以PC的LSB总是读回0。然而,在分支时,无论是直接写PC的值还是使用分支指令,都必须保证加载到PC的数值是奇数(即LSB=1),用以表明这是在

本文详细介绍了Cortex-M3处理器中的寄存器结构(包括普通寄存器如R0-R15和特殊寄存器如PSR),栈的使用和管理,中断向量表的作用,以及栈操作和复位时的特殊处理,特别是针对双栈机制和中断处理的讨论。

本文详细介绍了Cortex-M3处理器中的寄存器结构(包括普通寄存器如R0-R15和特殊寄存器如PSR),栈的使用和管理,中断向量表的作用,以及栈操作和复位时的特殊处理,特别是针对双栈机制和中断处理的讨论。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2196

2196

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?