一、

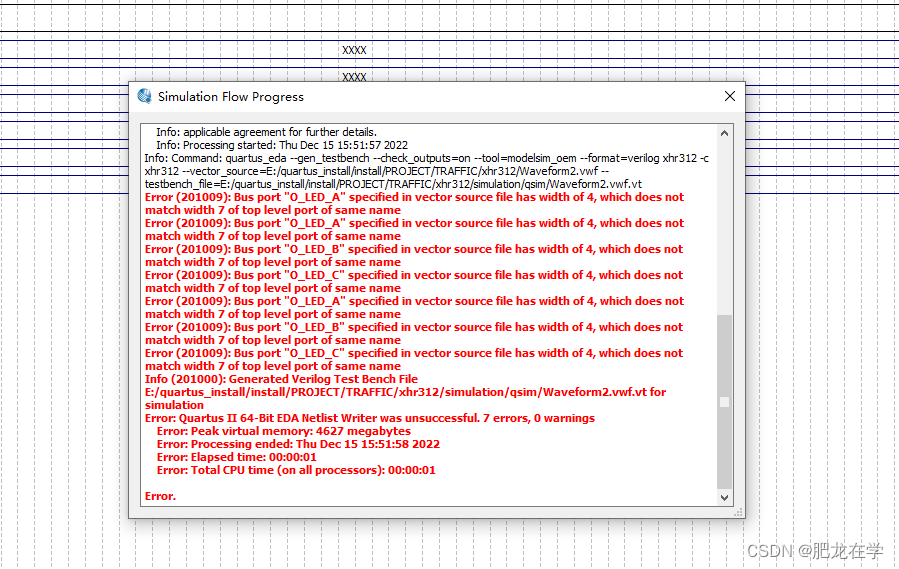

错误:

Error (201009): Bus port "O_LED_A" specified in vector source file has width of 4, which does not match width 7 of top level port of same name

Error (201009): Bus port "O_LED_A" specified in vector source file has width of 4, which does not match width 7 of top level port of same name

Error (201009): Bus port "O_LED_B" specified in vector source file has width of 4, which does not match width 7 of top level port of same name

Error (201009): Bus port "O_LED_C" specified in vector source file has width of 4, which does not match width 7 of top level port of same name

Error (201009): Bus port "O_LED_A" specified in vector source file has width of 4, which does not match width 7 of top level port of same name

Error (201009): Bus port "O_LED_B" specified in vector source file has width of 4, which does not match width 7 of top level port of same name

Error (201009): Bus port "O_LED_C" specified in vector source file has width of 4, which does not match width 7 of top level port of same name

Info (201000): Generated Verilog Test Bench File E:/quartus_install/install/PROJECT/TRAFFIC/xhr312/simulation/qsim/Waveform2.vwf.vt for simulation

Error: Quartus II 64-Bit EDA Netlist Writer was unsuccessful. 7 errors, 0 warnings

Error: Peak virtual memory: 4627 megabytes

Error: Processing ended: Thu Dec 15 15:51:58 2022

Error: Elapsed time: 00:00:01

Error: Total CPU time (on all processors): 00:00:01

Error.

原因:

这是一个子模块的仿真,子模块中输出的O_LED_A位宽是4位,顶层中也输出的有一个O_LED_A位宽是7位,分配管脚是时候是对7位分配的。在对子模块进行仿真的时候,因为名称相同,位宽不同,所以分配管脚中还是7位,导致出现了这个错误!

SOLUTION:

就算把顶层模块代码删掉,由于管脚分配仍然存在,所以还是会报错。唯二的方法就是更换子模块输出端口名称,另一个就是把引脚分配全部删除掉。

本文解决了一个常见的Quartus II错误,即子模块与顶层模块间信号宽度不一致的问题。出现该错误是因为子模块输出信号的位宽与顶层模块中相应信号的位宽不符。解决方法包括更改子模块输出端口名称或删除引脚分配。

本文解决了一个常见的Quartus II错误,即子模块与顶层模块间信号宽度不一致的问题。出现该错误是因为子模块输出信号的位宽与顶层模块中相应信号的位宽不符。解决方法包括更改子模块输出端口名称或删除引脚分配。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?