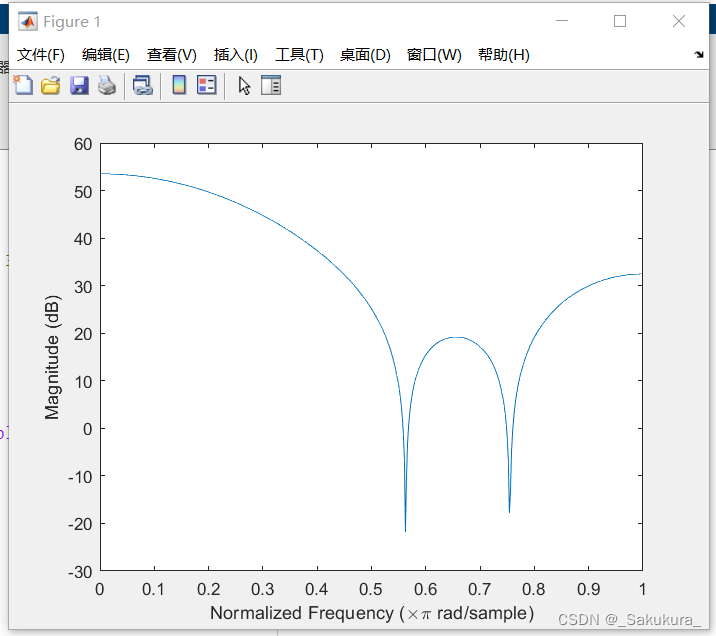

1.fir转置滤波器

1.1问题

使用系数5,12,60,96,128,96,60,12,5实现转置滤波器,使用逻辑单元,不使用乘法器

1.2思路

使用<<、>>左移右移逻辑运算实现恒定系数乘法。

关于转置滤波器,这里就不贴图了。

1.3问题代码及仿真

1.3.1转置fir滤波器模块

module trans_fir#(

parameter WIDTH = 'd8

)(

input clk,

input rstn,

input signed [WIDTH+7:0] x,

output signed [WIDTH+18:0] y

);

//parameter h0 = 5,h1=12,h2=60,h3=96,h4=128,h5=96,h6=60,h7=12,h8=5;

wire signed [WIDTH+18:0] b[8:0];

wire signed [WIDTH+18:0] c[16:0];

integer i;

assign c[0]=x<<2;

assign c[1]=x;

assign c[2]=x<<3;

assign c[3]=x<<2;

assign c[4]=x<<6;

assign c[5]=x<<2;

assign c[6]=x<<6;

assign c[7]=x<<5;

assign c[8]=x<<7;

assign c[9]=x<<6;

assign c[10]=x<<5;

assign c[11]=x<<6;

assign c[12]=x<<2;

assign c[13]=x<<3;

assign c[14]=x<<2;

assign c[15]=x<<2;

assign c[16]=x;

assign b[0]=c[0]+c[1];

assign b[1]=c[2]+c[3];

assign b[2]=c[4]-c[5];

assign b[3]=c[6]+c[7];

assign b[4]=c[8];

assign b[5]=c[9]+c[10];

assign b[6]=c[11]-c[12];

assign b[7]=c[13]+c[14];

assign b[8]=c[15]+c[16];

reg signed [WIDTH+18:0] d[8:0];

always @(posedge clk,negedge rstn) begin

if(!rstn)begin

for (i = 0;i<9 ;i=i+1 ) begin

d[i]<='d0;

end

end

else begin

for (i = 0;i<8 ;i=i+1 ) begin

d[i]<=b[i]+d[i+1];

end

d[8]<=b[8];

end

end

assign y=b[0];

endmodule

1.3.2Testbench

这里是用了rom的ip核存储了一个正弦信号。

module tb_trans_fir(

);

parameter WIDTH = 'd8;

reg clk;

reg rstn;

wire signed [WIDTH+7:0] x;

wire signed [WIDTH+18:0] y;

reg [11:0] addr;

initial begin

clk=1'b0;

rstn=1'b0;

#5

rstn<=1'b1;

end

always #10 clk=~clk;

trans_fir #(

.WIDTH(WIDTH)

)u_fir(

.clk(clk),

.rstn(rstn),

.x(x),

.y(y)

);

blk_mem_gen_0 u_rom(

.clka(clk),

.addra(addr),

.douta(x)

);

always @(posedge clk,negedge rstn) begin

if(!rstn)begin

addr<='d0;

end

else begin

addr<=addr+1'b1;

end

end

endmodule

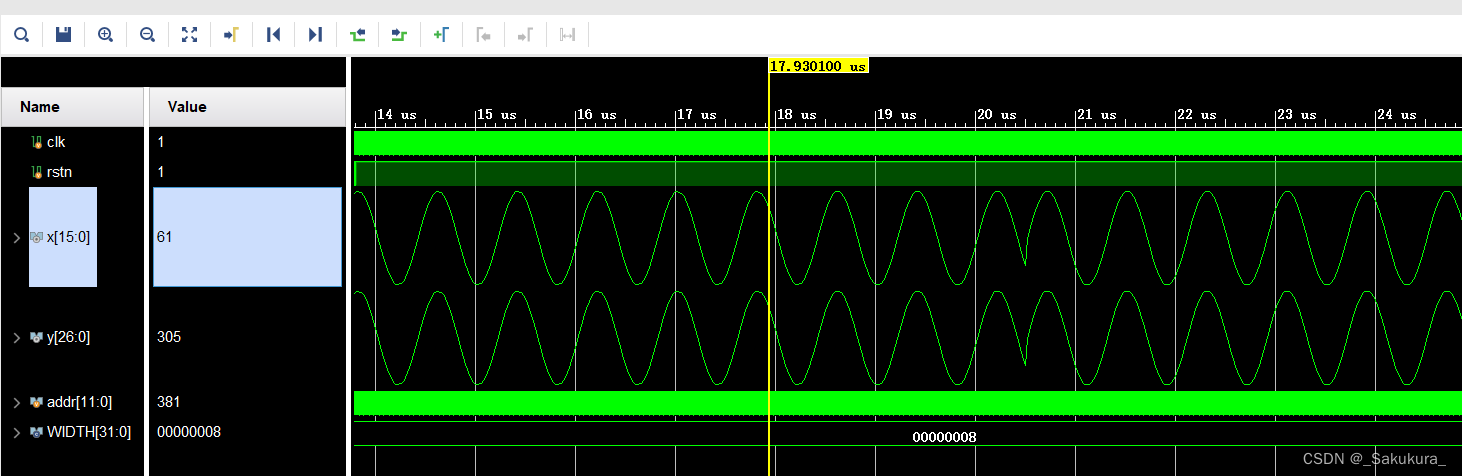

1.3.3vivado仿真图

1.5总结

猜测应该是移位和加法运算无法在同一个周期完成,且扩展和移位不要放在一起

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?