存储容量的扩展(若存储芯片连在一起组成足够容量的存储器)

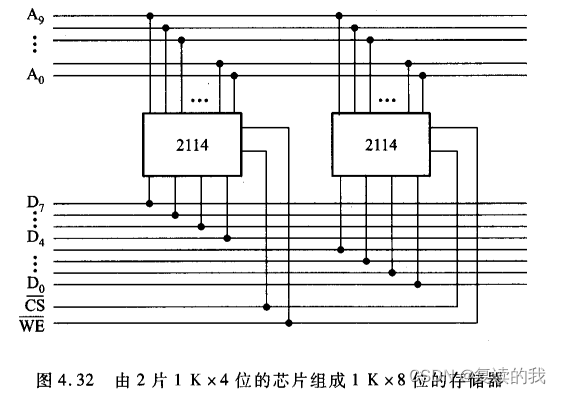

位扩展:指增加存储字长

一片数据线作为高4位、另一片线作为低4位

地址线、CS、WE都分别连在一起

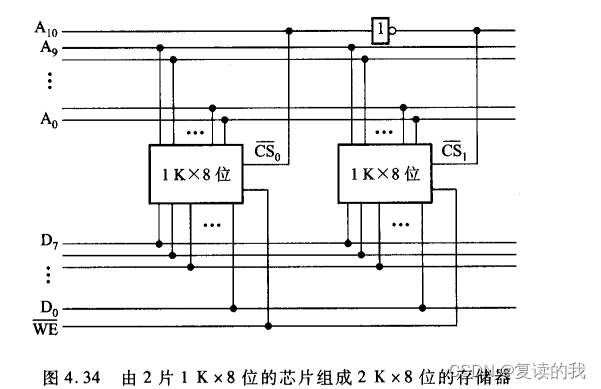

字扩展:指增加存储器字的数量

将A10用作片选信号,通过片选进行选择

字位扩展

存储器与CPU连接

存储芯片与CPU芯片相连时,注意片与片之间地址线、数据线和控制线的连接

地址线连接

CPU地址线数比存储芯片地址线数多

CPU地址线的低位与存储芯片的地址线相连,CPU地址线高位用于存储扩充或其他用途(片选信号等)

数据线连接

CPU数据线数与存储芯片的数据线数也不一定相等,必须对存储芯片扩位,使其数据线数与CPU数据线数相等

读写命令线连接

CPU读写命令线一般可直接与存储芯片读写控制端相连(高电平为读,低电平为写)有些CPU读写线是分开的

CPU读命令线与存储芯片允许读控制端相连

CPU写命令线与存储芯片允许写控制端相连

片选线连接

片选线连接是CPU与存储芯片正确工作的关键

片选有效信号与CPU的访存控制信号MREQ(低电平有效)有关

片选有效信号还和地址有关,因为CPU的地址线往往多于存储芯片的地址线,那些未与存储芯片连上的高位地址必须和访存控制信号共同产生存储芯片的片选信号

合理选择存储芯片

合理选择存储芯片主要指存储芯片类型和数量选择

通常选用ROM存放系统程序、标准子程序和各类常数等

提高访存速度措施

除了寻找高速元件和采用层次结构外,调整主存的结构也可以提高访存速度

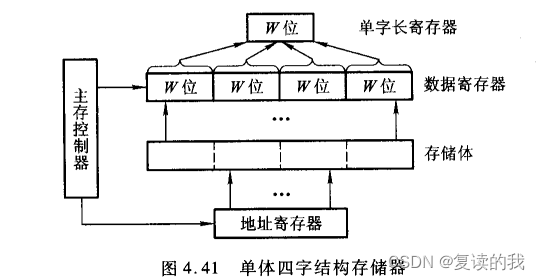

1.单体多字系统

由于程序和数据在存储体内是连续存放的,因此CPU访存取出的信息也是连续的

单体字结构的存储器

按地址在一个存取周期内可读出4*W位的指令或数据,使主存带宽提高

前提:指令和数据在主存内必须连续存放,一旦遇到转移指令,或者操作数不能连续存放,这种方法效果不明显

2.多体并行系统

采用多体模块组成存储器。每个模块有相同容量和存取速度,各模块有独立的组件,他们能并行工作也能交叉工作

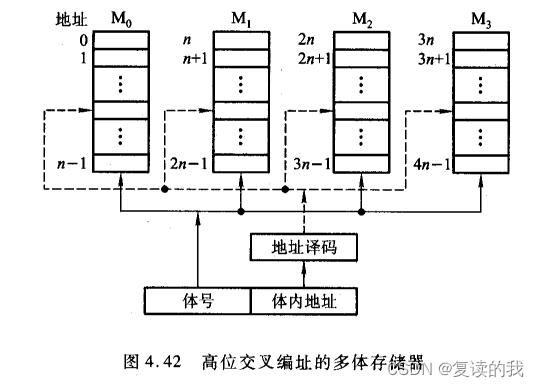

高位交叉编址:高位地址表示体号,低位地址为体内地址

程序按体内地址顺序存放,按这种编制方式,只要合理调动,使不同的请求源同时访问不同的体,便可实现并行工作

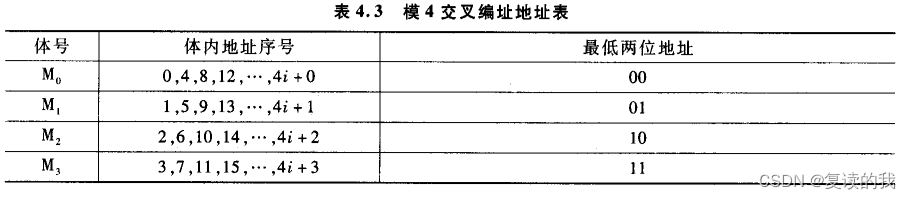

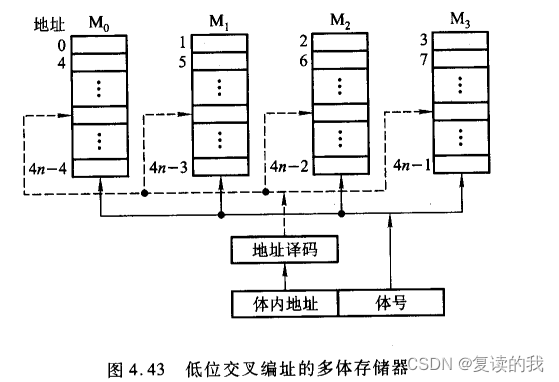

低位交叉编制:低地址表示体号,高位地址为体内地址 又称模M编制(M等于模块数)

一般模块数M取2的方幂 有的为减少存储器冲突,采用质数个模块

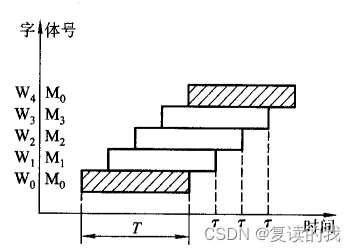

多体模块结构的存储器采用交叉编址后,可以在不改变每个模块存取周期的前提下,提高存储器带宽

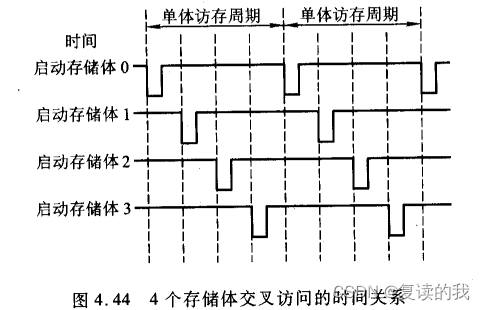

CPU交叉访问4个存储体的时间关系,负脉冲为启动每个体的工作信号

虽然对每个体而言,存取周期没有缩短,但由于CPU交叉访问各体,最终在一个存取周期内,存储器实际上向CPU提供了4个存储字

模块数为n,存取周期为T,总线传输周期为t

对于低位交叉存储器所需总时间Tz

Tz=T+(n-1)t

对于高位交叉编制

Tz=nT

多模块存储器不仅要与CPU交换信息,还要与辅存、I/O设备,I/O处理机交换信息

存储器控制部件(存控):决定与哪个部件交换信息

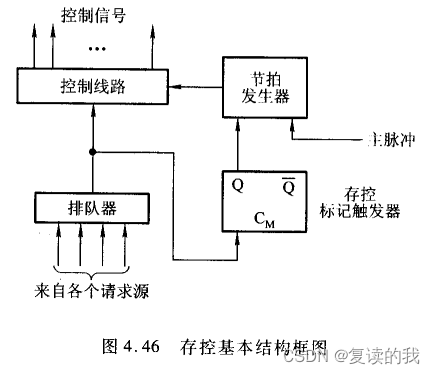

存控由排队器、控制线路、节拍发生器及标记触发器组成

排队器

由于访存的请求源很多,并且访问是随机的。为了防止请求源同时占有同一存储体或其他错误产生,有它来确定请求源的优先级

存控标记触发器Cm

它来接受排队器的输出信号,一旦响应某请求源的请求,Cm被置1,启动节拍发生器工作

节拍发生器

产生固定节拍,与机器主脉冲同步,使控制线路按一定时序发出信号

控制线路

它将排队器给出信号与节拍发生器提供的节拍信号配合,向存储器各部件发出各种控制信号

文章探讨了存储容量的位扩展和字扩展技术,以及如何通过优化存储芯片与CPU的连接,如使用多体并行系统和交叉编址,来提高存储器的访问速度。同时提及了存储器控制部件在数据交换中的作用,特别是排队器、标记触发器和节拍发生器在管理随机访问请求和确保数据流畅中的关键角色。

文章探讨了存储容量的位扩展和字扩展技术,以及如何通过优化存储芯片与CPU的连接,如使用多体并行系统和交叉编址,来提高存储器的访问速度。同时提及了存储器控制部件在数据交换中的作用,特别是排队器、标记触发器和节拍发生器在管理随机访问请求和确保数据流畅中的关键角色。

4398

4398

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?