1. 计算机概述

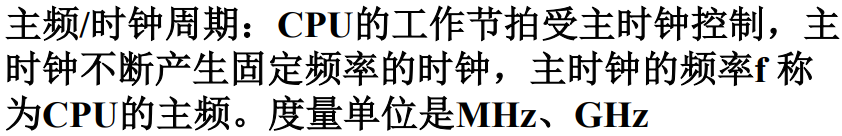

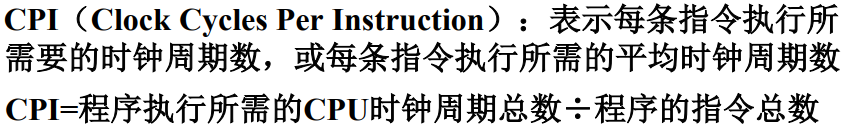

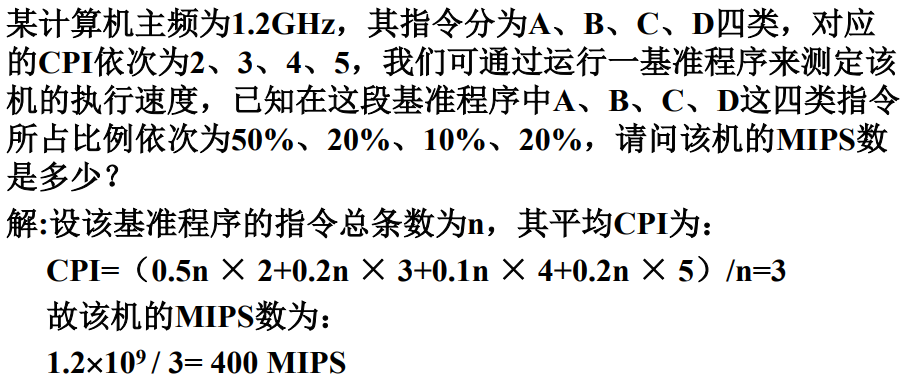

1.1 计算机的性能指标

1Ghz = 10^9 Hz

例1

2. 运算方法与运算器

2.1 补码的算术移位

左移补0,右移补符号位

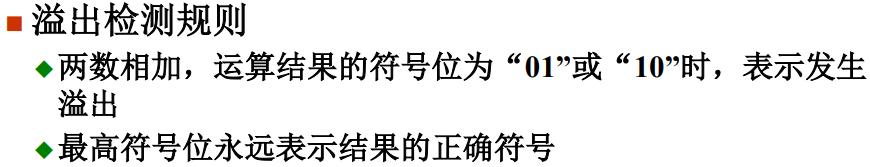

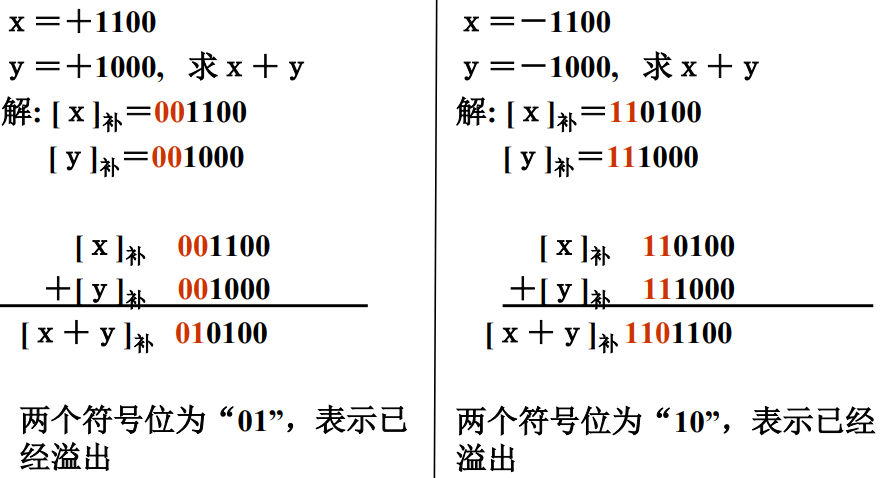

2.2 变形补码(双符号位)

例2.

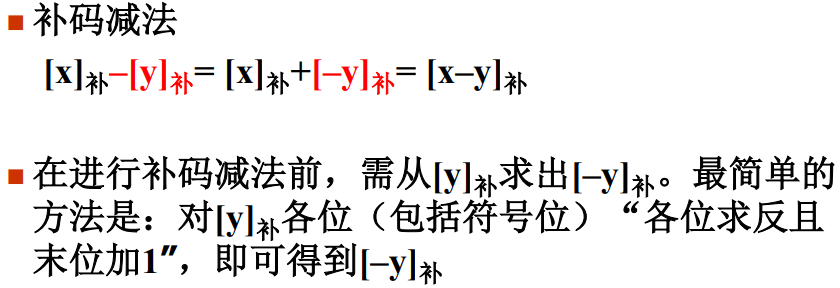

2.3 补码减法

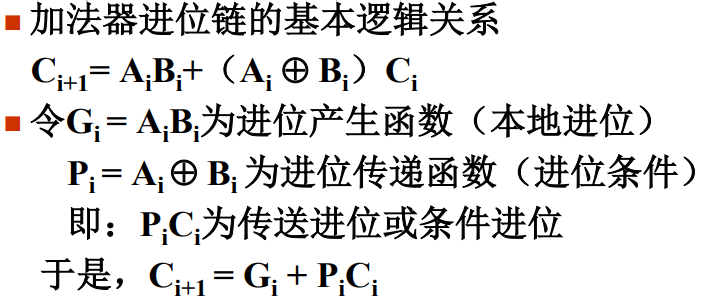

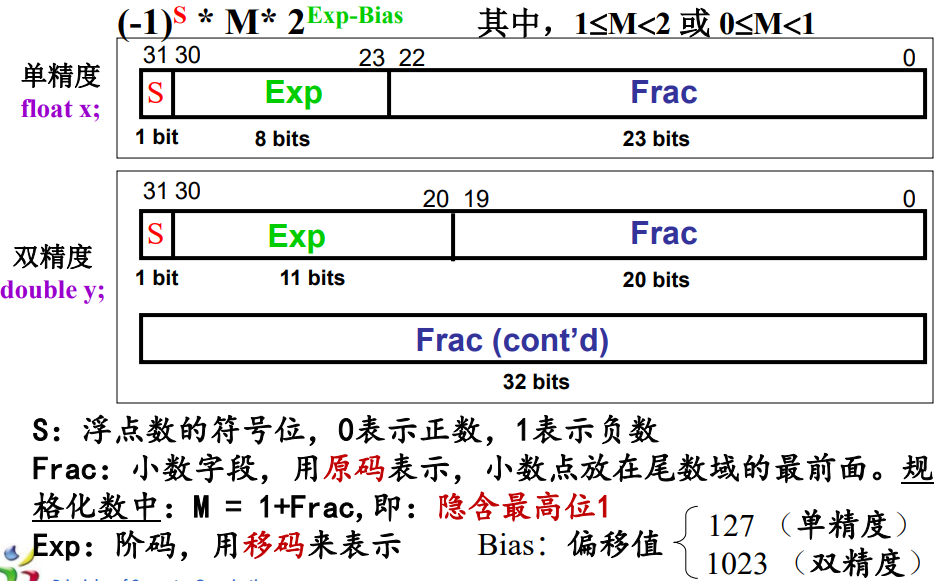

2.4 加法器进位链

串行进位

并行进位

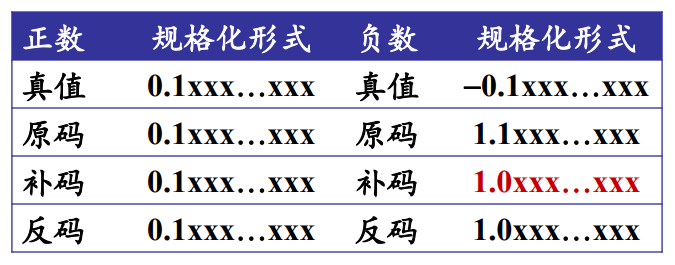

2.5 浮点数

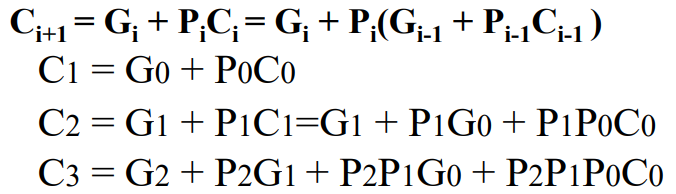

规格化数

对于原码而言,其规格化数的最高位一定是1

对于补码而言,其规格化数的最高位一定与符号位相反

IEEE754浮点数标准

3. 存储系统

3.1 RAM

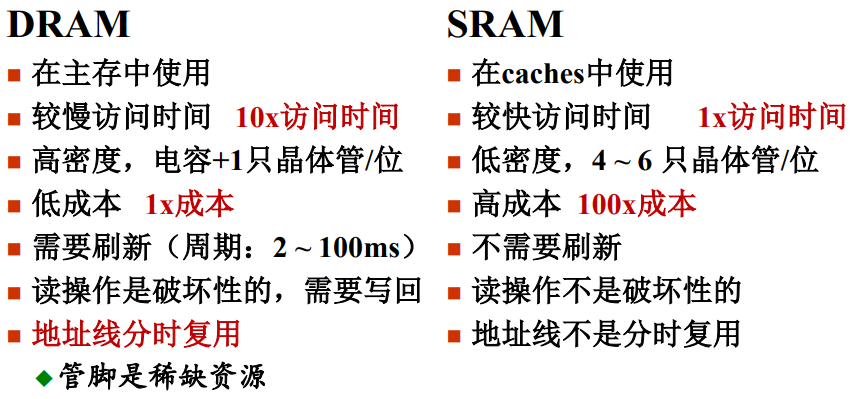

RAM:随机存取存储器,分为静态存储器(SRAM)和动态存储器(DRAM)

SRAM vs DRAM

SRAM的存储容量不如DRAM

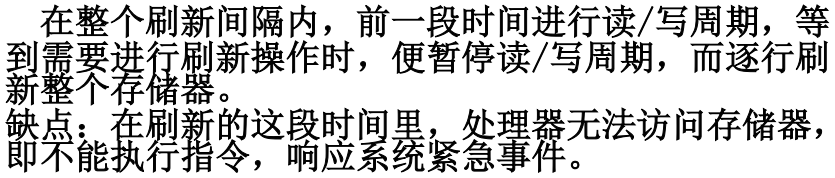

集中式刷新

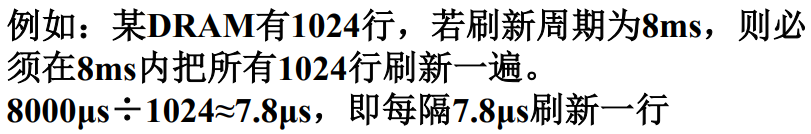

分散式刷新

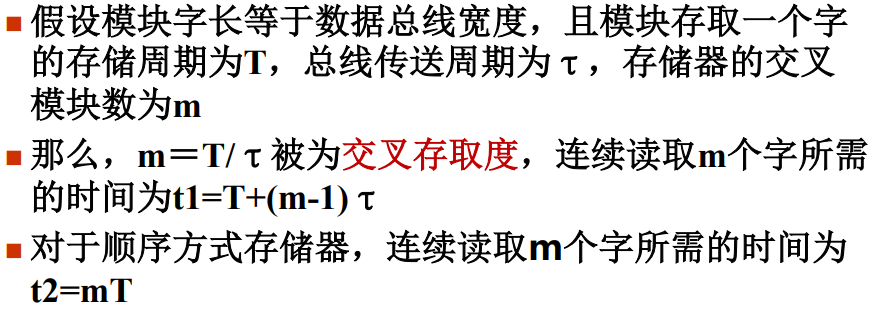

3.2 交叉存储器

3.3 主存与Cache的地址映射

全相联映射

优点:存储空间利用率高、命中率较高

缺点:需要CAM存储器,线路复杂,成本高

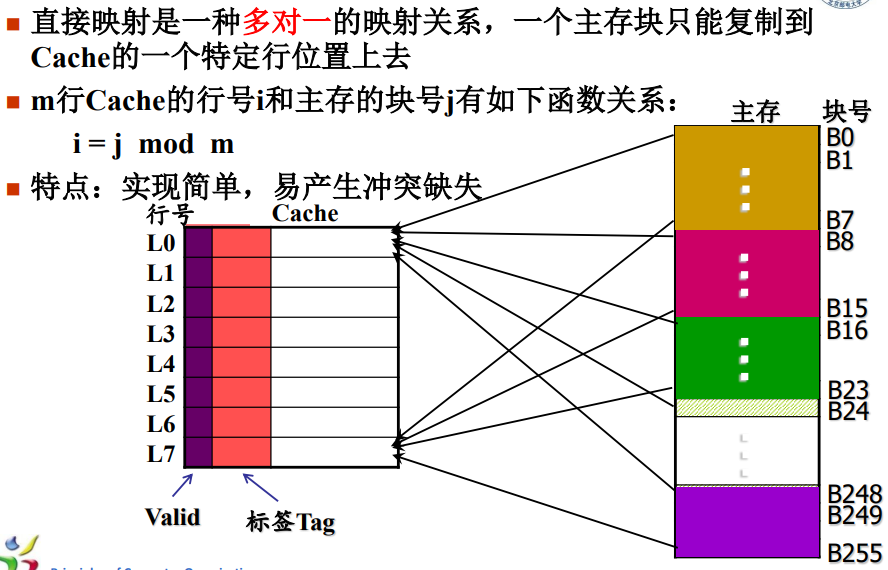

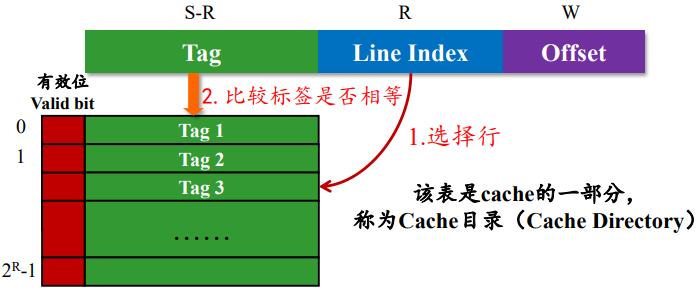

直接映射

特点:实现简单,易产生冲突缺失

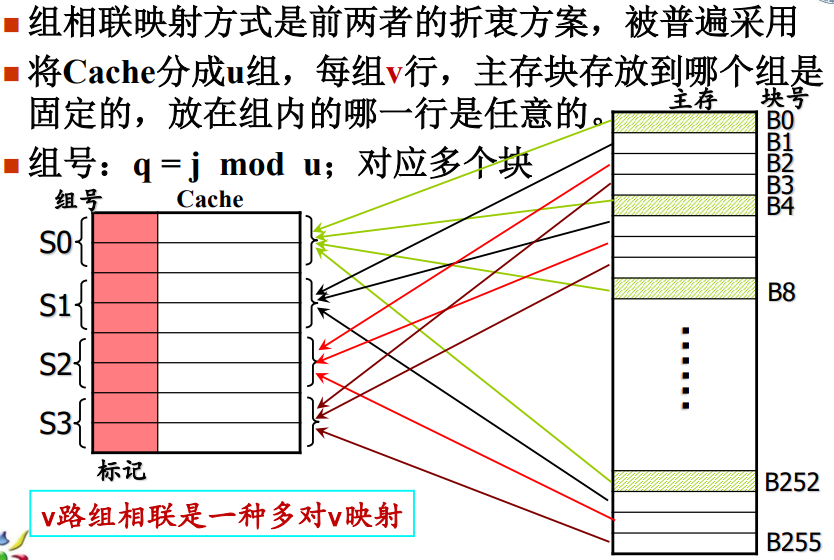

v路组相联映射

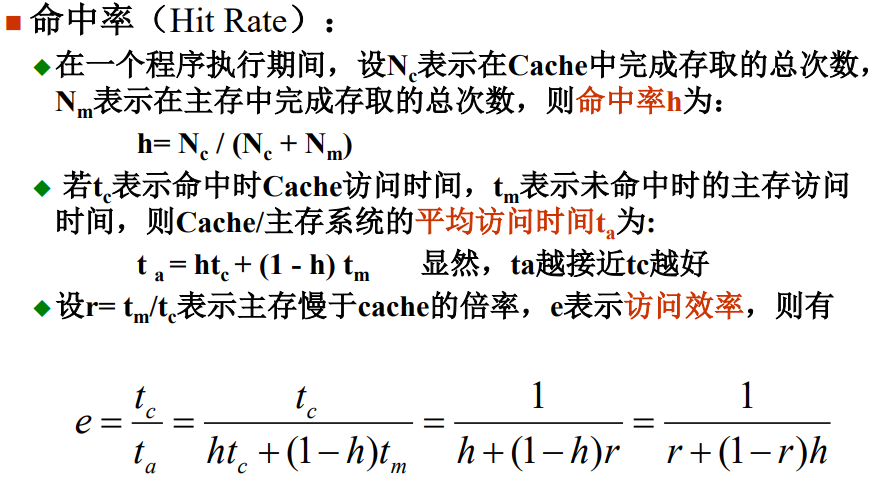

3.4 Cache的性能指标

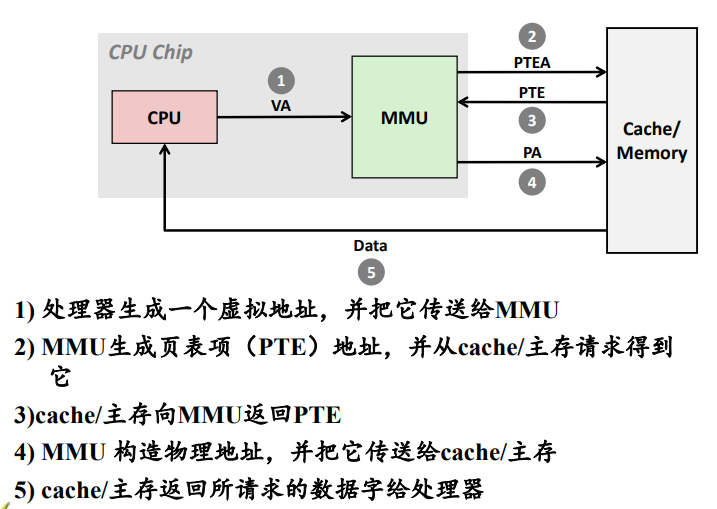

3.5 虚拟存储器

虚拟地址被分为:虚拟页号 和 页内地址

页式虚拟存储器

页表大小:页表中表项的数量 == 虚拟地址空间中页的数量

页面命中

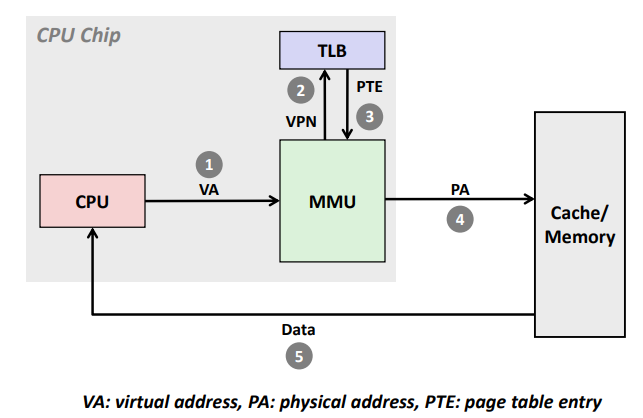

快表TLB

TLB命中

4. 指令系统

4.1 操作数寻址方式

立即寻址:指令的地址字段指出的不是操作数的地址,而是操作数本身

直接寻址:在指令的地址字段中直接指出操作数在内存的地址

间接寻址:指令的地址字段中的形式地址不是操作数的真正地址,而是操作数地址的地址

相对寻址:把程序计数器PC的内容加上指令格式中的偏移量(有符号数)而形成操作数的有效地址

基址寻址:将CPU中基址寄存器的内容加上指令格式中的偏移量得到的操作数有效地址

变址寻址:将CPU中变址寄存器的内容加上指令格式中的偏移量得到的操作数有效地址

4.2 微程序控制的基本思想

用多条微指令(即一个微程序)解释每条指令的执行过程。全部的微程序有机地组合在一起,存储在控制存储器(只读存储器)中

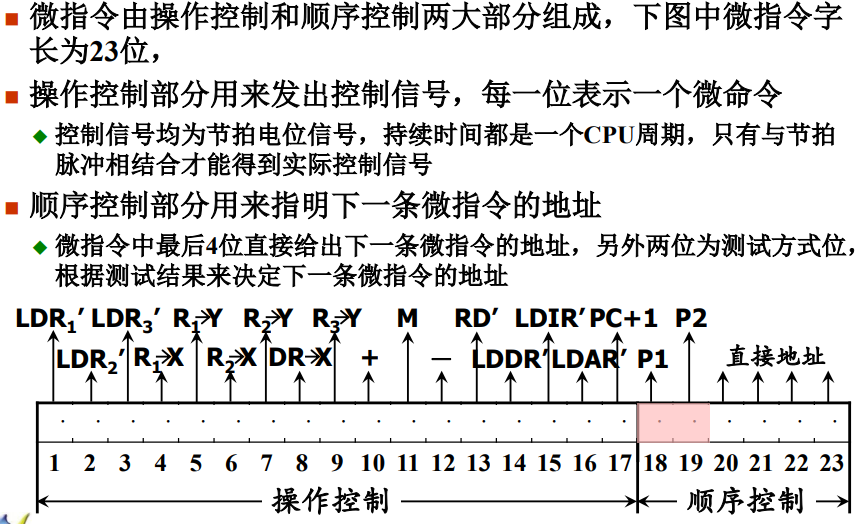

微指令基本格式

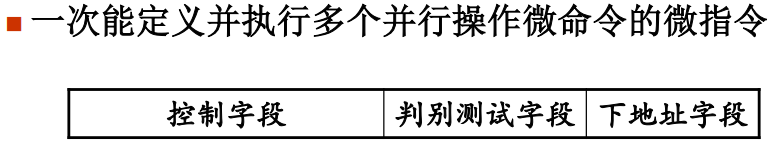

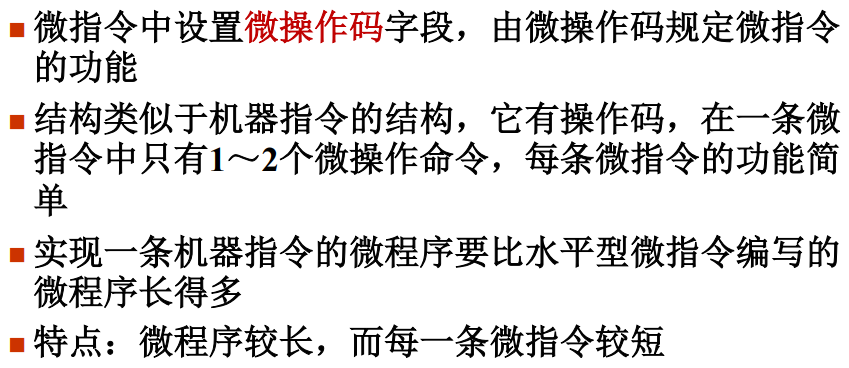

微指令格式大体分为两类:

水平型微指令

垂直型微指令

5. 中央处理器

5.1 流水线冒险

数据冒险 / 数据相关

一条指令的执行依赖于更早的一条还在流水线指令的执行结果

解决方法

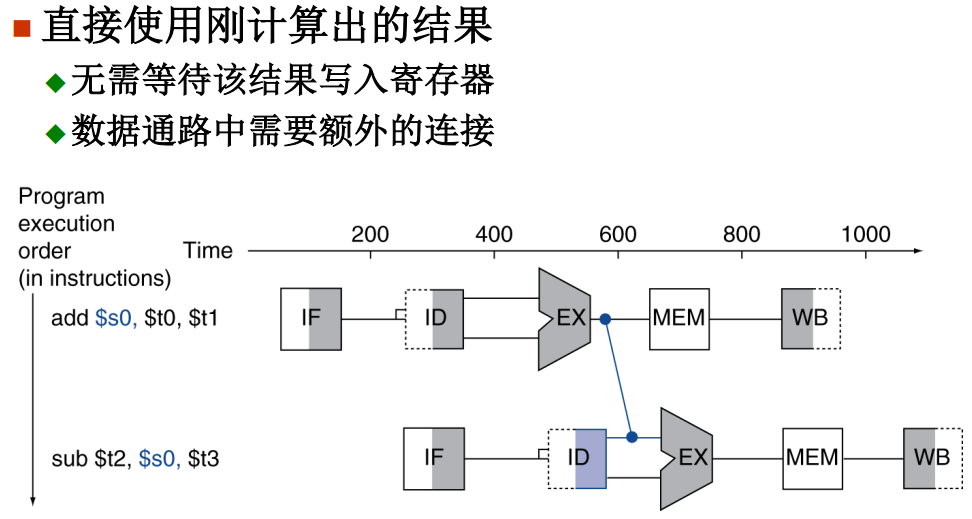

前推 / 旁路

5.2 流水线的性能指标

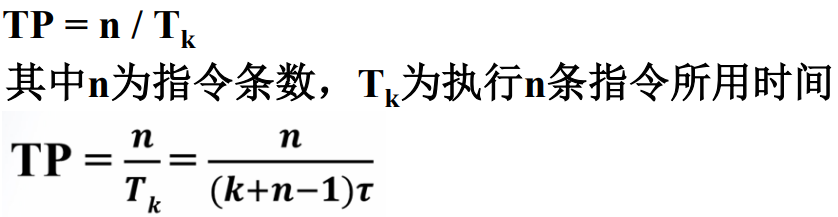

吞吐率(单位时间执行完毕的指令数)

k为流水线级数

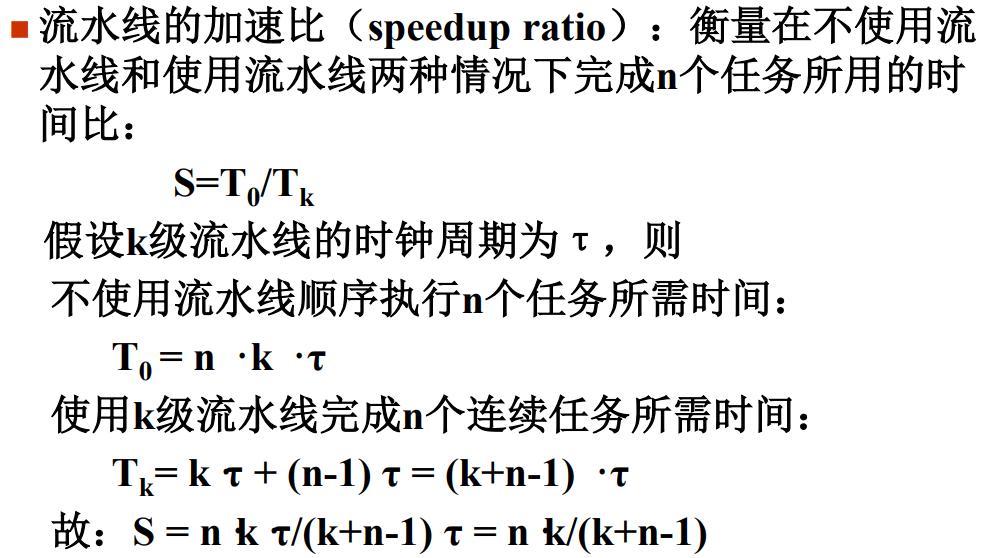

加速比

8. 输入输出系统

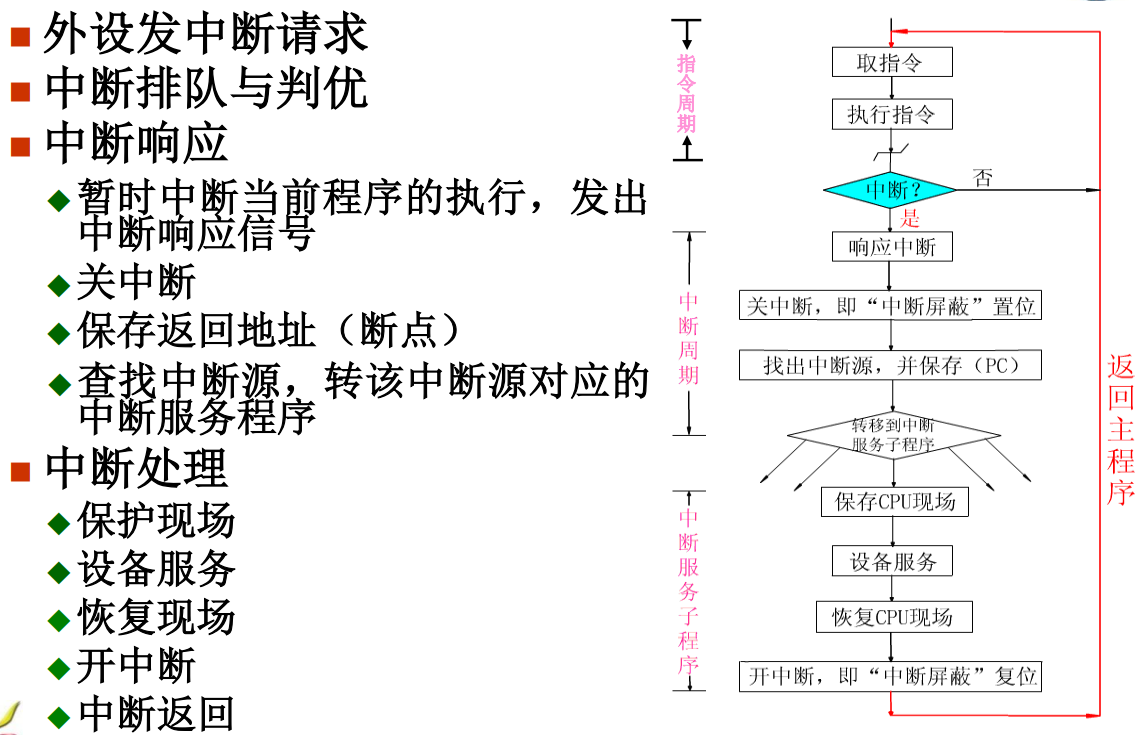

8.1 中断

处理过程

基本I / O接口

EI:允许中断

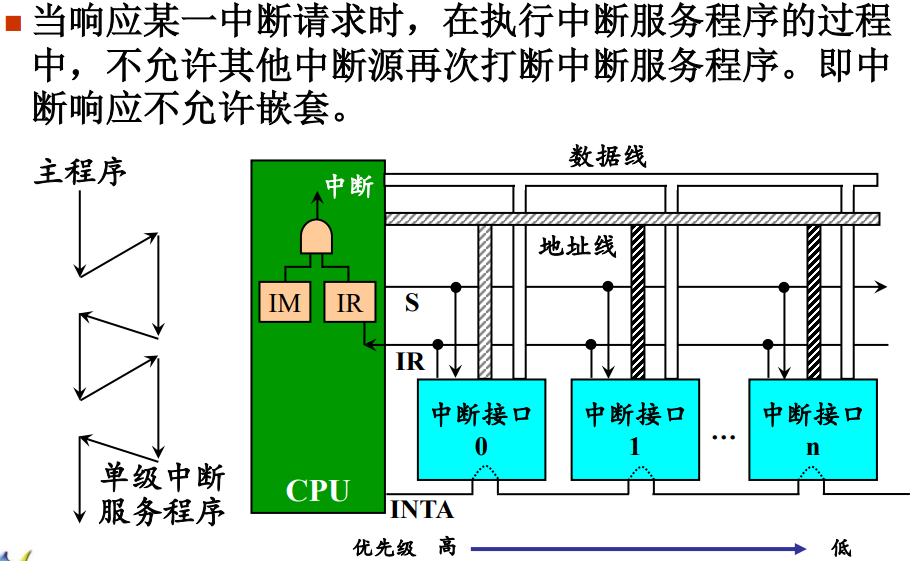

单级中断

多级中断

一个系统有n级中断,则CPU中有n个IR(中断请求位),n个IM(中断屏蔽位),某级中断被响应后,则关闭本级和低于本级的IM,开放更高级的IM(1 - 屏蔽中断、0 - 允许中断)

Tips

1. 时序信号

硬布线控制器一般采用主状态周期 - 节拍电位 - 节拍脉冲三级体制

微程序控制器一般采用节拍电位 - 节拍脉冲二级体制

2. RAM 和 ROM

RAM是随机存取存储器,具有易失性,需要刷新

ROM是只读存储器,是非易失性的,不需要刷新

SRAM和DRAM都是半导体随机读写存储器

闪速存储器具有RAM存储器的可擦、可写、可编程的特点,且所写入的数据在断电后不会消失(ROM)

3. 计算机系统中的存储器系统是指cache、主存储器和外存储器

4. 单地址指令中为了完成两个数的算术运算,除地址码指明的一个操作数以外,另一个数常需采用隐含寻址方式

5. 总线定时通常采用 同步定时 和 异步定时 两种方式

6. 三种集中式总线仲裁方式分别是 链式查询 计数器定时查询 和 独立查询

7. 程序控制类指令的功能是 改变程序执行顺序

8. PCI总线

HOST总线不仅连接主存,还可以连接多个CPU

PCI总线体系中有三种桥,都是PCI设备

桥的作用可使所有的存取都按CPU的需要出现在总线上

PCI总线的基本传输机制是猝发式传送

微型机的标准总线由16位的ISA总线,发展到32位的EISA总线和VESA总线,又进一步发展到64位的PCI总线

9. 将CPU和存储器合在一起称为主机

10. 形成指令地址的方式,称为指令寻址方式,有顺序寻址和跳跃寻址

11. 某寄存器中的值有时是地址,因此只有计算机的指令才能识别它

1102

1102

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?