一、组合逻辑电路

(1)实验目的

1.掌握组合逻辑电路的实际应用。

2.用实验验证所设计电路的逻辑功能。

3.掌握基本门多余端的处理方法。

4.判断、观测组合逻辑电路冒险并了解消除险象的方法。

(2)实验原理及设计过程

1.组合逻辑电路的设计:

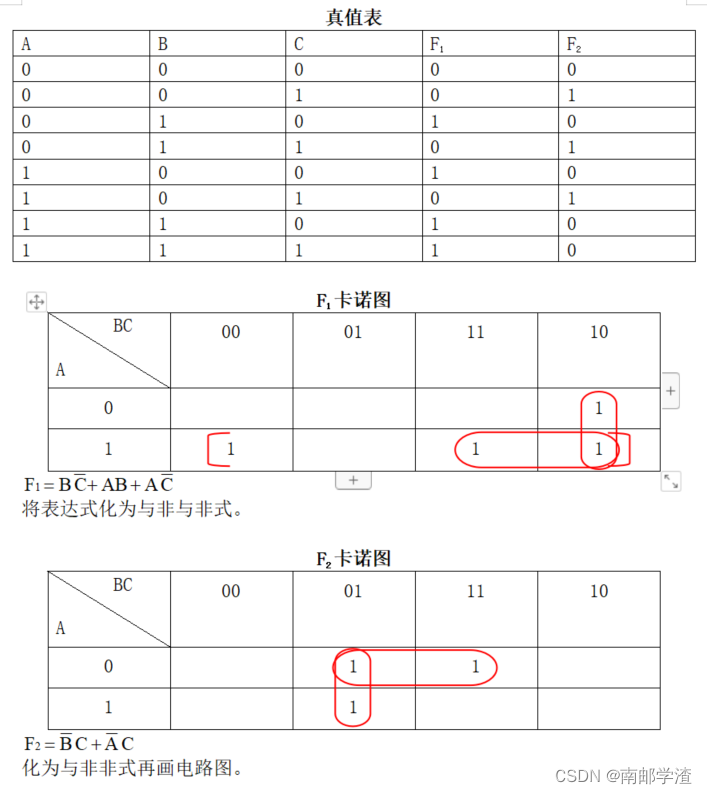

①正确将需求抽象为逻辑关系

②列出真值表

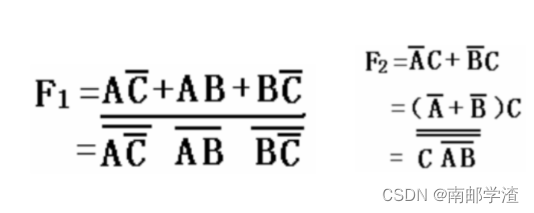

③得到逻辑表达式

④根据制图标准,正确绘制逻辑电路图

⑤仿真验证

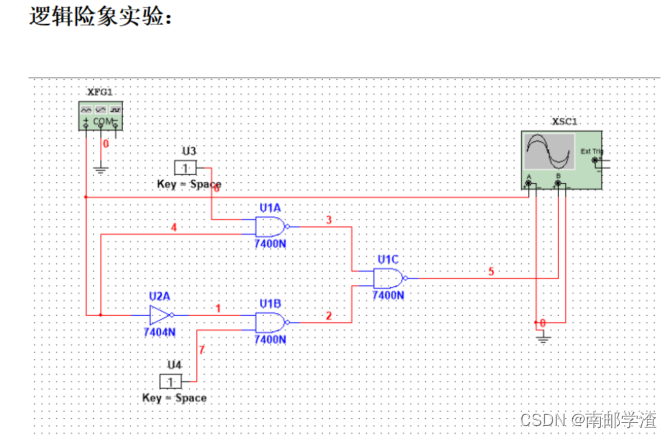

2.组合逻辑电路中的逻辑险象

按短暂尖峰极性的不同,可将冒险分为“0-1-0”型险象(也称“1”型)和

“1-0-1”型险象(也称“0”型)

逻辑险象:输入信号所经路径不同而引起的冒险现象

3.逻辑险象的判断与消除

逻辑险象的判断

①当逻辑函数中出现下列结果时将出现逻辑险象:

存在0-1-0型险象

存在1-0-1型险象

②卡诺图若出现“相切”的卡诺圈,且相切部分未被另外卡诺圈包围,即可断定存在逻辑冒险。

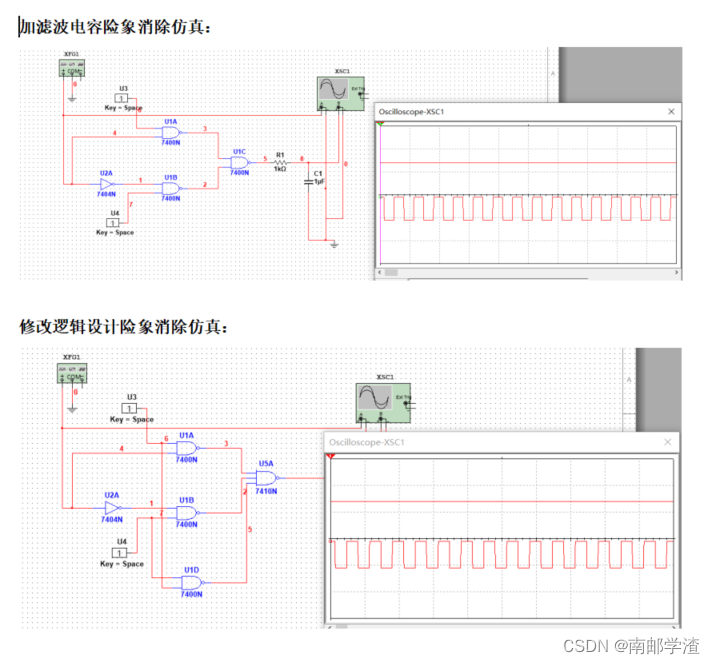

逻辑险象的消除

①增加多余项,在卡诺图中两圈相切处增加一个冗余圈,可以消除逻辑冒险。

②输出端加滤波电路,可消除逻辑冒险和功能冒险

③加取样脉冲,当信号变化完成后,才启动取样脉冲,可避免逻辑冒险和功能冒险

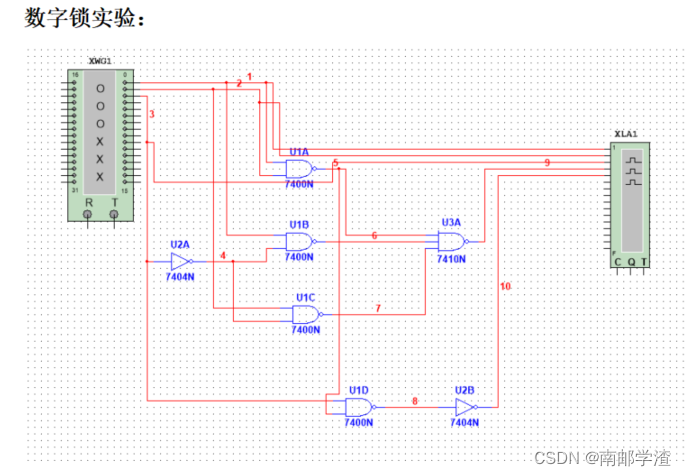

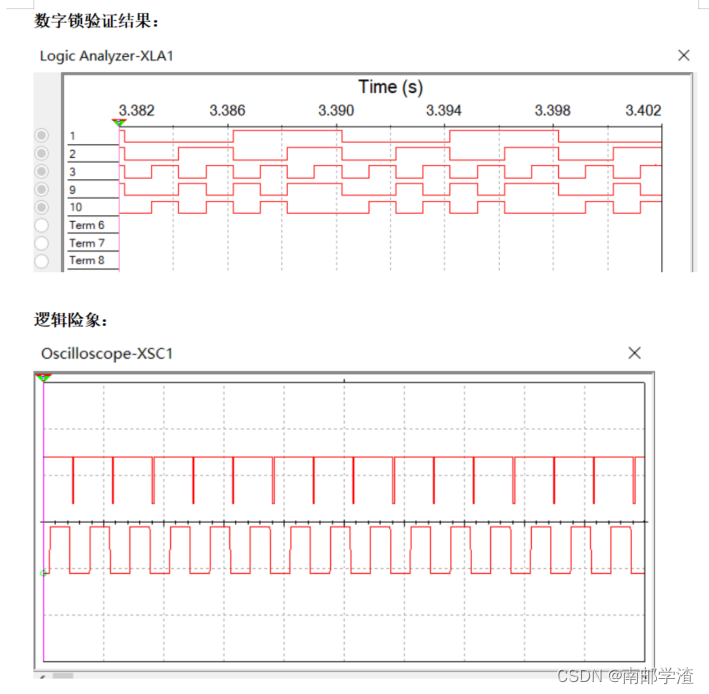

数字锁实验:

用与非门设计一数字锁逻辑电路,该锁有3个按钮A、B、C,当A、B、C同时按下,或A、B同时按下,或只有A或B按下时开锁,如果不符合上述条件应发出报警。对于逻辑组合电路来说,可以根据题目给的要求列真值表,画出卡洛图得出表达式,最后再画出电路图。

将两个输出端接在发光二极管上,手动改变ABC的组合取值,观察输出端的亮暗情况是否与真值表一致。

(3)实验电路图

(4)实验数据分析和实验结果

本文详细介绍了组合逻辑电路的实验过程,包括实验目的、设计步骤、逻辑险象的判断与消除方法。通过与非门设计了一数字锁逻辑电路,验证了电路功能,并通过手动改变输入观察输出,确保与真值表一致。实验还探讨了如何在卡诺图中消除冒险,以及使用滤波电路和取样脉冲来避免冒险现象。

本文详细介绍了组合逻辑电路的实验过程,包括实验目的、设计步骤、逻辑险象的判断与消除方法。通过与非门设计了一数字锁逻辑电路,验证了电路功能,并通过手动改变输入观察输出,确保与真值表一致。实验还探讨了如何在卡诺图中消除冒险,以及使用滤波电路和取样脉冲来避免冒险现象。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?