题目概述:

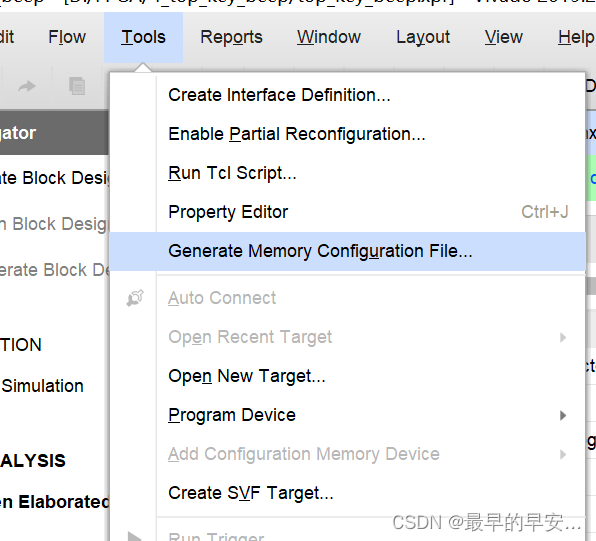

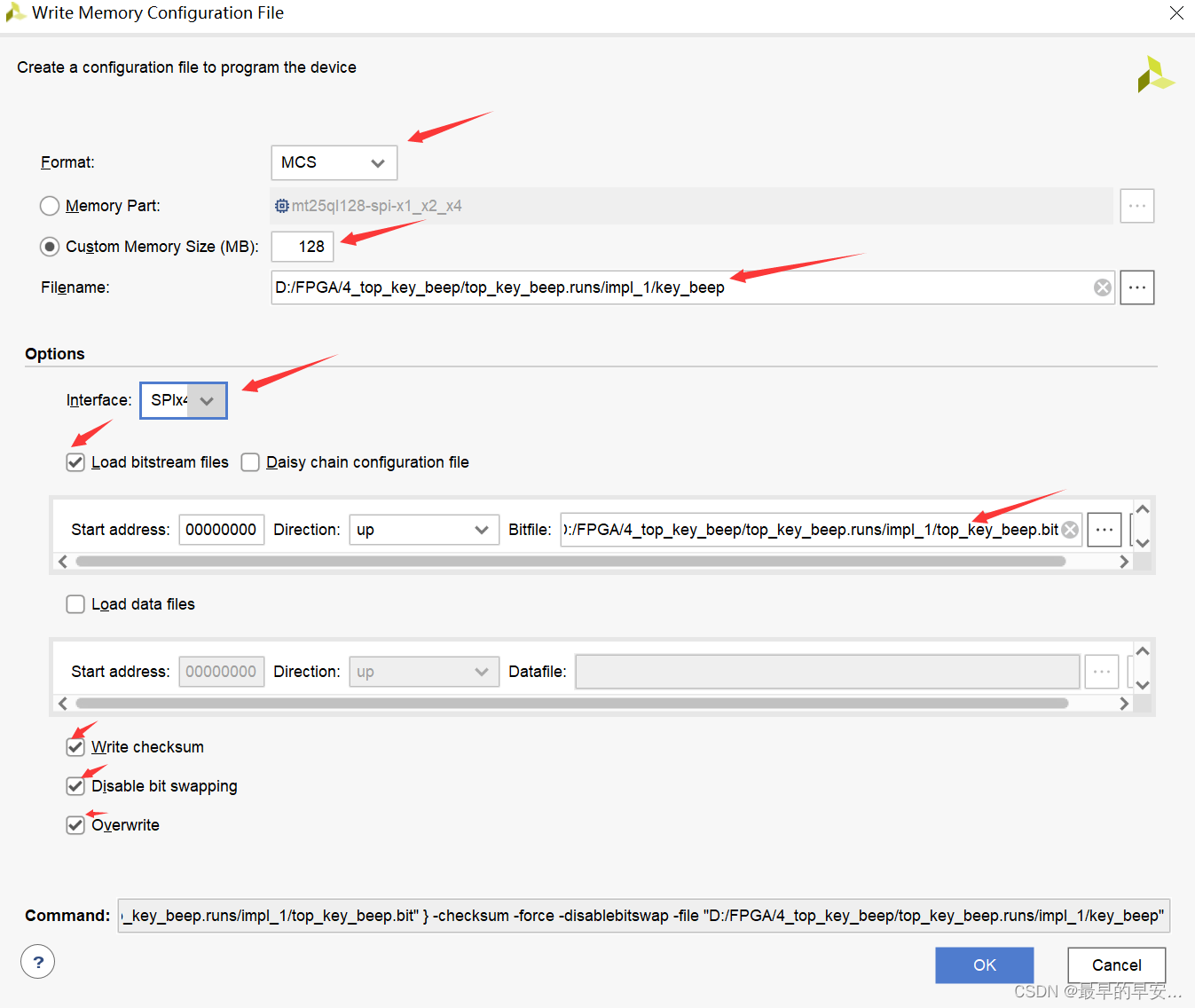

为了能够让工程上电就能运行,则需要生成固化文件,将文件固化到板载flash中去,这样上电就可以启动。

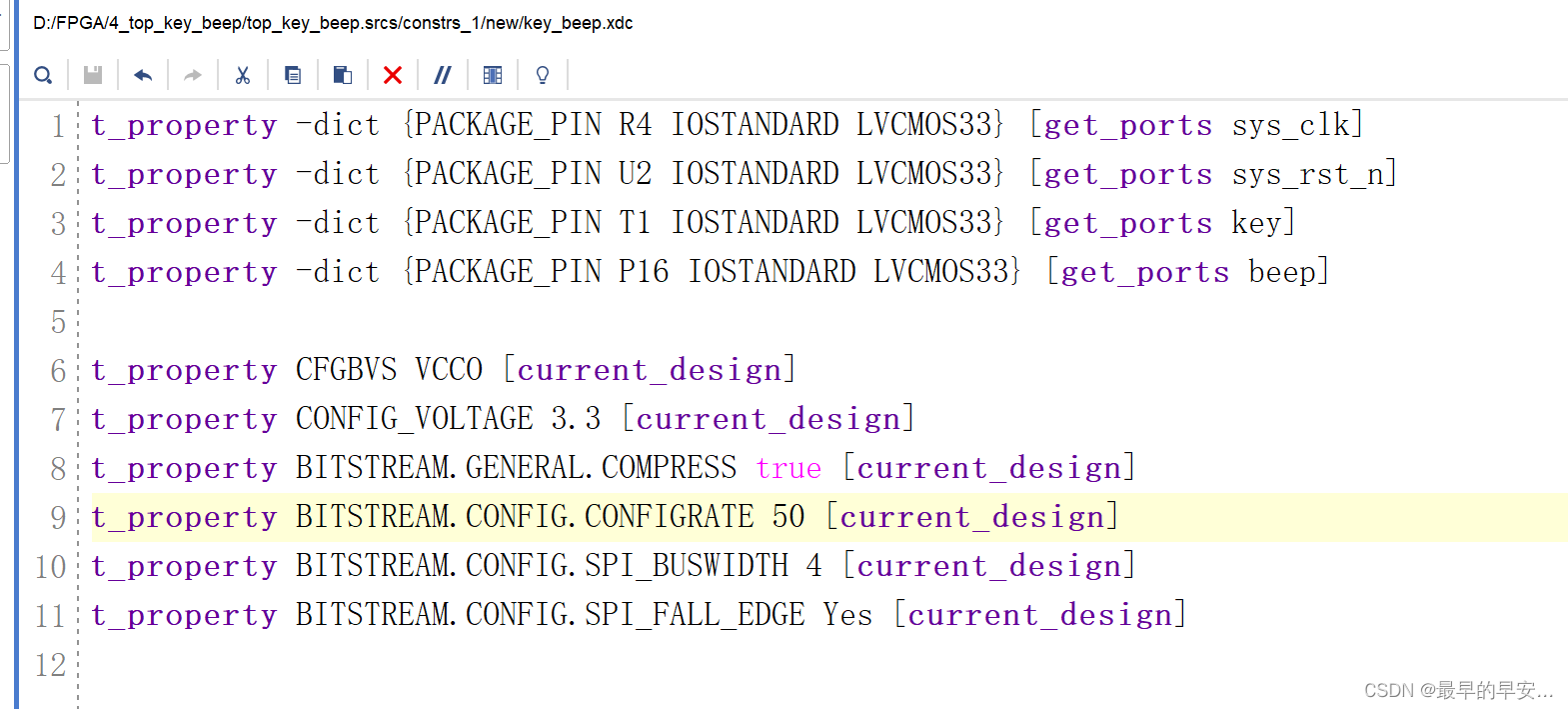

在生成固化文件之前我们先打开工程时序约束文件,在时序约束文件里添加下面的一段原语:

set_property CFGBVS VCCO [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property BITSTREAM.GENERAL.COMPRESS true [current_design]

set_property BITSTREAM.CONFIG.CONFIGRATE 50 [current_design]

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.SPI_FALL_EDGE Yes [current_design]

如下:

结束并完成。

2101

2101

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?