Verilog数字系统设计十二

复杂数字电路设计2

前言

随着人工智能的不断发展,机器学习这门技术也越来越重要,很多人都开启了学习机器学习,本文就介绍了机器学习的基础内容。提示:以下是本篇文章正文内容:

FIFO 是先入先出存储器的缩写,FIFO 控制器在数字系统中被大量使用,可以作为数据缓存使用。

一、什么是FIFO控制器?

FIFO 是先入先出存储器的缩写,FIFO 控制器在数字系统中被大量使用,可以作为数据缓存使用。

二、编程

1.要求:

- FIFO控制器设计

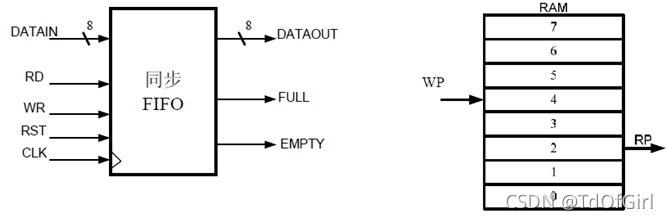

- FIFO 是先入先出存储器的缩写,FIFO 控制器在数字系统中被大量使用,可以作为数据缓存使用。时钟同步的FIFO 控制器接口如下图所示,主要接口信号定义如下:

RST_N:异步复位信号,当RST_N 为低电平时,FULL 输出‘0’,EMPTY 信号输出‘1’电平,FIFO 指针指向0,FIFO 被清空;

CLK:时钟信号,输出信号与CLK 信号同步;

DATAIN:数据输入信号,8 位总线;

RD:读有效信号,高电平有效,当RD 位高时,在时钟信号CLK 的上升沿,DATAOUT 输出一个8 位的有效数据;

WR:写有效信号,当WR 为高电平时,在CLK 的上升沿,从DATAIN 信号向存储器写入一个8 位的有效数据;

DATAOUT:数据输出信号,8 位总线,在CLK 的上升沿,当RD 为高电平时,从FIFO 中输出一个8 位的数据;

FULL:存储器写满标志信号,高电平时表示存储器中的数据已经写满;

EMPTY:存储器读空标志信号,高电平时表示存储器中的数据已经被读空了;

2.设计思路:

3.FIFO控制器实现:

代码如下:

module fifo(dataOut,full,empty,clk,rst,dataIn,wr,rd);

input clk,rst,wr,rd;

output full,empty;

input[3:0] dataIn;

output[3:0] dataOut;

reg[3:0] fifo_reg[3:0];

reg[1:0] w_head,R_tail;

reg[1:0] count;

reg [3:0] dout;

reg f,e;

parameter MAX = 3;

//*************update w_head*************

always @ (posedge clk)

if(!rst)

w_head <= 2'd0;

else if(wr && !full)

w_head <= w_head +1'b1;

//*************update R_tail*************

always @ (posedge clk)

if(!rst)

R_tail <= 2'd0;

else if(rd && !empty)

R_tail <= R_tail + 1'b1;

//**************count************

always @(posedge clk)

if(!rst)

count <= 2'd0;

else

case({rd,wr})

2'b00:

count <= count;

2'b01:

if(count != MAX)

count <= count + 1'b1;

2'b10:

if(count != 0)

count <= count - 1'b1;

2'b11:

;

endcase

//************rd**********

always @(posedge clk)

if(!rst)

dout <= 4'd0;

else if(rd && !empty)

dout <= fifo_reg[R_tail];

///***************wr**********

always @(posedge clk)

if(wr && !full)

fifo_reg[w_head] <= dataIn;

always @ (posedge clk)

if(count==0)

e <= 1'b1;

else

e <= 1'b0;

always @ (posedge clk)

if(count==MAX)

f <= 1'b1;

else

f <= 1'b0;

assign full = f;

assign empty = e;

assign dataOut = dout;

endmodule

测试代码如下:

module fifo_tb();

reg clk_t,rst_t,wr_t,rd_t;

reg [3:0] dataIn_t;

wire [3:0] dataOut_t;

wire full_t,empty_t;

initial

begin

clk_t =0;

rst_t =0;

#100

rst_t = 1;

wr_t =0;

rd_t = 0;

#20

wr_t = 1;

dataIn_t = 4'd1;

#20

dataIn_t = 4'd2;

#20

dataIn_t = 4'd3;

#20

dataIn_t = 4'd4;

#20

wr_t =1;

#20

wr_t =0;

rd_t =1;

#100;

rd_t = 0;

wr_t = 1;

dataIn_t = 4'd6;

#20

dataIn_t = 4'd7;

rd_t = 1;

#20

dataIn_t = 4'd8;

#20

dataIn_t = 4'd9;

#20

wr_t = 1;

dataIn_t = 4'd5;

#20

dataIn_t = 4'd2;

#20

rd_t =0;

dataIn_t = 4'd3;

#20

dataIn_t = 4'd4;

#20

wr_t =0;

rd_t =1;

end

always #10 clk_t =~clk_t;

fifo myfifo(

.clk(clk_t),

.rst(rst_t),

.wr(wr_t),

.rd(rd_t),

.dataIn(dataIn_t),

.dataOut(dataOut_t),

.full(full_t),

.empty(empty_t)

);

endmodule

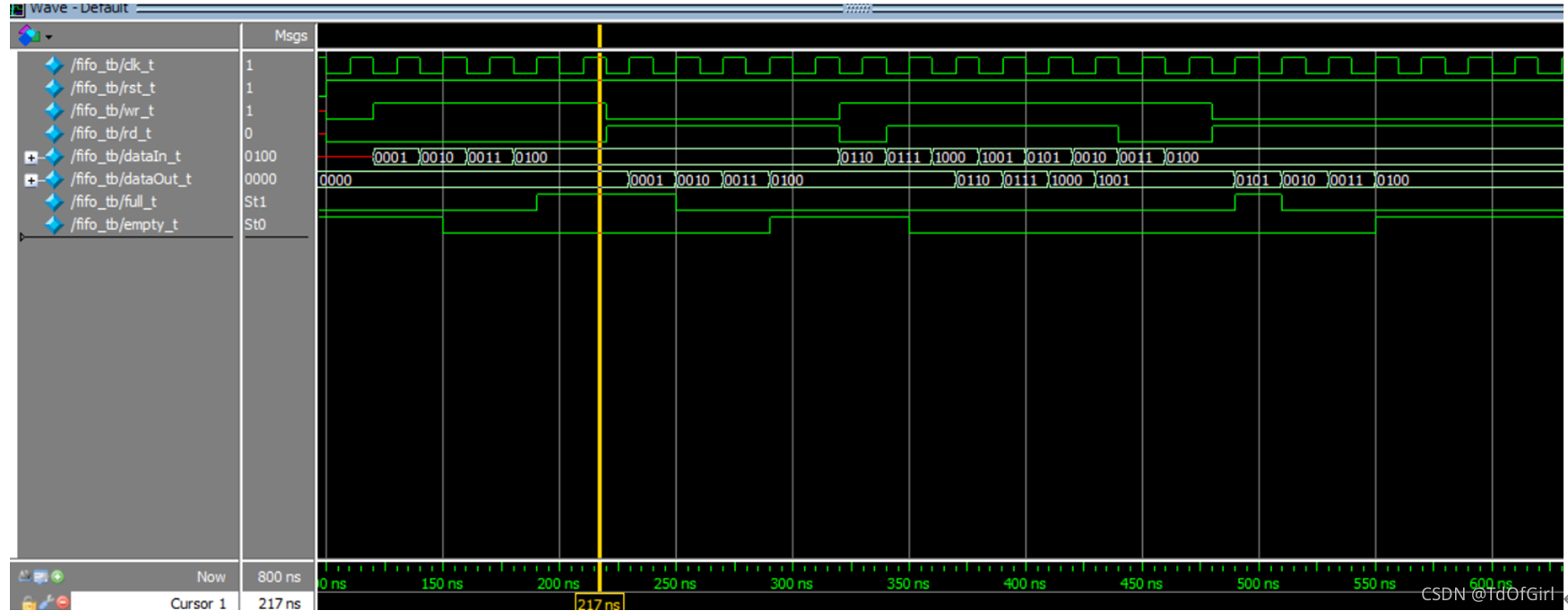

仿真波形如下:

总结

提示:

以上就是今天要分享的内容,本文仅仅简单介绍了用Verilog实现FIFO控制器设计。

本文详细介绍了如何使用Verilog设计FIFO控制器,包括接口定义、设计思路及具体实现代码。通过实例展示了FIFO控制器在时钟同步下的工作原理,提供了测试代码和仿真波形,帮助理解FIFO在数字系统中的应用。

本文详细介绍了如何使用Verilog设计FIFO控制器,包括接口定义、设计思路及具体实现代码。通过实例展示了FIFO控制器在时钟同步下的工作原理,提供了测试代码和仿真波形,帮助理解FIFO在数字系统中的应用。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?