主要内容

综合,就是把idea变成现实的过程;

逻辑综合和功能仿真/形式验证可以是同步进行的;

Synthesis Flow

顶层综合的flow,主要分为五大步骤;

①首先导入库文件和design设计文档/RTL coding;

②第二步是加入一些时序约束及设计规则约束;

③利用综合工具跑综合,通过改一些不同的参数,得到不同的结果;这一步将占用EDA工具95%时间;

④对得到的结果进行横向和纵向进行分析,如在同一个结果中分析时序差的原因,或将不同参数得到的结果进行横向对比;这一步占用人的时间最多;

⑤将符合要求的综合结果输出netlist;

在整个后端flow中,一般的工作方向有两类,一是flow开发,编写所需要的各种flow脚本;二是进行综合结果分析的工作,就是利用开发的flow,通过调节不同参数,分析得到的不同结果及debug;

Synthesis

Synthesis=Translation+Gate Mapping+Logic Optimization=转换+门级映射+逻辑优化;

当我们告诉综合工具要做综合了,工具就是做了上述三个事情,先把RTL coding 和约束进行转换,然后再进行门级映射gate mapping,最后再做逻辑优化;

门级网表:前面第一课就说过,门级网表也是代码,不过不是像verilog coding那种,而是工具自动得到的门级电路图,如上图右侧所示,里面包含了各种门和连线;

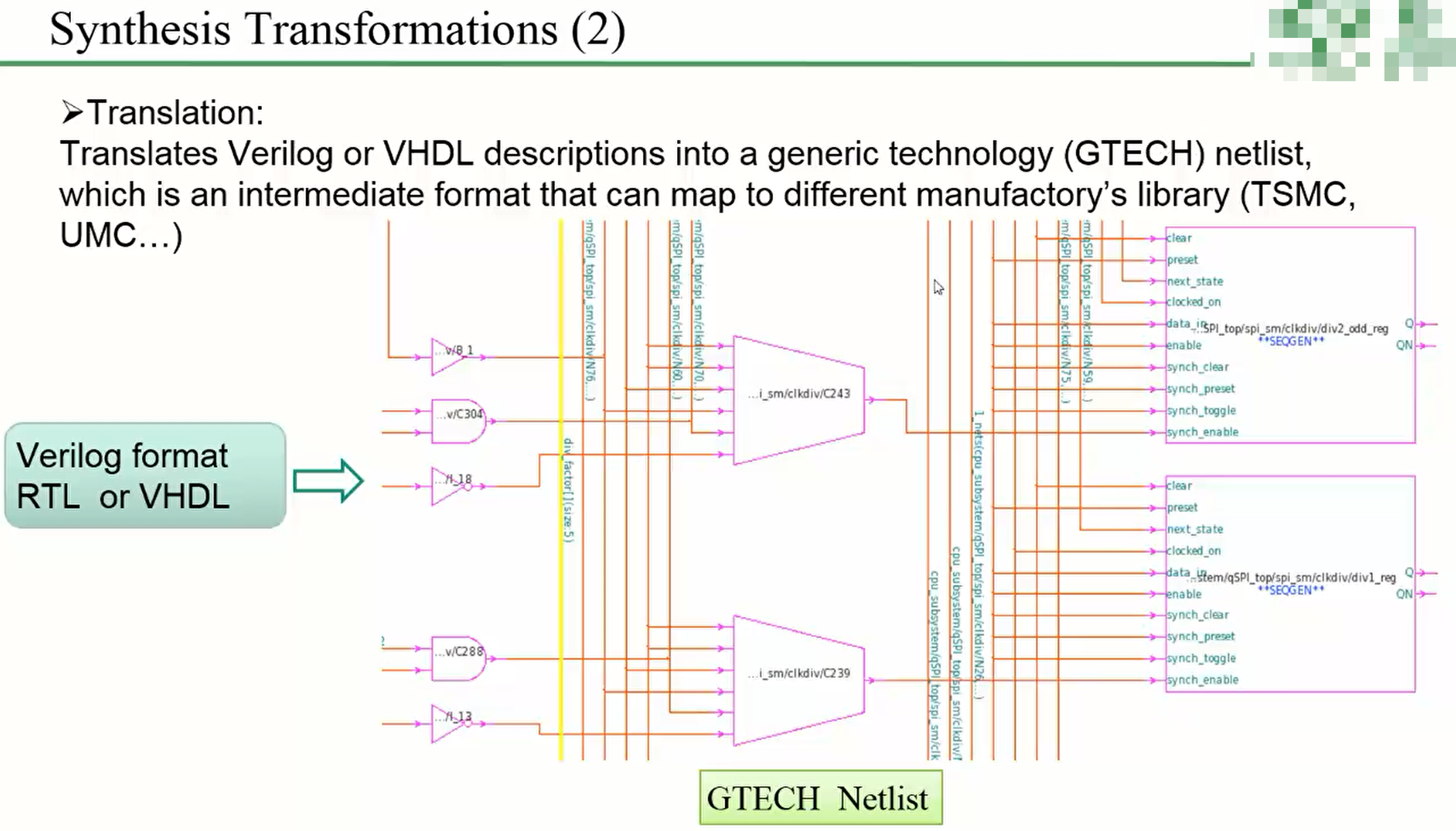

Translation

当我们把coding读到工具里面时,工具会立刻转换并得到一个GTECH网表(gtech),这是一个过渡用的中间网表,这个网表里面的这些门是EDA软件得到的,并不是真实存在的,所以那些门的延时之类的数据是不存在的;

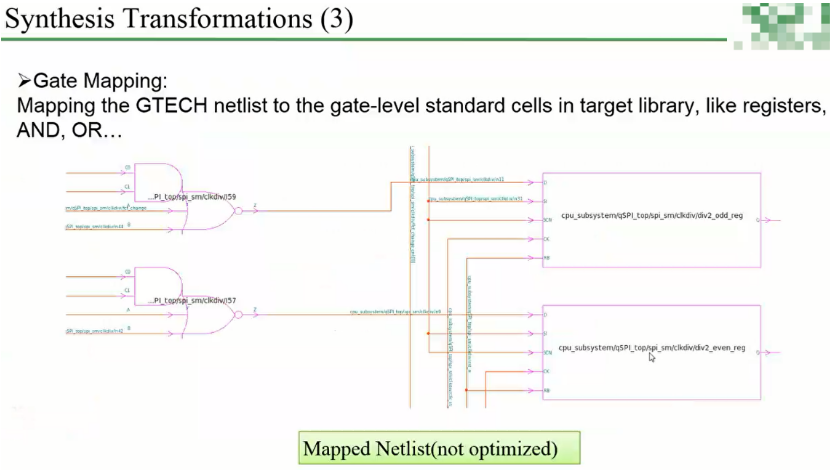

Gate Mapping

Gate Mapping门级映射,建立理解就是替换,前面不是得到了GTECH网表嘛,里面的门都是EDA工具得到的,在此处,就是确定了代工厂后,将GTECH中的各个门换成相应代工厂内的标准门,这个简单替换的过程叫映射;

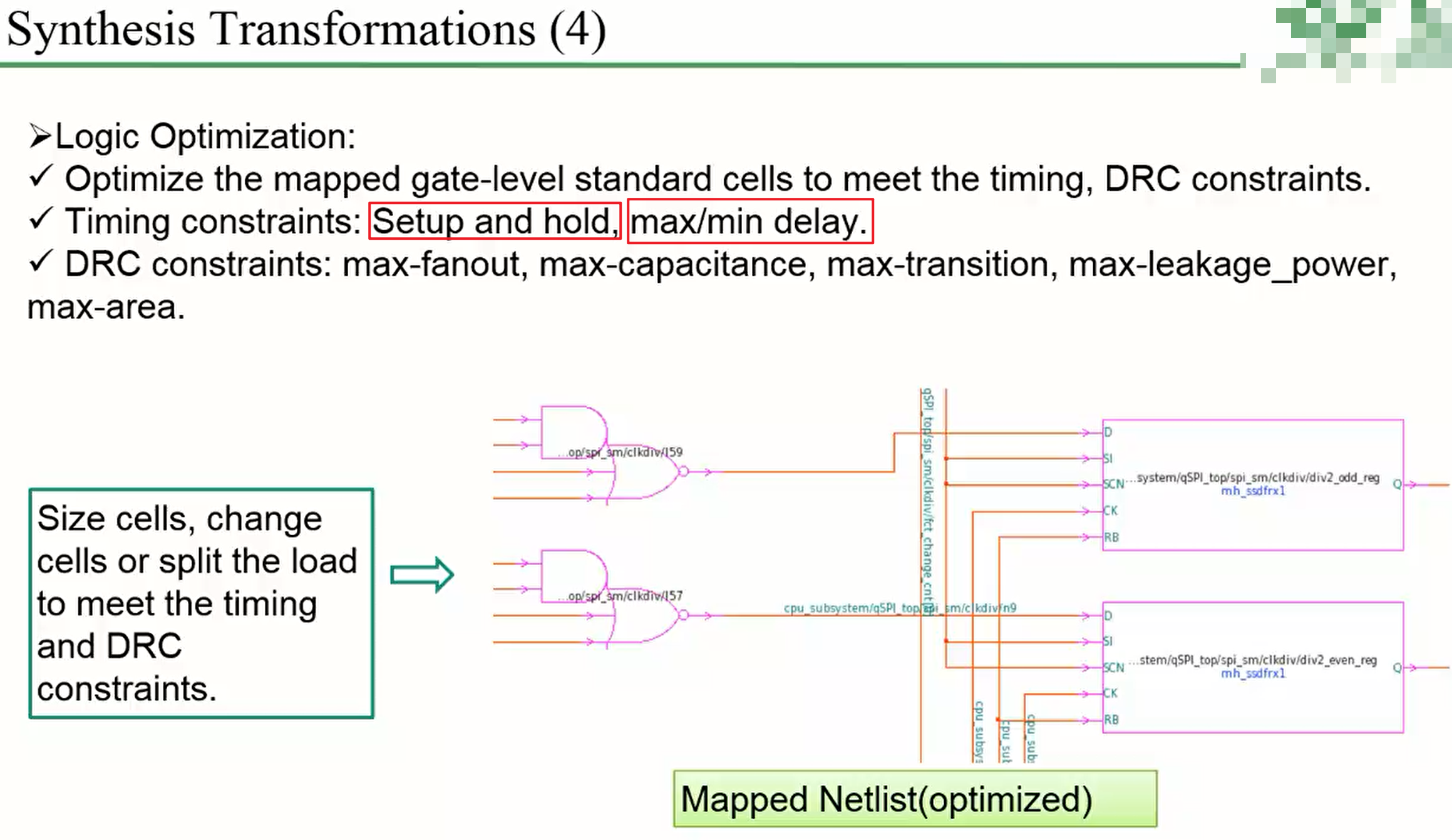

Logic Optimization

本文详细介绍了集成电路设计中的SynthesisFlow,包括RTL编码到门级映射、逻辑优化的过程。重点讨论了综合工具如何转换设计、门级映射以及逻辑优化以满足时序、面积和DRC约束。此外,还提到了综合过程中的关键步骤,如设置约束、选择目标工艺库和链接库,以及如何分析和优化综合结果。

本文详细介绍了集成电路设计中的SynthesisFlow,包括RTL编码到门级映射、逻辑优化的过程。重点讨论了综合工具如何转换设计、门级映射以及逻辑优化以满足时序、面积和DRC约束。此外,还提到了综合过程中的关键步骤,如设置约束、选择目标工艺库和链接库,以及如何分析和优化综合结果。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?