文章目录

一、原理图

(一)创建项目

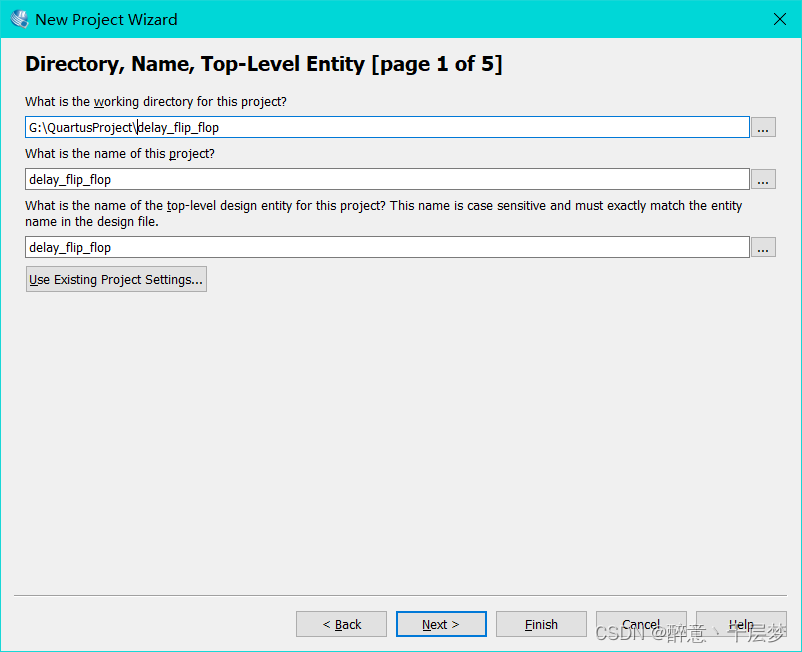

设置项目路径以及项目名称、顶层名

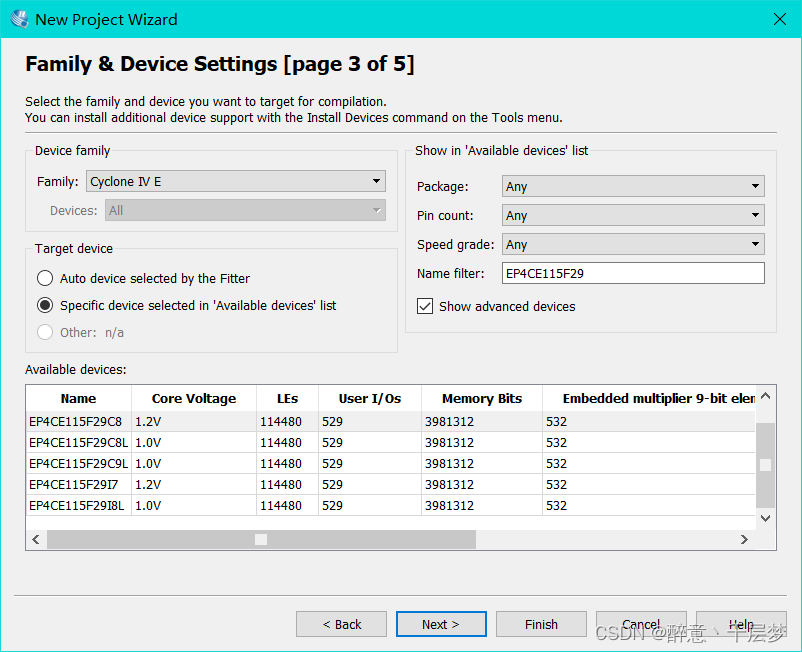

选择器件型号

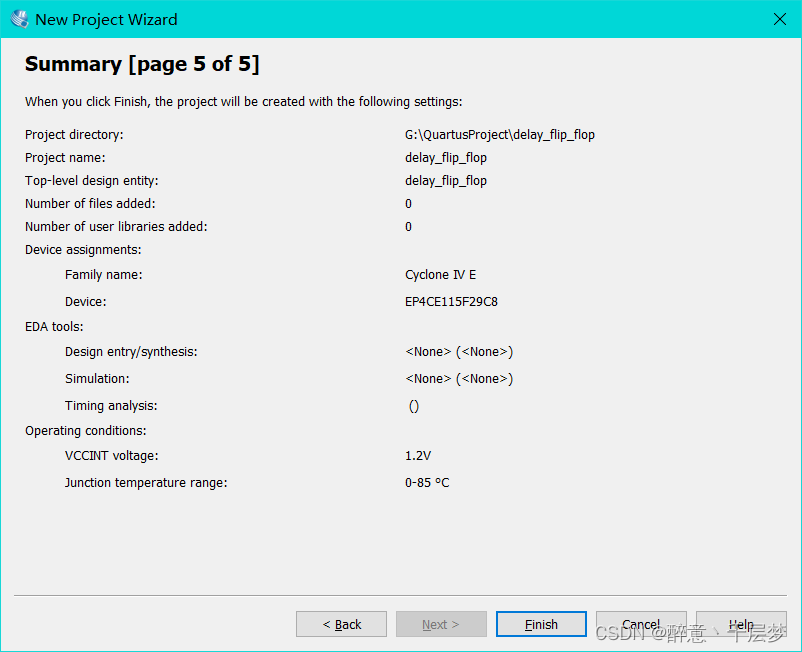

最终信息

(二)绘制D触发器原理图

点击file -> new -> Block Diagram 新建框图

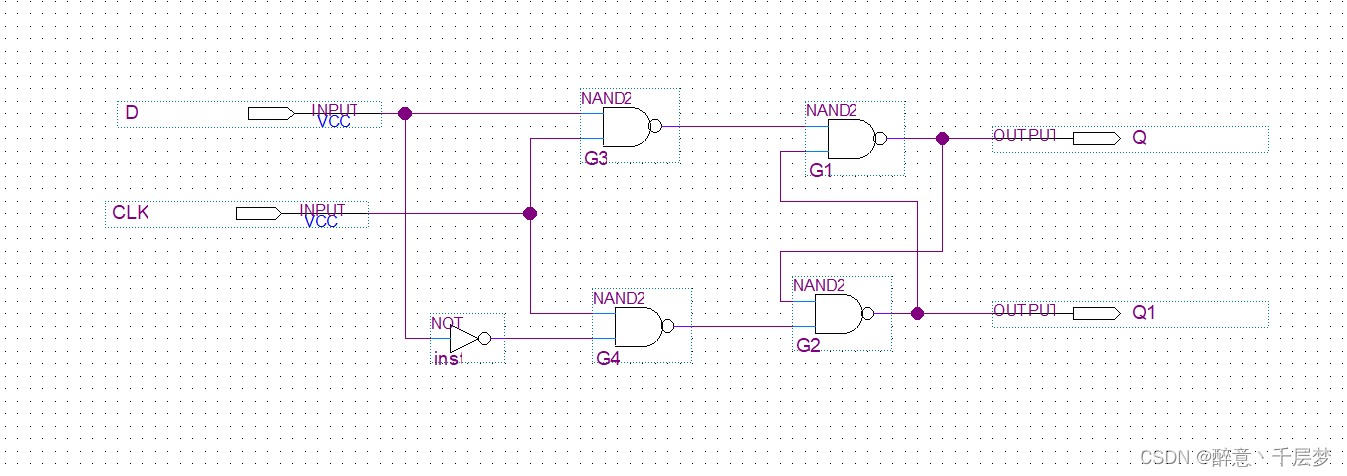

D触发器由一个非门、两个输出、两个输入、四个与非门共同构成,最终效果图如下

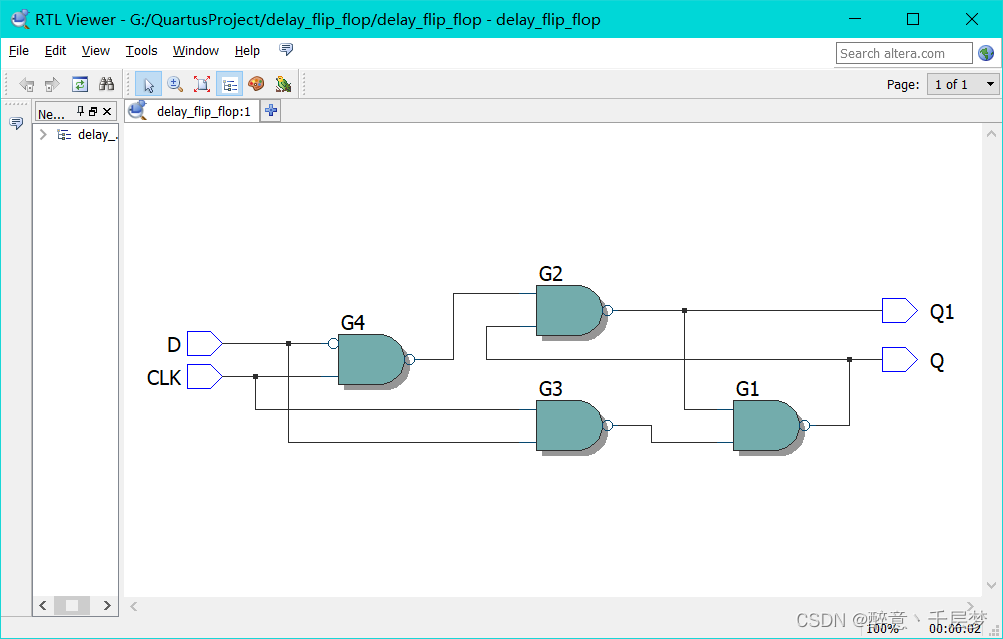

绘制完成再编译,编译成功后点击Tools -> netlist Viewers -> RTL Viewer 可以查看硬件电路图

(三)查看仿真波形

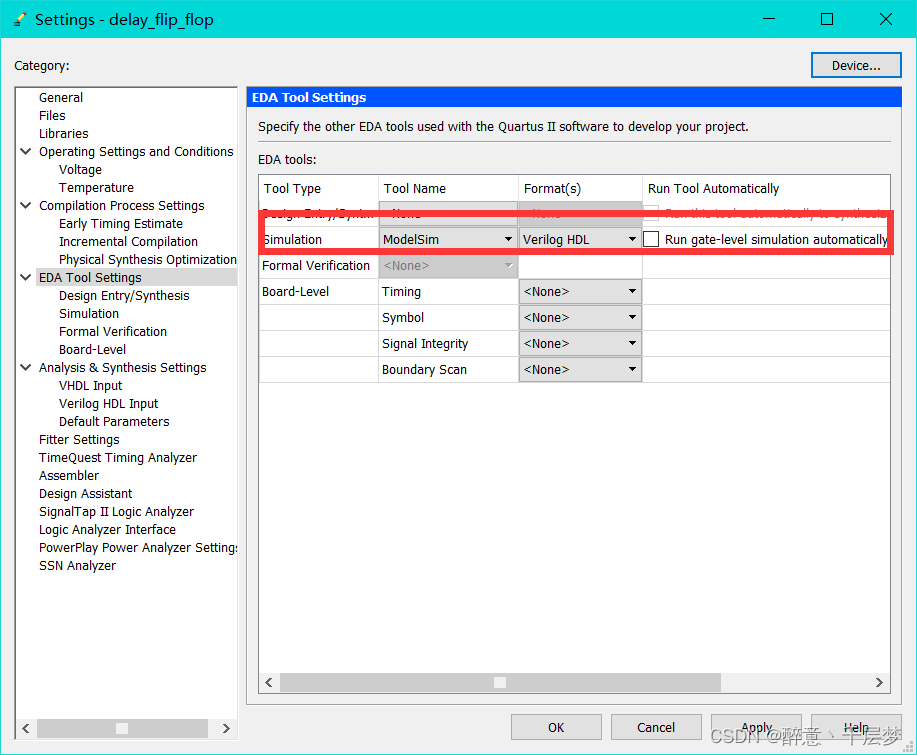

1. 配置仿真工具

点击Assignments -> setting ->EDA Tool Setting

选择仿真工具为ModelSim

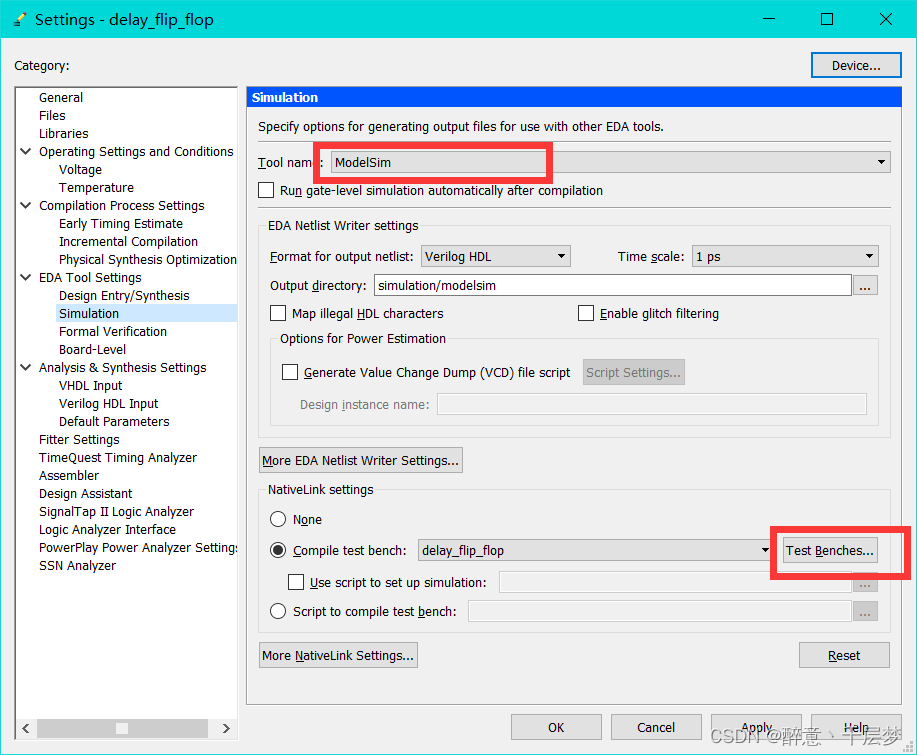

在Simulation里面把tool换成ModelSim,再点击Test Benches

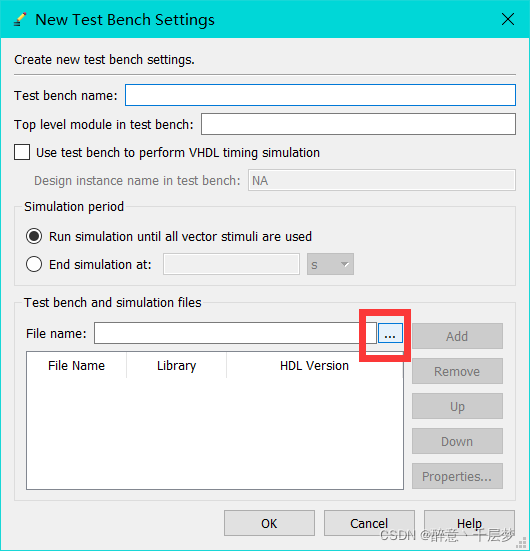

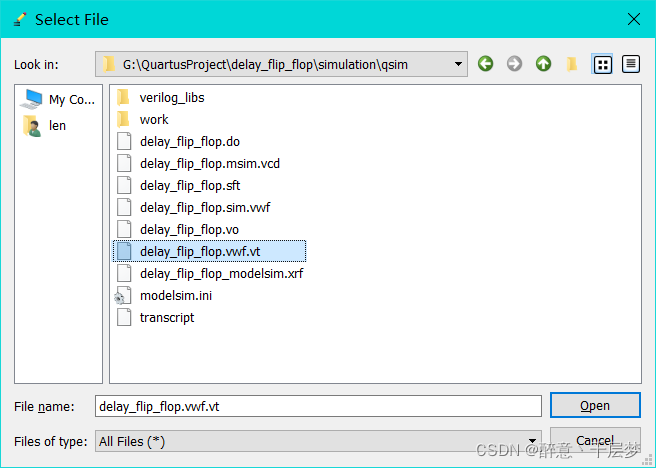

点击选择文件,选择qsim文件夹里面后缀为vt的文件即可

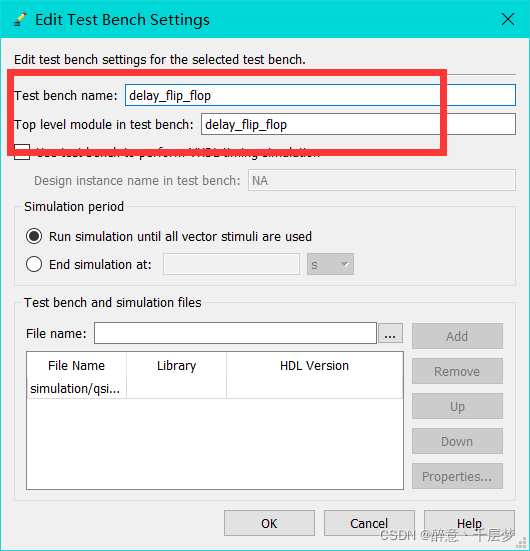

最后设置个名称就行

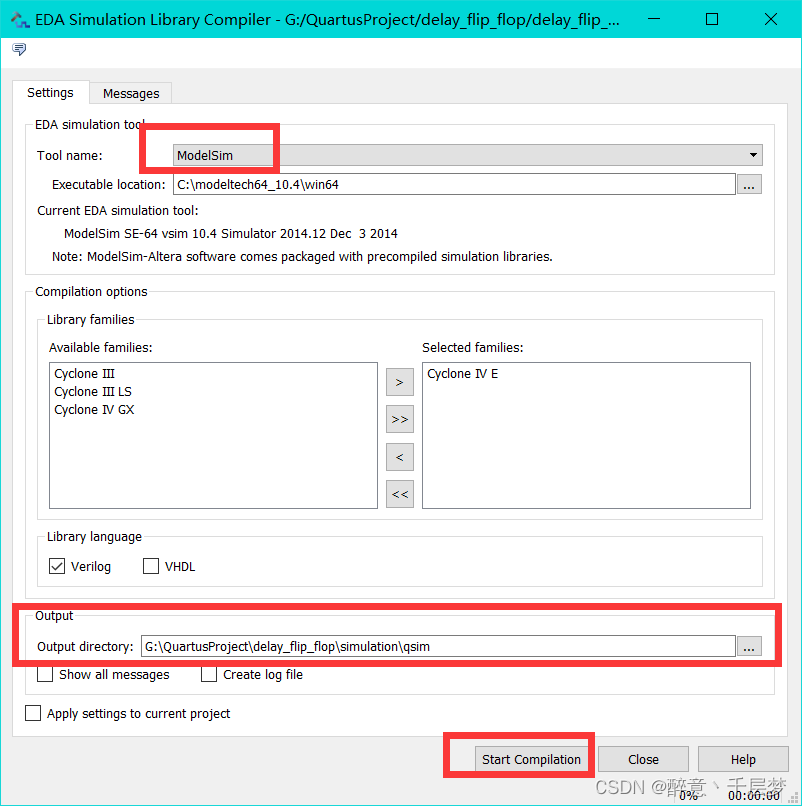

2.加载仿真库文件

点击Tools -> Launch Simulation Library,按如下操作即可

3.添加仿真文件

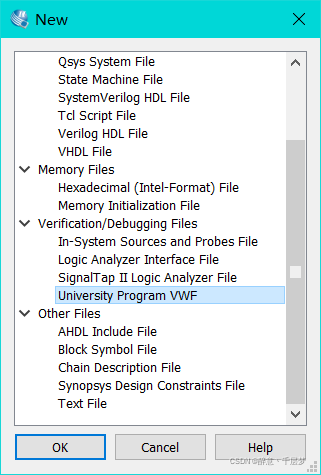

点击file -> new -> University Program VMF新建波形文件

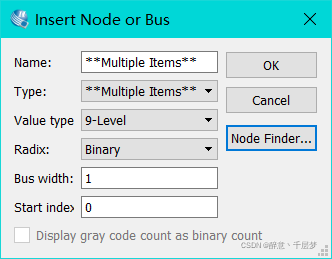

点击Edit -> insert -> insert Node or Bus进行添加

进行添加引脚

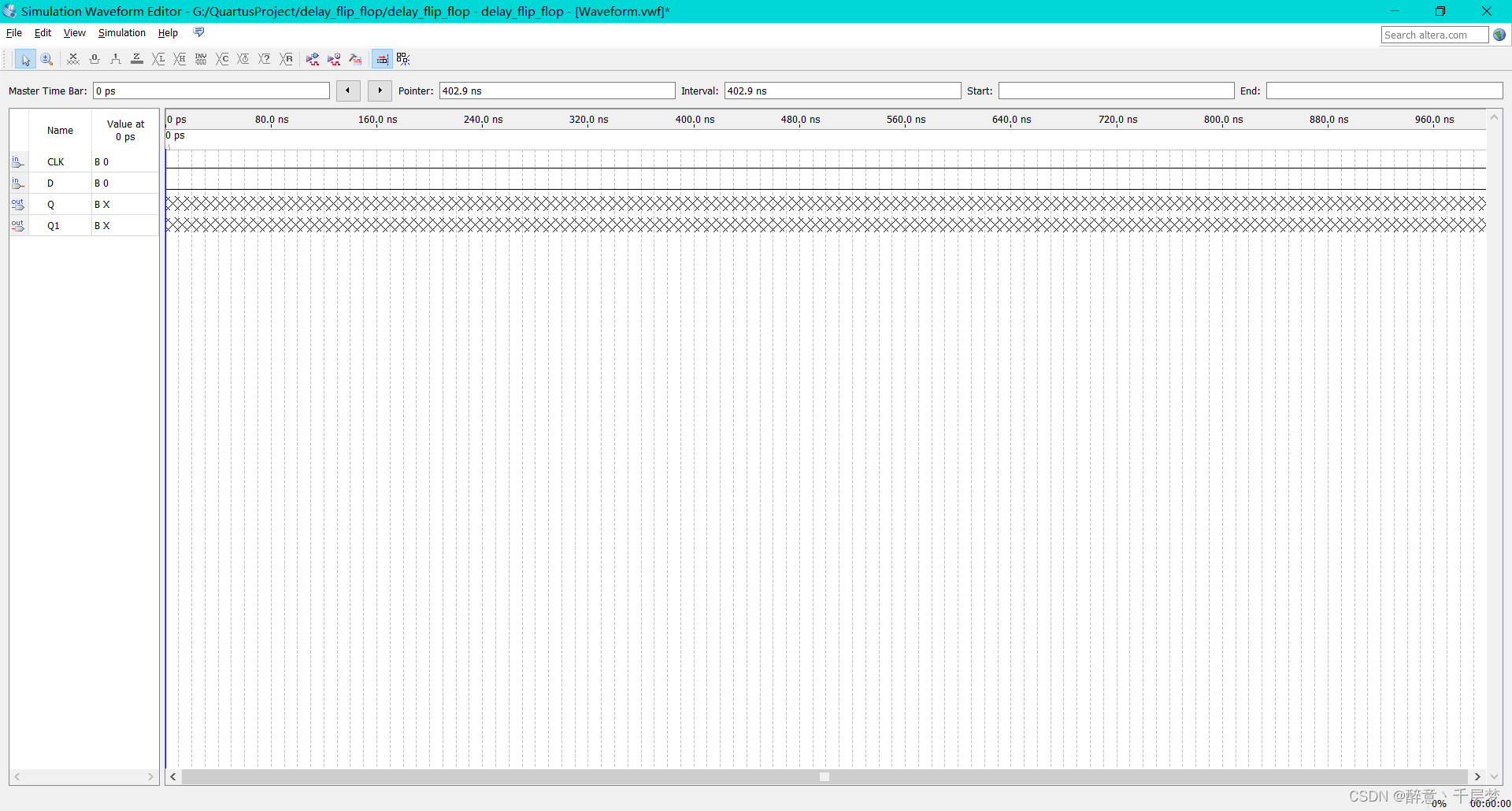

添加完成后界面会变成这样

主界面会出现对应引脚的波形

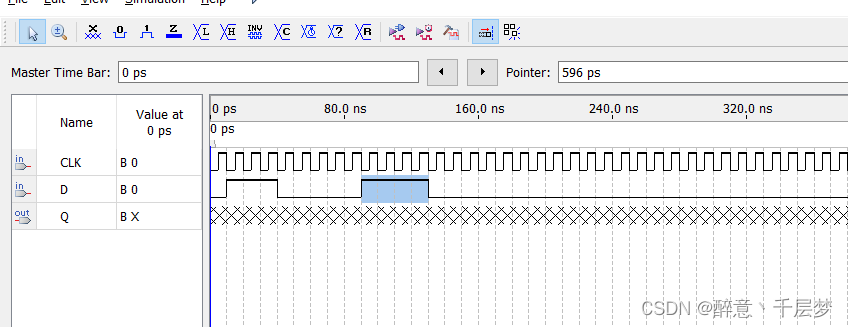

4.仿真

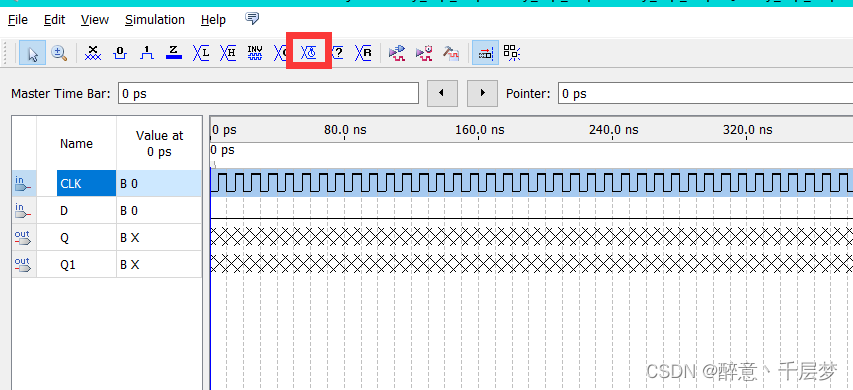

把输入clk设置为时钟信号

把输入D随便设置几个低电平和高电平

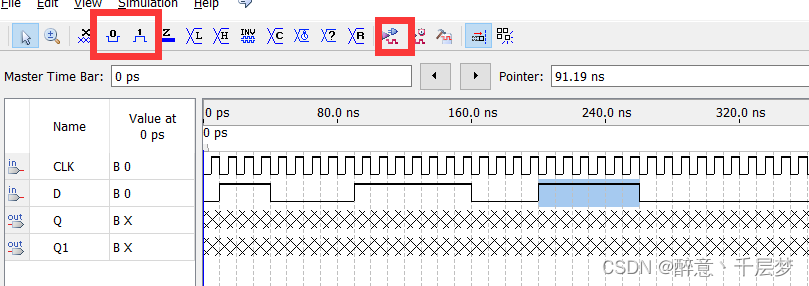

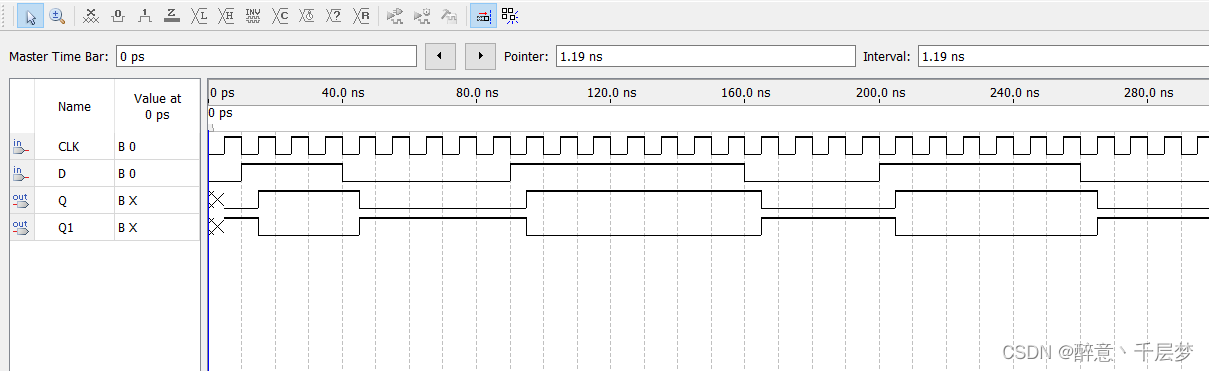

最后运行结果

在上升沿到来,Q的值跟随D的值进行变化,Q与Q1互为相反

二、调用库

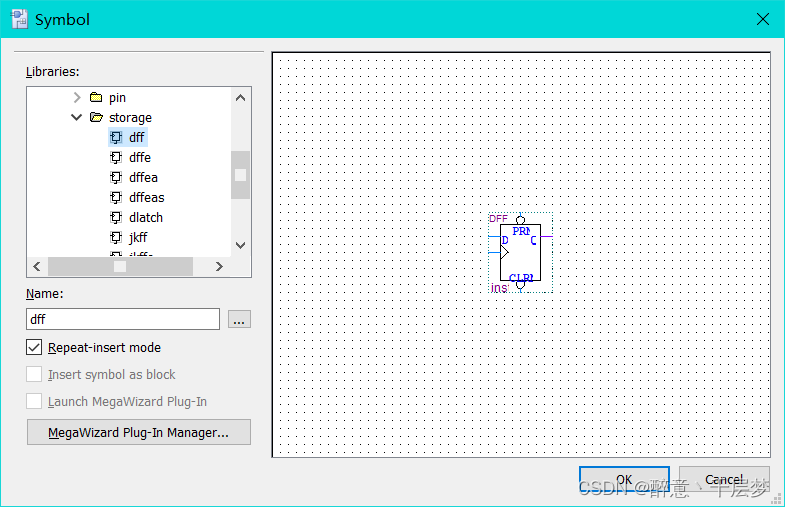

(一)绘制原理图

直接调用库里面的D触发器

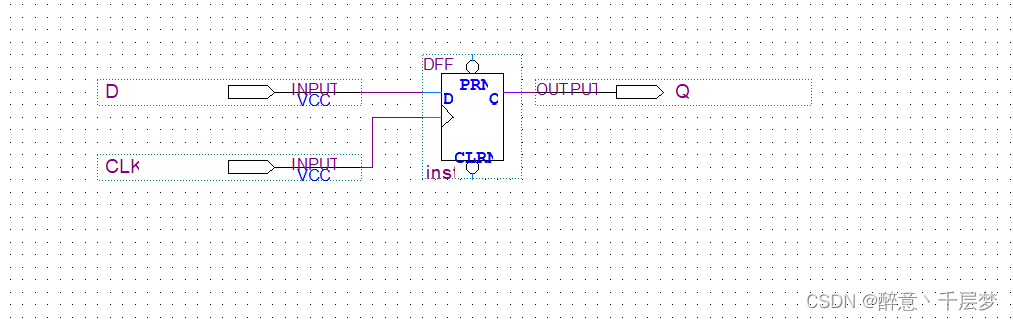

添加两个输入和一个输出完成最后连线

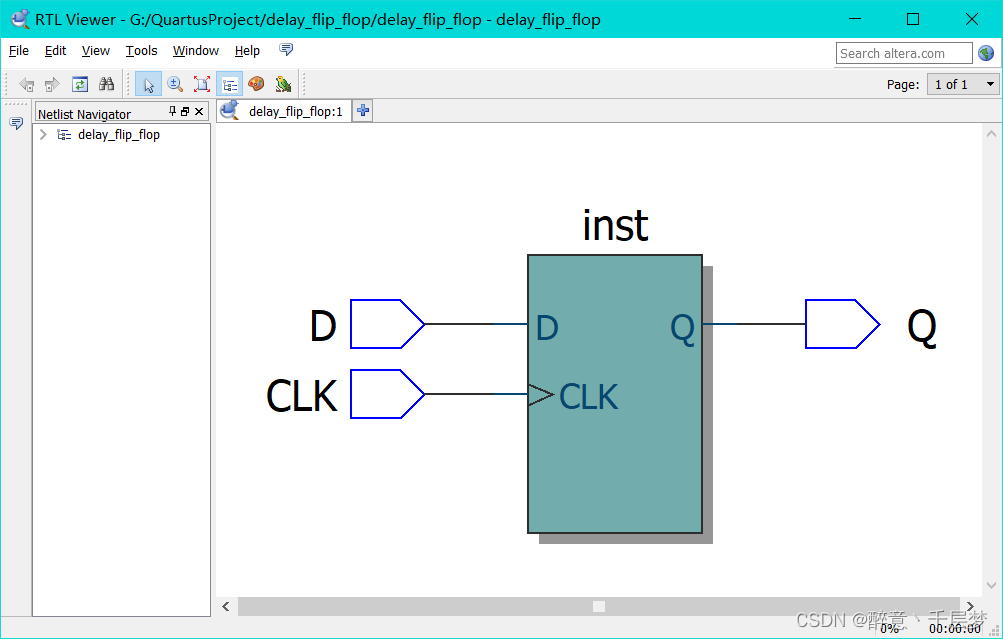

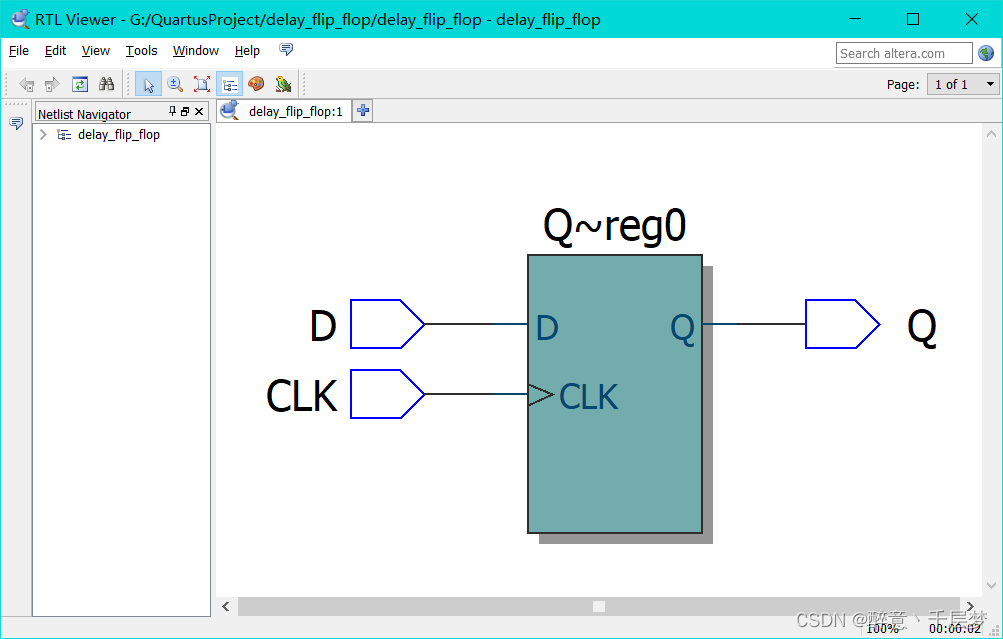

编译后查看电路图

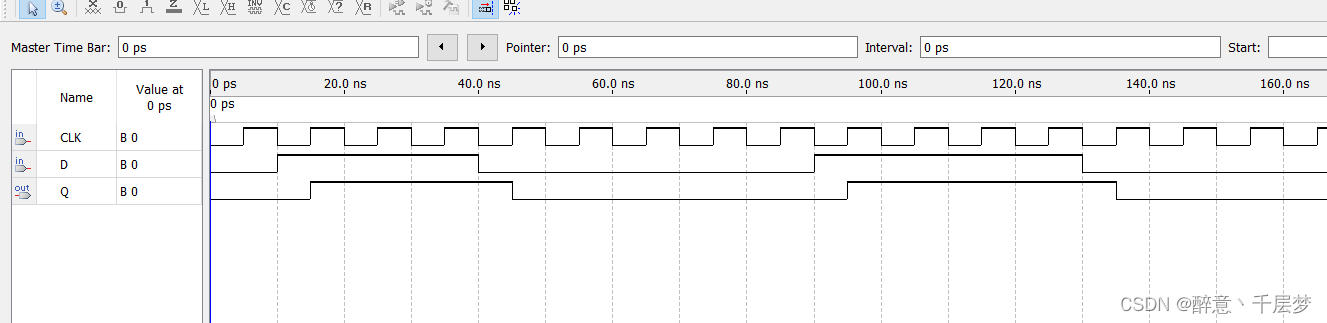

(二)查看仿真波形

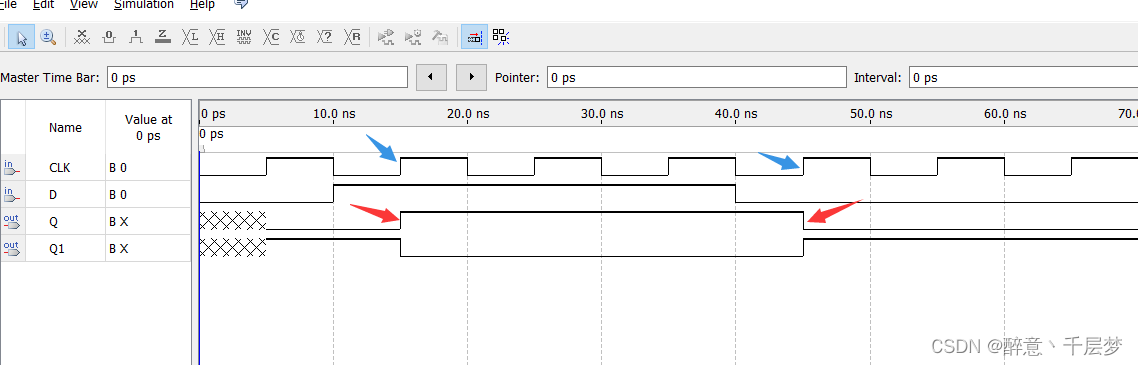

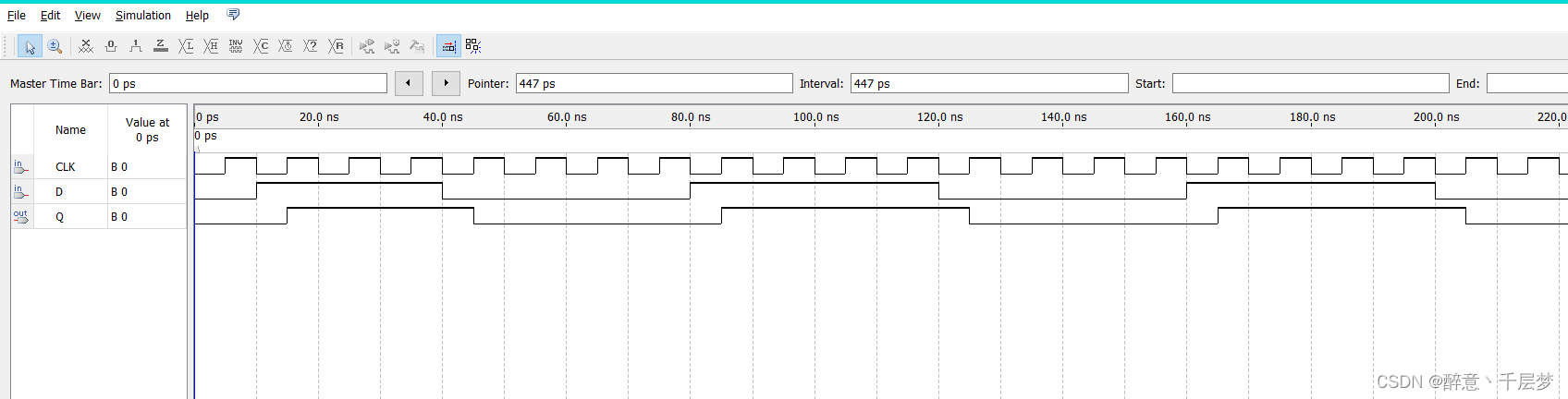

设置好时钟以及D的高低电平

最终效果如图,可以看到Q也是在上升沿随着D的值发送变化

三、Verilog语言

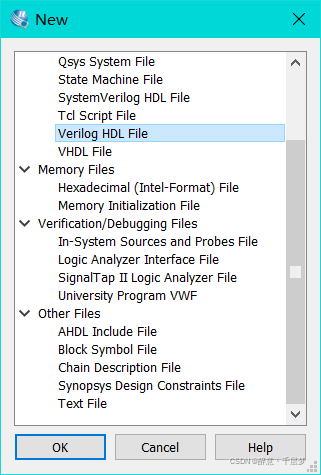

(一)新建Verilog文件

点击file -> new -> Verilog HDL File

写入以下代码

module delay_flip_flop(

D,

CLK,

Q

);

input wire D;

input wire CLK;

output reg Q;

always@(posedge CLK)

begin

begin

Q <= D;

end

end

endmodule

编译后查看电路图

(二) 查看仿真波形

可以看到波形也是一样的情况,在上升沿处Q随着D的值发发生变化

本文详细介绍了如何使用Verilog语言和原理图方式设计并仿真D触发器。从创建项目、绘制D触发器、配置仿真工具到查看仿真波形,每个步骤都有清晰的操作指南。通过三种不同的方法展示了D触发器在上升沿时Q值跟随D值变化的特性,并提供了Verilog代码实现和波形验证。

本文详细介绍了如何使用Verilog语言和原理图方式设计并仿真D触发器。从创建项目、绘制D触发器、配置仿真工具到查看仿真波形,每个步骤都有清晰的操作指南。通过三种不同的方法展示了D触发器在上升沿时Q值跟随D值变化的特性,并提供了Verilog代码实现和波形验证。

3218

3218

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?