一 IC学习方法入门

1 Verilog语法

哪些可综合、哪些不可综合

练习:在VCS上仿真,移植到FPGA看运行结果

2 数字电路

不应该占用很多时间,理解即可,设计中元器件作为整体被调用,内部结构不讨论

FIFO、状态机、信号传输与握手、总线、跨时钟域同步

3 SV

语法掌握到第三章程度即可,产生人以激励和对输出结果进行怕没别的必要语法

4 UVM

5 FPGA

6 时序约束

通过FPGA的EDA软件学习(不通过DC综合器)

二 IC设计/验证公司方向

1 CPU【中央处理器】

= 控制器:【指令寄存器】+【指令译码器】+【操作控制器】()

运算器:【寄存器+高速缓存】 总线

2 GPU

3 SOC

4 ASIC

5 MCU(微控制器-嵌入式)

三 IC设计/验证工具及使用

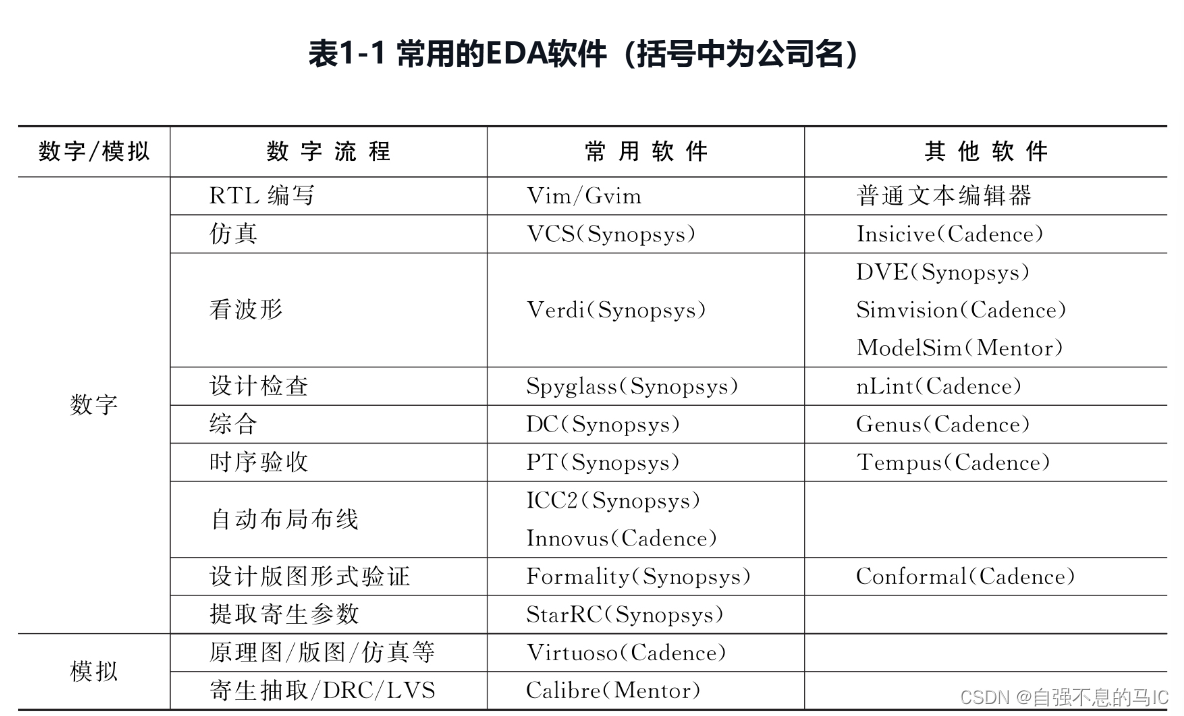

总览:

(1)RTL代码编辑器

Vim

Gvim:vim的图形增强版

备注:正则表达式 (在GVIM中熟练使用)

(2) 仿真

VCS(synopsys)

(3) 波形查看工具

DVE:集成在VCS编辑器中

Veridi(synopsys)

Modelsim(Mentor):主要用于FPGA功能的仿真

(4) 语法检查工具

Spyglass(Altrenta):语法、跨时钟域检查

(5) 综合工具(将RTL转换为实际电路)

DC:Design Compiler(synopsys)

(6)脚本语言:

TCL:DC、PT工具的基础语言

Perl、Python:加分项,会写不足以给设计加分,要熟练才会加分

-------------------------------------------------------------------------------------------------------------------

1 VCS

2 Verdi

verdi步骤:生成fsdb波形、查看fsdb波形、追踪RTL代码进行debug

使用快捷键Ctrl+w或者将信号拖拽到波形里。

通过Find Signal/Instance查找模块和信号,通过Find String查找字符串。

7025

7025

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?