实验目的

实验目的:

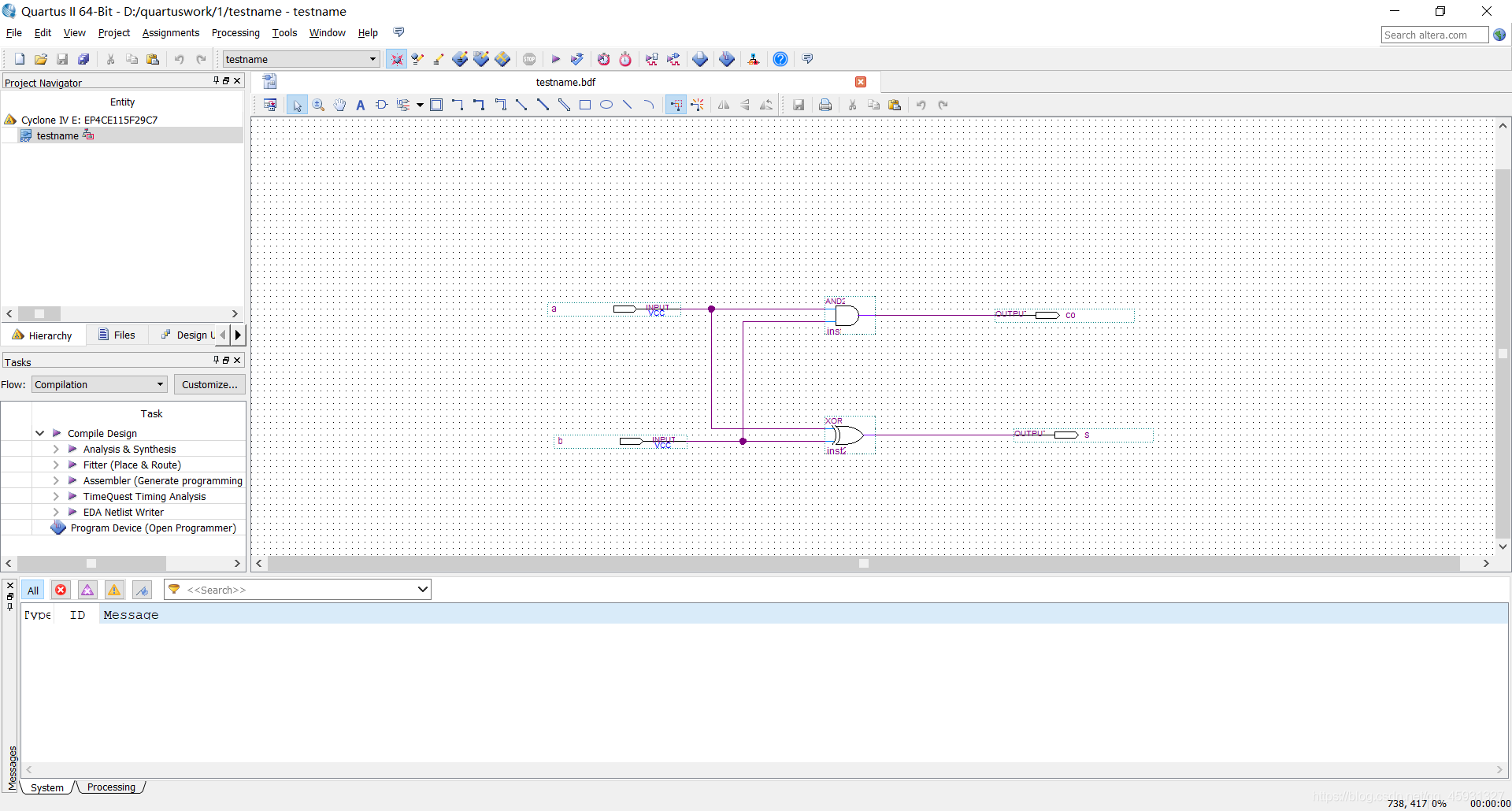

通过1位全加器的详细设计,掌握原理图输入以及Verilog的两种设计方法。软件基于quartusII 13.0版本,开发板基于Intel DE2-115。 1位全加器可以用两个半加器及一个或门连接而成, 因此需要先完成半加器的设计。

实验步骤

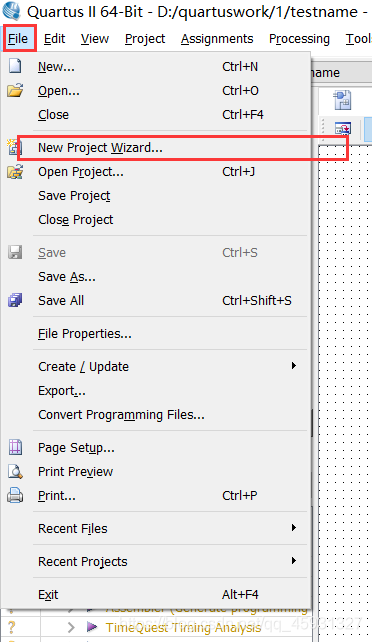

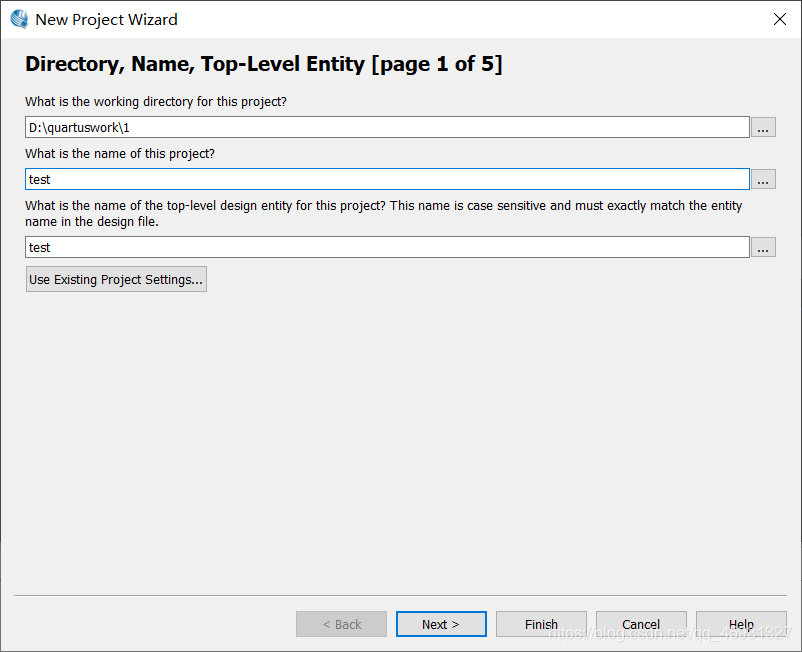

1.新建工程

路径地址存放在可找到的地方,取名无所谓

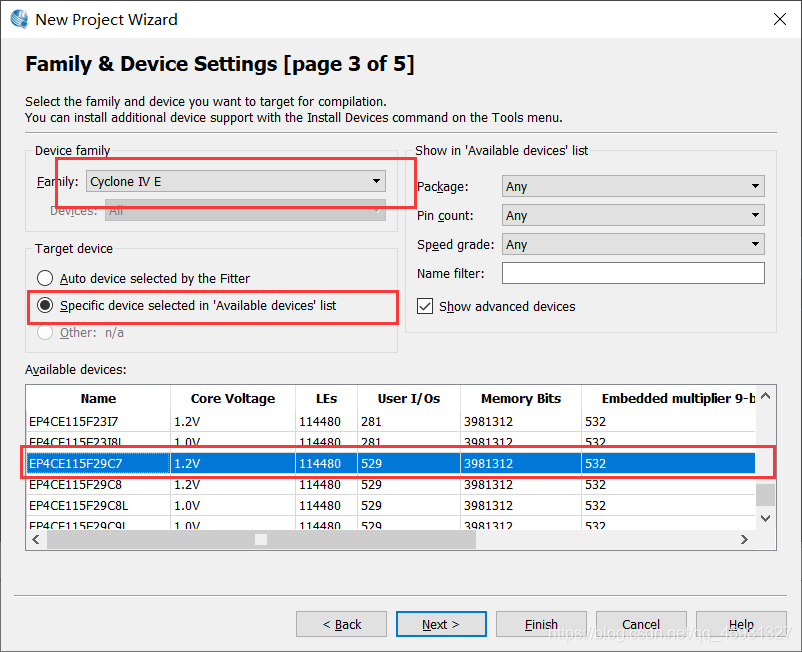

芯片选择与其他设置

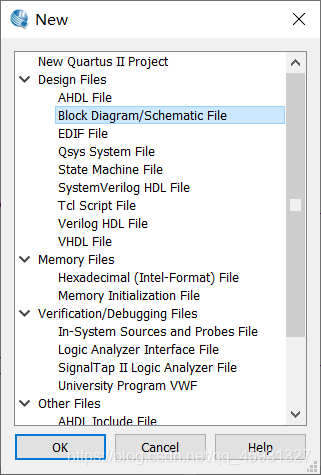

2.工程创建完成后创建新的原理图文件

创建完成原理图文件即可在原理图文件中添加原件,具体步骤不再详述

将设计项目设置成可调用的元件

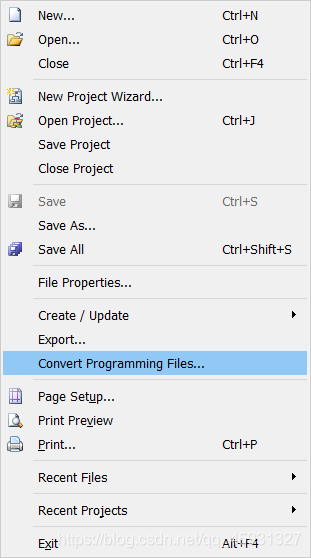

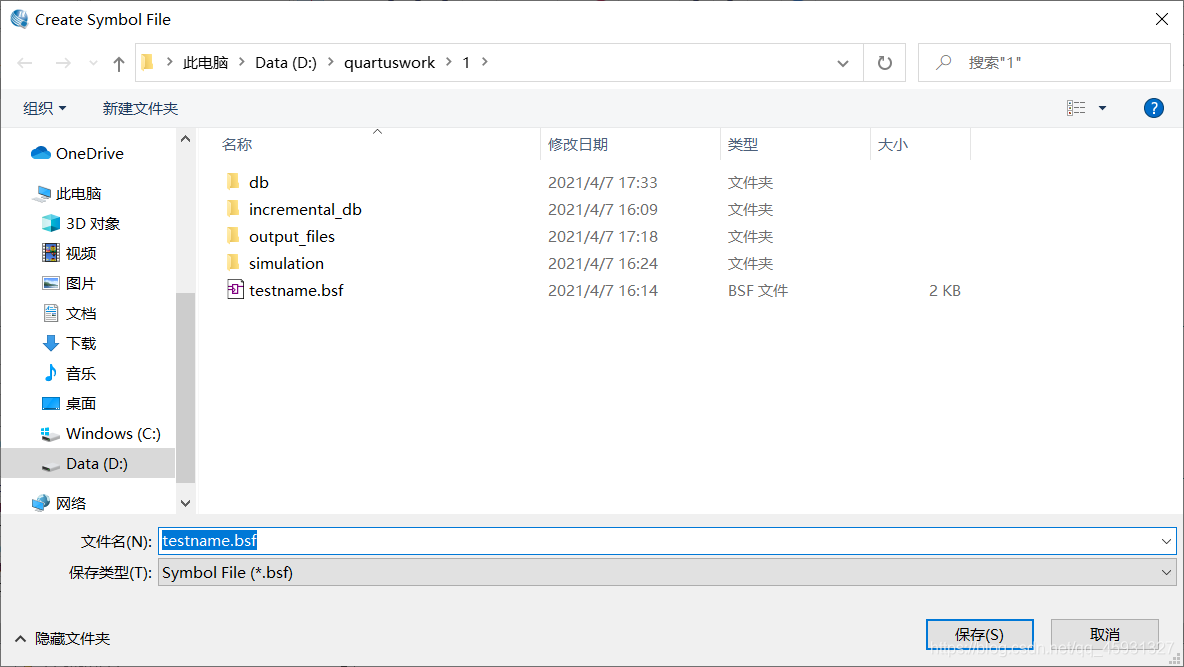

在打开半加器原理图文件half_adder.bdf的情况下,选择菜中File中的Create/Update→Create Symbol Files for Current File项

保存文件即可

3.半加器仿真

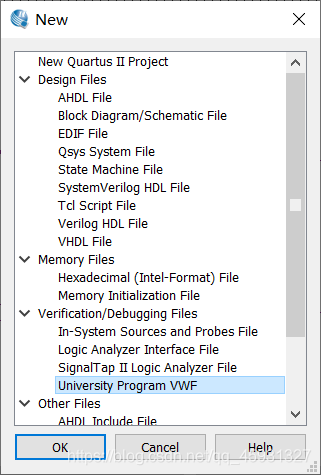

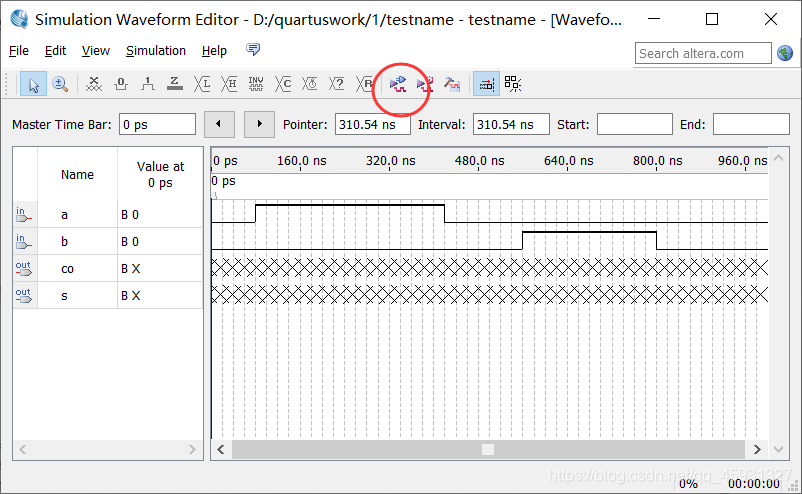

新建波形文件,new一个VMF文件

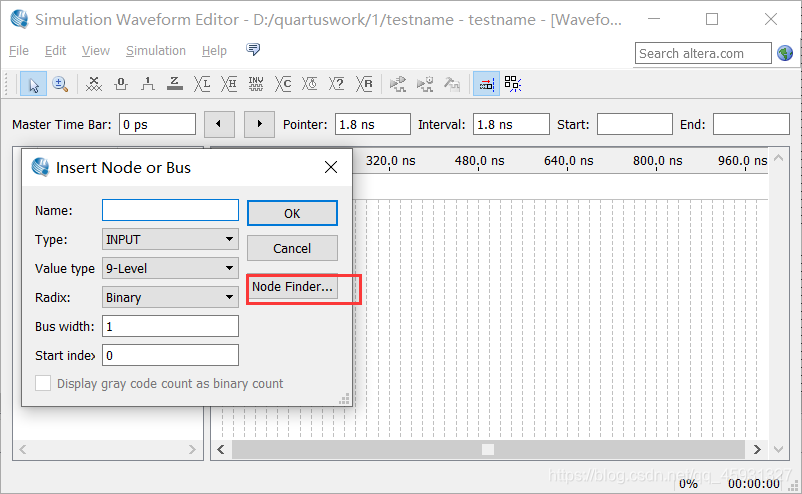

点击空白对话框在波形文件编辑器左端大片空白处双击,出现“insert node or bus"对话框

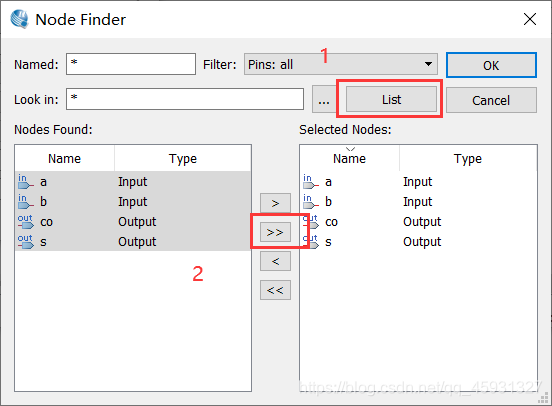

依次点击 Node Finder,LIST ,>>

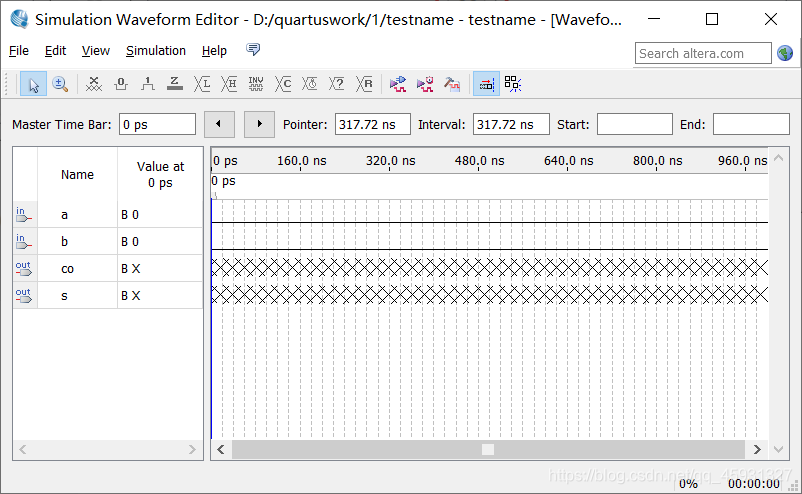

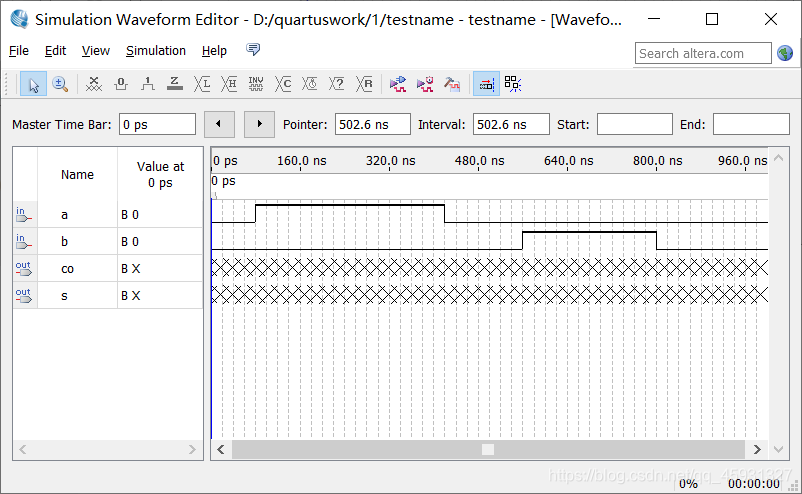

点击OK,出现波形图,设置波形图

保存文件,点击

半加器设置完成。

该实验旨在通过QuartusII13.0和Intel DE2-115开发板,介绍FPGA设计的基础。实验内容包括新建工程,创建半加器原理图文件,使用Verilog进行设计,并进行仿真验证。首先,选择合适的芯片和设置,然后在原理图文件中添加元件。接着,创建半加器符号文件,并进行波形仿真,设置输入和输出波形,观察并验证半加器的正确运行。

该实验旨在通过QuartusII13.0和Intel DE2-115开发板,介绍FPGA设计的基础。实验内容包括新建工程,创建半加器原理图文件,使用Verilog进行设计,并进行仿真验证。首先,选择合适的芯片和设置,然后在原理图文件中添加元件。接着,创建半加器符号文件,并进行波形仿真,设置输入和输出波形,观察并验证半加器的正确运行。

4326

4326

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?