通常的作法是,异常会被划分为多个优先等级,在执行低优先级的异常处理时,更高优先级的异常可以被触发并且执行,这个过程一般被称作***异常嵌套***。异常的优先级可以是可编程的,也可以是固定的。除了优先级的设置,有些异常(包括多数的中断)可以由软件禁止或使能。

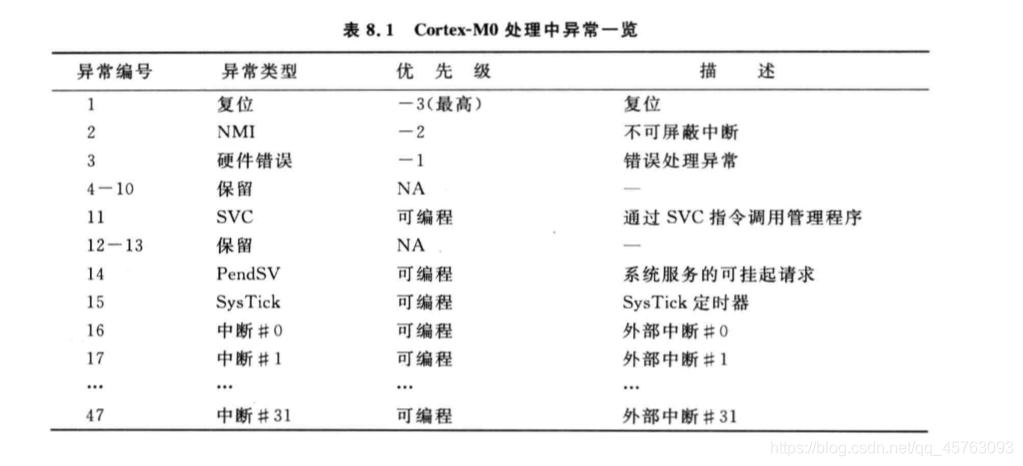

Cortex-M0处理器内置了中断控制器,并且支持最多32个中断请求(IRQ)输入,以及1个不可屏蔽中断(NMI)输人。根据微控制器产品设计的不同,IRQ和NMI可以由外部产生,也可以由片上外设产生。另外,Cortex-M0处理器还支持多个内部异常。Cortex-M0的每个异常源都有一个单独的异常编号,NMI的编号为2,而片上外设和外部中断的则为16~47。 1~15的其他编号,用于处理器内部的系统异常,这个范围内的有些编号还没有使用。

本文介绍Cortex-M0处理器的异常处理机制,包括异常的优先级、嵌套特性,以及最多32个中断请求和1个不可屏蔽中断的支持。详细解释了异常源的编号分配,涵盖外部中断、片上外设中断及内部异常。

本文介绍Cortex-M0处理器的异常处理机制,包括异常的优先级、嵌套特性,以及最多32个中断请求和1个不可屏蔽中断的支持。详细解释了异常源的编号分配,涵盖外部中断、片上外设中断及内部异常。

850

850

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?