设计任务:

使用 FPGA 来构建 MAC 层和 UDP 组包,完成从板卡到主机的数据包传递链路。

项目目的:

通过学习以太网的 UDP 帧协议,完成包的构建和使用网络抓包工具抓包分析数据包是否正确。

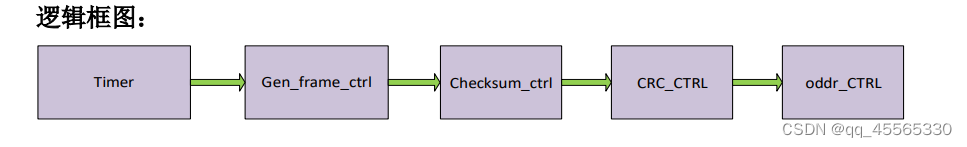

千兆以太网心跳包的产生流程:

第一:根据 Timer 定时器产生触发条件,触发产生心跳包,在一些系统中需要根据需求发送心跳包。

第二:根据以太网协议把 UDP 的基本帧结构构建出来。

第三:UDP 包包含两个校验和需要计算,我们这里是使用硬件进行校验和计算,也就是用 FPGA 逻辑电路搭建一个校验和计算模块。

第四:在帧的尾部添加 4 个字节的 CRC 校验字段,完成整个帧的设计。

第五:通过 ODDR 模块完成 8 比特到 4 比特的转换操作。

校验和填充模块:

把在 gen_frame_ctrl 中组成的基本的成帧数据传输给 checksum_ctrl 模块,在该模块中对 IP_checksum 和 UDP_checksum 进行计算,并填充的千兆以太网成帧数据的对应位置,那么就组成了没有 CRC 校验的千兆以太网 UDP 协议包,将 checksum 模块组成的有 CRC 校验的千兆以太网 UDP 协议包传输到 crc_ctrl 模 块。通过上一节我们已经可以将基本的千兆以太网数据进行组包,但我们在对对应 ip_check_sum 和 udp_check_sum 的位置填充的 00,而在实际过程中 ip_check_sum和udp_check_sum是对ip头部数据和udp包进行校验的一种方式, 通常情况下不会为零的,他们是经过一定的计算计算出来之后填充到协议对应位置用于 PC 机接收校验数据是否正确。那么接下来我们来分析 ip_check_sum 和 udp_check_sum 的计算方式。

Ip_check_sum 计算方式:

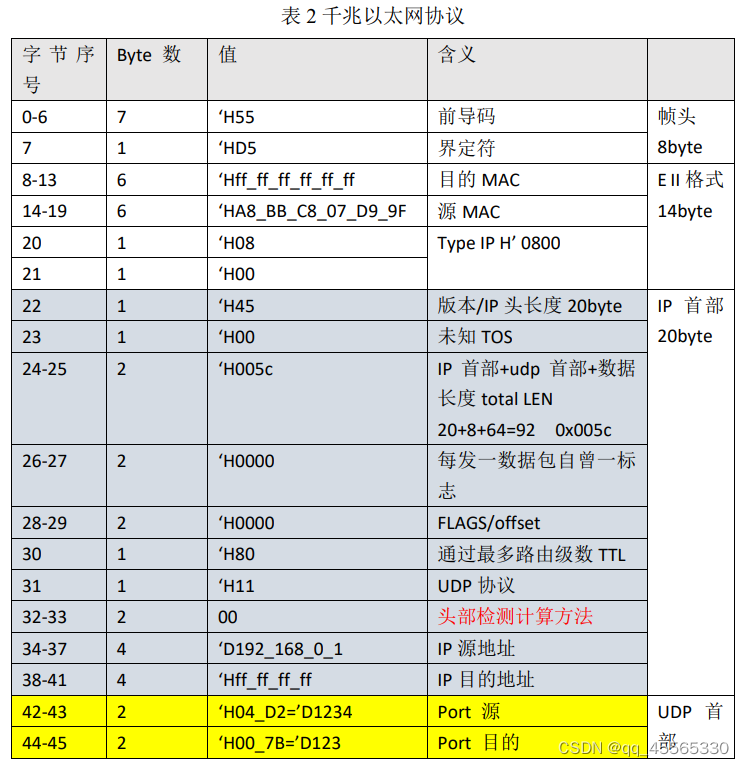

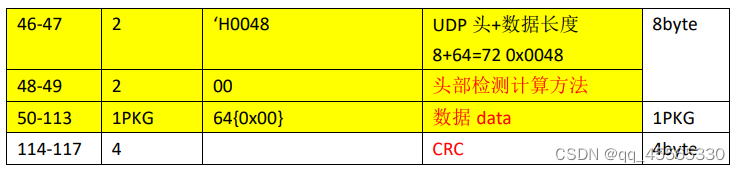

如表 2 ,我们可以先观察一下千兆以太网协议组成。Ip_check_sum 计算就是把 IP 首部 20byte 按 2byte 即 16bit 分开分别相加后,得出来的相加结果如果大于 16’hffff,那么就将相加结果的超出 16’hffff 的部分与相加结果的低 16 位相加,直到最终结果小于 16’hffff 为止。最后把最终小于 16’hffff 的结果取反作为 ip_checksum,即 ip_checksum 的高字节在前,低字节在后,将之前填充在千兆 以太网协议中的 0 进行替换即可。

比如说抓个 IP 数据包,取 IP 数据包 IP首部 20bytes,数据如下: 45 00 00 30 80 4c 40 00 80 06 b5 2e d3 43 11 7b cb 51 15 3d 下面我来计算一下校验和:

(1)将校验和字段置为 0:

将 b5 2e 置为 00 00,即变成: 45 00 00 30 80 4c 40 00 80 06 00 00 d3 43 11 7b cb 51 15 3d

(2)反码求和:

4500+0030+804c+4000+8006+0000+d343+117b+cb51+153d=34ace 将超过 16’hffff 的部分(3)与低 16 位(4ace)上,结果为:3+4ace=4ad1,因为 4ad1 小于 16’hffff,故作为 Ip_checksum 的反码。

(3)取反码特出最终 Ip_checksum:

将 4ad1 取反得:ip_checksum=b52e,即 b52e 就是本包数据最终的 ip_checksum,再将 b52e 填充到对应位置即可。

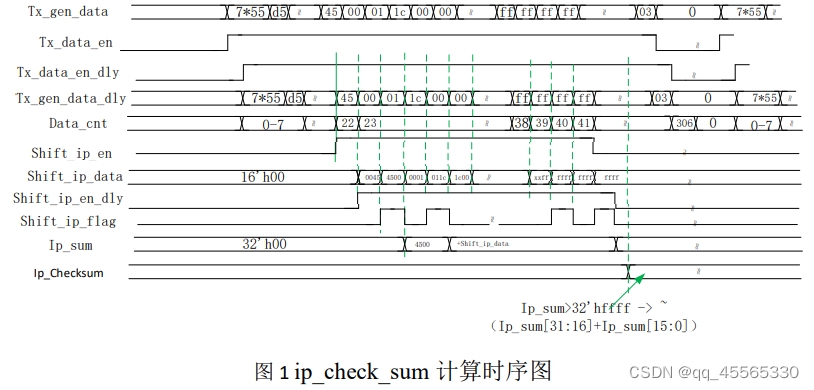

通过以上叙述制出 Ip_checksum 的反码计算方式时序图,如图 1 所示。

通过观察图 1,tx_gen_data 和 tx_data_en 是由上一个模块,即 gen_frame_ctrl 模块传输来的,通过拼接计算得出 20byte 的每两个 bytes 拼接想加的结果 IP_sum,将最终的结果 IP_sum 传输给 Ip_checksum,并判断 Ip_checksum 是否大于 16’hffff,若大于16’hffff,那么就 Ip_checksum 超出16’hffff 的部分与 Ip_checksum 的低16 位相加,直到最终结果小于16’hffff 为止。 该结果就是 Ip_checksum 的反码。

UDP_checksum 计算方式:

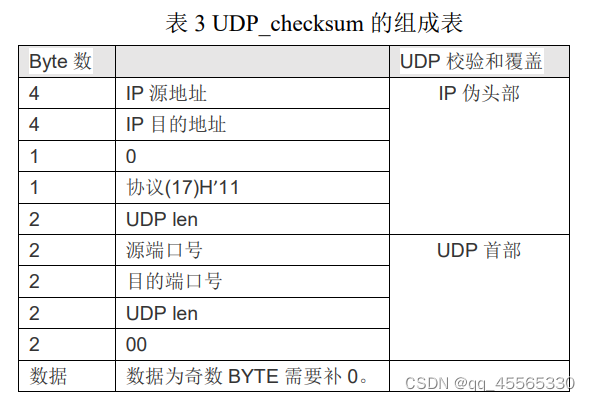

如表 1 ,我们可以先观察一下千兆以太网协议组成。UDP_checksum 计算方式和 ip_checksum 类似,但 UDP_checksum 计算稍微复杂一点,需要加入 IP 伪头部,UDP_checksum 计算方式是将 IP 伪头部、UDP 首部的 8 个 bytes 和数 据包部分按 2byte 即16bit 分开分别相加后,得出来的相加结果如果大于 16’hffff,那么就将相加结果的超出 16’hffff 的部分与相加结果的低 16 位相加,直到最终结果小于 16’hffff 为止。最后把最终小于16’hffff 的结果取反作为 UDP _checksum,即 UDP _checksum 的高字节在前,低字节在后,将之前填充在千兆以太网协议中的 0 进行替换即可。UDP_checksum 的组成如表 3 所示。

通过观察表 3,IP 伪头部包含了 IP 源地址,IP 目的地址,一个字节的 0, 协议号和 UDP_len ,在我

本文详细介绍了如何在FPGA中构建MAC层和UDP包,实现数据包从板卡到主机的传输,并探讨了千兆以太网心跳包的产生流程。重点在于IP和UDP的校验和计算,包括IP_checksum和UDP_checksum的硬件计算模块设计,以及在数据包中填充校验和的策略。通过Verilog代码展示了具体实现过程。

本文详细介绍了如何在FPGA中构建MAC层和UDP包,实现数据包从板卡到主机的传输,并探讨了千兆以太网心跳包的产生流程。重点在于IP和UDP的校验和计算,包括IP_checksum和UDP_checksum的硬件计算模块设计,以及在数据包中填充校验和的策略。通过Verilog代码展示了具体实现过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

892

892

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?