文章目录

1.设计要求

设计并制作一个能够测量正弦波信号频率的电路。

基本要求如下:

(1) 测频范围为0~999Hz,精度为1Hz;

(2) 用数码管显示测频结果;

(3) 设有超量程指示(信号频率≥1kHz时)。

说明:在输入正弦波信号峰值为100mV的情况下进行测试。

2.方案

基于FPGA的控制方案

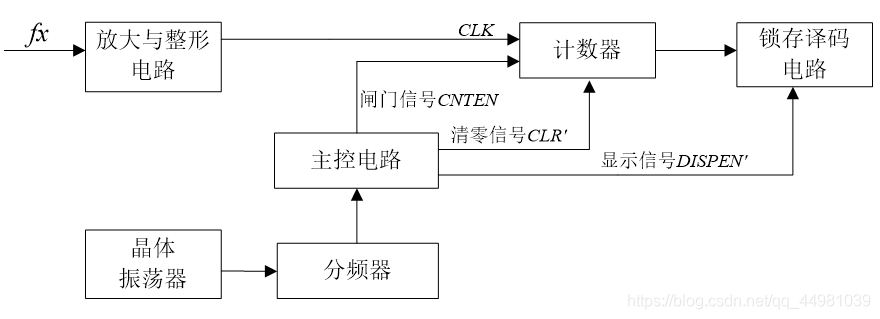

通过软件设计,其中测频控制电路、等精度测量和频率计算电路以及转换译码电路均可以在DE0中实现。标准信号产生电路可通过外部晶振信号(频率为50MHz)提供,待测信号可与扩展接口相连接,故总体设计方案如下图所示。

其中fx为被测信号,CLR’是用于将计数器清零,CNTEN为门控信号,用于控制计数器在单位时间内对CLK进行计数,DISPEN’用于控制锁存译码电路刷新测量结果.

3.单元电路设计

3.1 FPGA部分模块电路代码

由于DE0开发板库中的元器件有限,因此对于库中没有的器件,需要自己写出该器件的功能,并完成调试后封装成电路图,以便在顶层电路中调用。

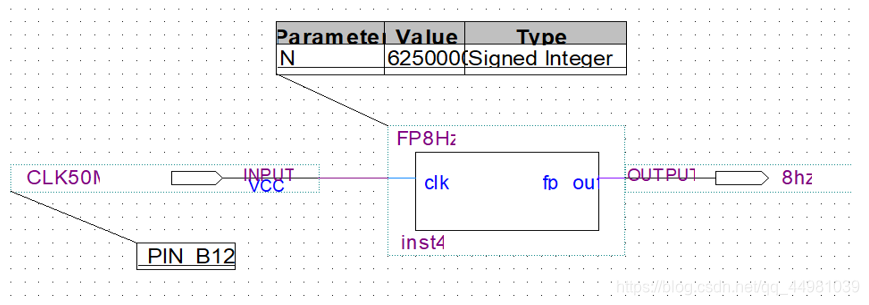

3.1.1分频电路

将DE0开发板的内部50MHz晶振进行分频,使用其8Hz的频率作为标准频率信号产生,具体代码如下:

module FP8Hz(clk,fp_out);

input clk;

output

reg fp_out;

reg [21:0] cnt;

parameter N = 6250000;

always @ (posedge clk)

if ( cnt < N/2-1)

cnt <= cnt + 1'b1;

else

begin

cnt <= 22'b0;

fp_out <= ~fp_out;

end

endmodule

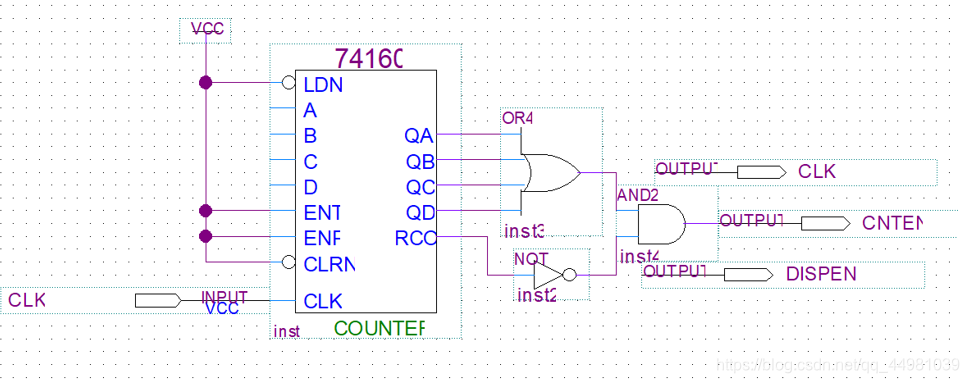

3.1.2主控电路

为设计方便,用十进制计数器74HC160作为主控电路,取时钟脉冲为8Hz,输出用

表示。设测频计数器的清零信号CLK’低电平有效,门控信号CNTEN高电平有效,显示信号DISPEN’低电平有效,其中闸门信号有效时间为1秒。

3.1.3计数电路

电路设计的测频范围为0~9999Hz,则需要4个74HC160级联扩展为一万进制计数器。

本文介绍了基于FPGA的简易频率计设计,包括设计要求、方案选择、单元电路设计(分频、主控、计数、译码显示和超量程指示电路)以及外部电路设计和顶层电路设计。采用Verilog HDL进行编程,并通过DE0开发板进行调试,实现了0~999Hz频率的测量,超量程指示功能以及数码管显示。

本文介绍了基于FPGA的简易频率计设计,包括设计要求、方案选择、单元电路设计(分频、主控、计数、译码显示和超量程指示电路)以及外部电路设计和顶层电路设计。采用Verilog HDL进行编程,并通过DE0开发板进行调试,实现了0~999Hz频率的测量,超量程指示功能以及数码管显示。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5469

5469

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?