To define a clock, we need to provide the following information:

- Clock source: it can be a port of the design, or be a pin of a cell inside the design (typically that is part of a clock generation logic).

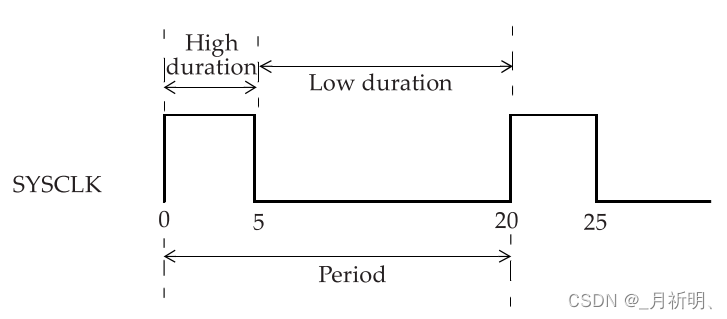

- Period: the time period of the clock.

- Duty cycle: the high duration (positive phase) and the low dura-

tion (negative phase). - Edge times: the times for the rising edge and the falling edge.

Figure shows the basic definitions.

Here is a basic clock specification.

create_clock \

-name SYSCLK \

-period 20 \

-waveform {0 5} \

[get_ports SCLK] The name of the clock is SYSCLK and is defined at the port SCLK. The period of SYSCLK is specified as 20 units - the default time unit is nanoseconds if none has been specified. (In general, the time unit is specified as part of the technology library.) The first argument in the waveform specifies the time at which rising edge occurs and the second argument specifies the time at which the falling edge occurs.

Here is an example of a clock specification with no waveform specification.

create_clock -period 5 [get_ports SCAN_CLK]In this specification, since no -name option is specified, the name of the clock is the same as the name of the port, which is SCAN_CLK. In practice, it is a good idea to keep the clock name the same as the port name.

In addition to the above attributes, one can optionally specify the transition time (slew) at the source of the clock.This is specified using the set_clock_transition specification.

set_clock_transition -rise 0.1 [get_clocks CLK_CONFIG]

set_clock_transition -fall 0.12 [get_clocks CLK_CONFIG] This specification applies only for ideal clocks and is disregarded once the clock trees are built, at which point, actual transition times at the clock pins are used. If a clock is defined on an input port, use the set_input_transition specification to specify the slew on the clock.

文章讲述了如何定义一个时钟,包括时钟源、周期、占空比、边沿时间和波形。示例中展示了创建时钟的命令,如`create_clock`用于指定时钟名称、周期和波形。还提到了可选地设置时钟源的转换时间(摆幅)以及在输入端口上定义时钟时使用`set_input_transitions`来指定时钟摆幅。

文章讲述了如何定义一个时钟,包括时钟源、周期、占空比、边沿时间和波形。示例中展示了创建时钟的命令,如`create_clock`用于指定时钟名称、周期和波形。还提到了可选地设置时钟源的转换时间(摆幅)以及在输入端口上定义时钟时使用`set_input_transitions`来指定时钟摆幅。

1021

1021

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?