AD7606是AD公司的经典ADC芯片,每年为其带来几亿美元的稳定收入,该芯片的主要特点包括:支持8通道模拟输入,200K/秒的采样速度,16位的高精度数字输出,支持±10V和±5V的模拟采集范围,支持并行输出或SPI串行传输接口。因此,不难看出,数字信号的输出,有并行模式和串行模式,并行模式速度快,但是需要的接口资源多,串行模式需要的接口少,但传输和转换速度比并行模式慢。除此之外,可以将AD7606理解成两个BANK,BANK1负责1—4(或1—2,1—3通道),BANK负责5—8(或3—4,4—6通道),也就是说,1—4通道的模拟量,转换成数字量后会在A口输出,而5—8则会在B口依次输出。

AD7606中比较重要的信号接口有如下几个:

-

- RST信号,控制AD7606的复位。

- VDRIVE,决定逻辑电平值,需要和主芯片(DSP、FPGA或STM32等保持一致)。

- RANGE,模拟信号采集范围设置,包括±10V和±5V的模拟采集范围。

- PAR/SER/BYTE_SEL,输出方式选择信号。

- SCLK,SPI传输的时钟。

- CS,SPI传输的片选。

- OS012,表示过采样设置。

- BUSY,ADC输出的信号,表示模数转换完成,可以输出数字信号。

- CONVSTA,B,控制AD7606两个BANK转换开始,可以将这两个信号连在一起做处理,也可以分开控制,具体情况根据项目需求和原理图设计来。

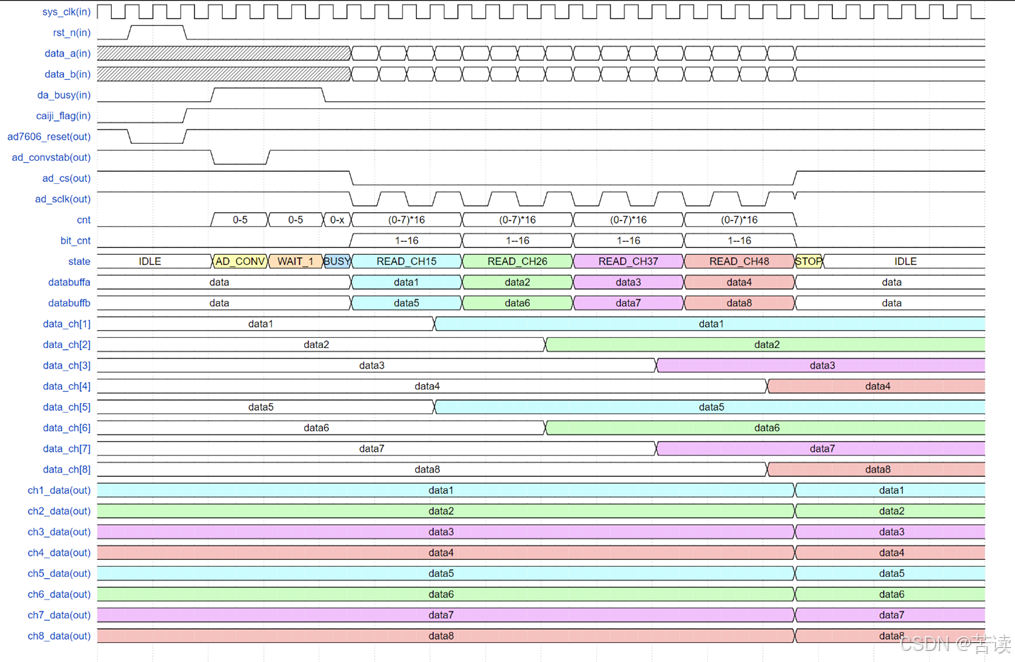

软件上,本项目主要采用串行传输的方式,以节省引脚资源,主要通信流程如下图所示:

首先,由主芯片发送复位信号,复位信号高电平有效,至少保持50ns。

由主机发送转换使能信号convst_ab,转换信号低电平有效,最大不超过0.5ms。

AD7606在收到转换信号后,会进入一段转换时间,在此期间,AD7606会往外输出一个高电平的BUSY信号,高电平拉低,则表示转换完成,可以对外输出,BUSY高电平的持续时间大概在4us——300us不等。这个过程的持续时间主要和是否过采样和过采样倍数有关。

数据接收,BUSY信号拉低后则表示AD7606可以对外输出,此时,需要主机输出片选CS和时钟SCLK,AD7606收到这两个信号后就开始往外传输数据,两个通道会依次往外传输两个BANK的数据,如上如所示。在FPGA的状态里,使用bit_cont来对数据位数进行计数,为1——16位,第一个BANK在状态CH15的最后一个bit_cont来将数据传输到输出data1,进入下一状态后则传输data2的数据,同时BANK2也在处理data5和data6的数据。

在最终的STOP状态,根据传入的参数来判断是否对外输出相关ADC数据。

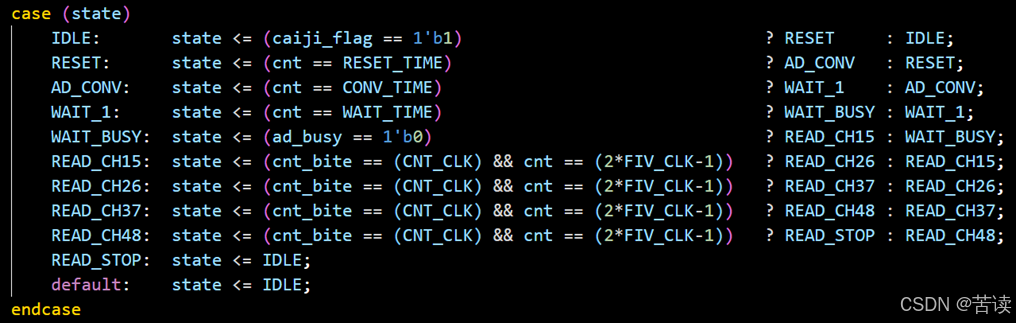

FPGA的状态转移图如下图所示:

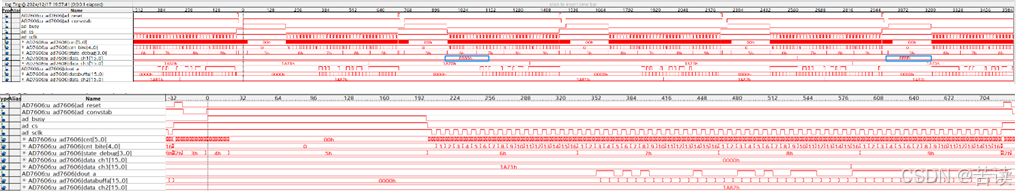

在按照以上思路编写verilog代码,实现了AD7606的数据采集之后,使用逻辑分析仪,清楚地观测到了,采集到的数据(补码形式),且各个信号和我们的时序设计完全一致。

如下图所示。至此,就实现了FPGA对AD7606的串行数据采集。

1959

1959

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?