`timescale 1ns/1ns

module RTL(

input clk,

input rst_n,

input data_in,

output reg data_out

);

reg data_in_reg;

wire data_out_pre;

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) begin

data_in_reg <= 1'b0;

end else begin

data_in_reg <= data_in;

end

end

// 上一拍为低,当前拍为高

assign data_out_pre = data_in && (!data_in_reg);

always @(posedge clk or negedge rst_n)

begin

if(!rst_n) begin

data_out <= 1'b0;

end else begin

data_out <= data_out_pre;

end

end

endmodule

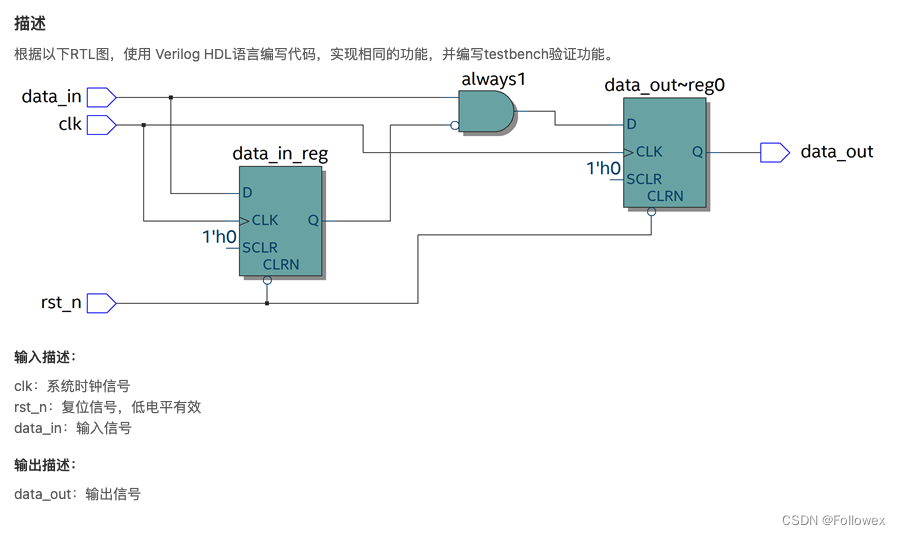

该Verilog代码展示了如何设计一个简单的时序逻辑模块,使用异步置零技术和组合逻辑来存储输入数据并控制输出。模块接收时钟(clk)和复位信号(rst_n),并将输入数据(data_in)存储到寄存器中,根据时钟边沿更新输出(data_out)。

该Verilog代码展示了如何设计一个简单的时序逻辑模块,使用异步置零技术和组合逻辑来存储输入数据并控制输出。模块接收时钟(clk)和复位信号(rst_n),并将输入数据(data_in)存储到寄存器中,根据时钟边沿更新输出(data_out)。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?