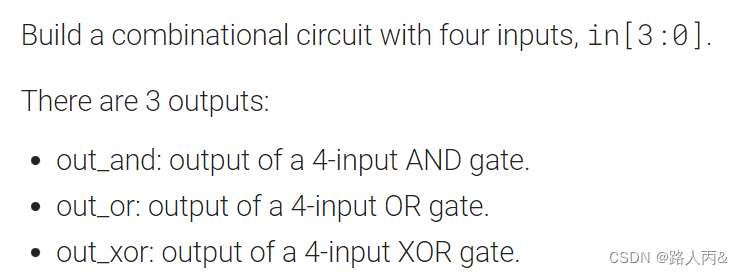

对数组所有位进行运算。一时兴起刷题遇到的,没有见过这样的写法(属于是FPGA超级小白了),查了一下是自身位运算。

module top_module(

input [3:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and=∈

assign out_or=|in;

assign out_xor=^in;

endmodule

除了我们比较常见的位运算外,还有一种位运算叫自身位运算,也是一种比较通用的用法,即放在信号前做运算,同上那个例子:

if (& GPIO_SW_N_delay)

;

else if (| GPIO_SW_N_delay)

;

分别表示当GPIO_SW_N_delay全1和非0的情况。

这篇博客介绍了Verilog中的一种特殊位运算——自身位运算,包括按位与(&)、按位或(|)和按位异或(^)。通过实例展示了如何使用这些运算符来检查输入信号全1、非0的情况,并解释了其在FPGA设计中的应用。

这篇博客介绍了Verilog中的一种特殊位运算——自身位运算,包括按位与(&)、按位或(|)和按位异或(^)。通过实例展示了如何使用这些运算符来检查输入信号全1、非0的情况,并解释了其在FPGA设计中的应用。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?