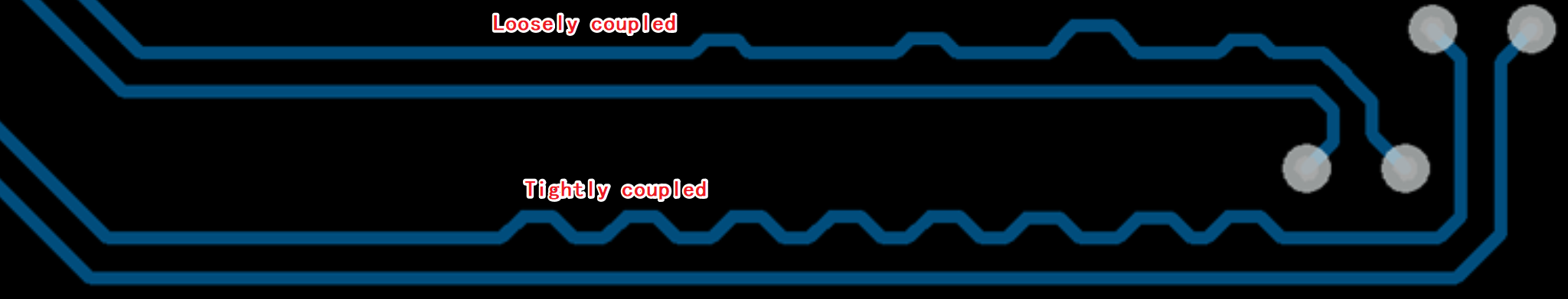

一、松耦合和紧耦合

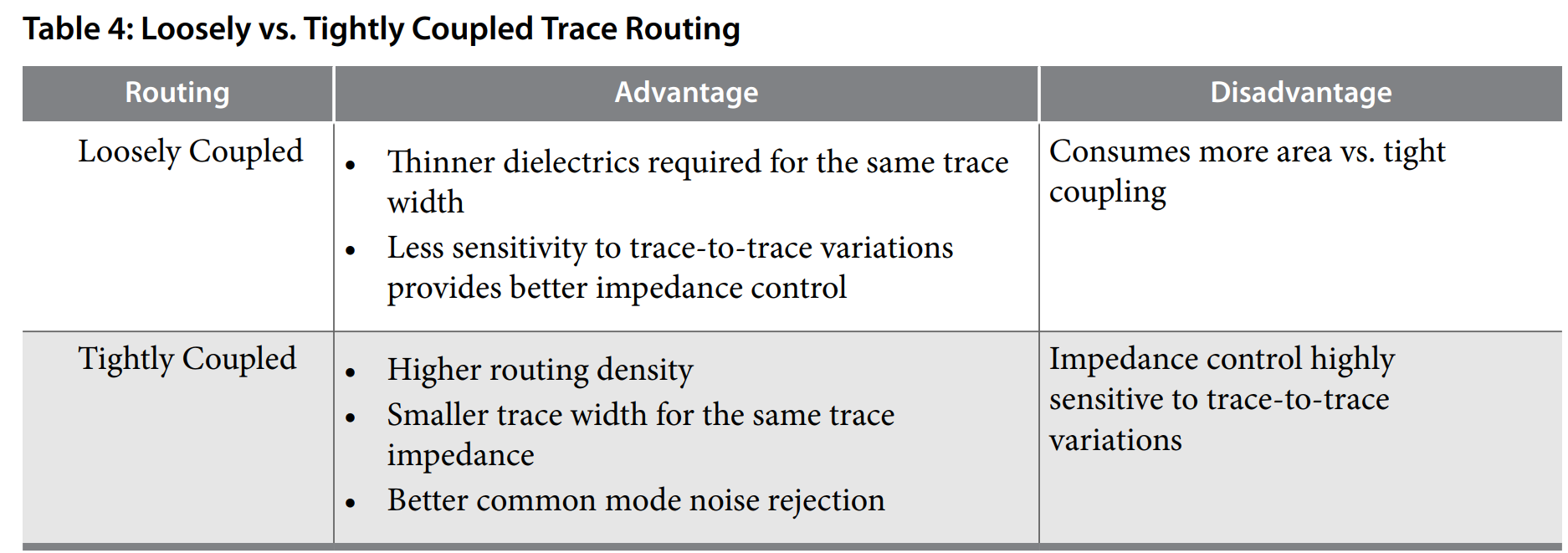

- 松耦合优点是相同走线宽度下电介质更薄,同时对线间距的变化不敏感,提供了更好的阻抗控制;

- 松耦合缺点是需要更大的区域进行绕线;

- 紧耦合优点是更高的布线密度,相同阻抗下走线可以更细,同时具有更好的共模噪声抑制;

- 紧耦合缺点是阻抗随线间距的变化大;

【注】使用松耦合或紧耦合主要是在布线密度和阻抗控制之间权衡

例如,差分对等长通常需要对一个分支进行蛇形处理,以保持P到N的等长。对于松耦合的走线,蛇形线不会急剧改变走线的差分阻抗。而对于紧耦合的走线,走线到走线间距的变化会显著改变标称差分阻抗±10%。

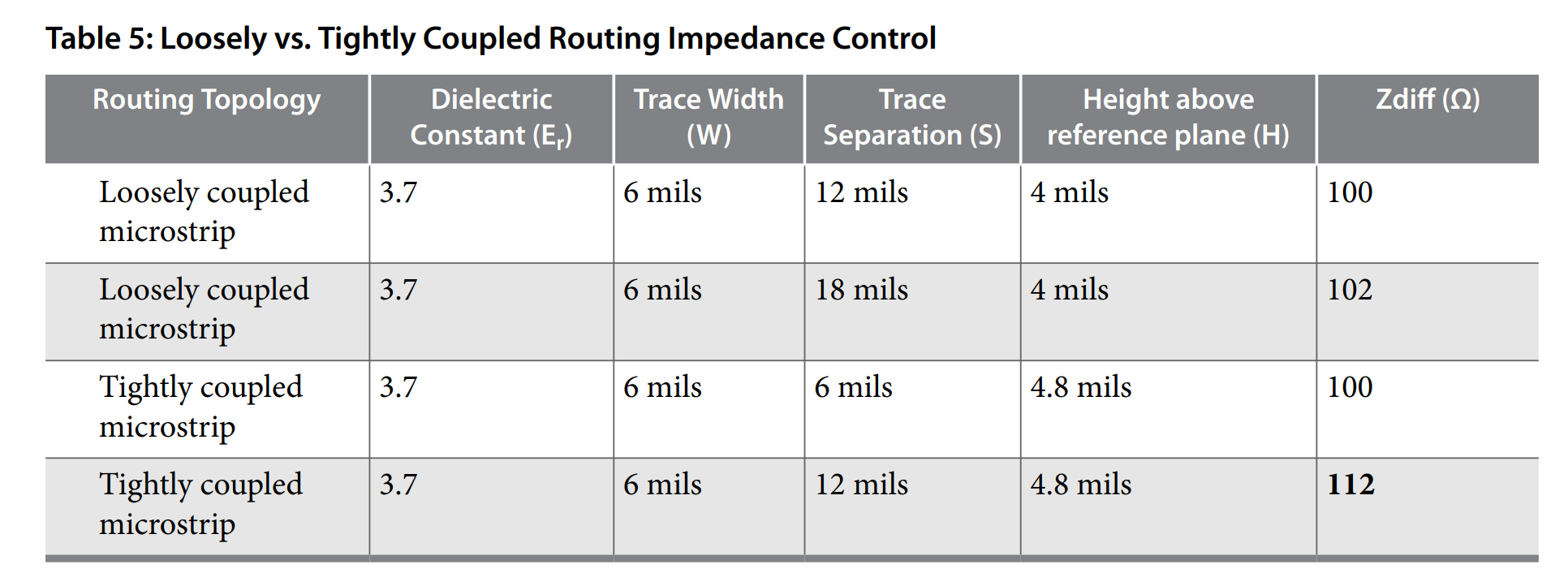

为了减少共模干扰,一般推荐在TX源端进行差分对的等长(deskew),不在RX端进行等长,如下图:

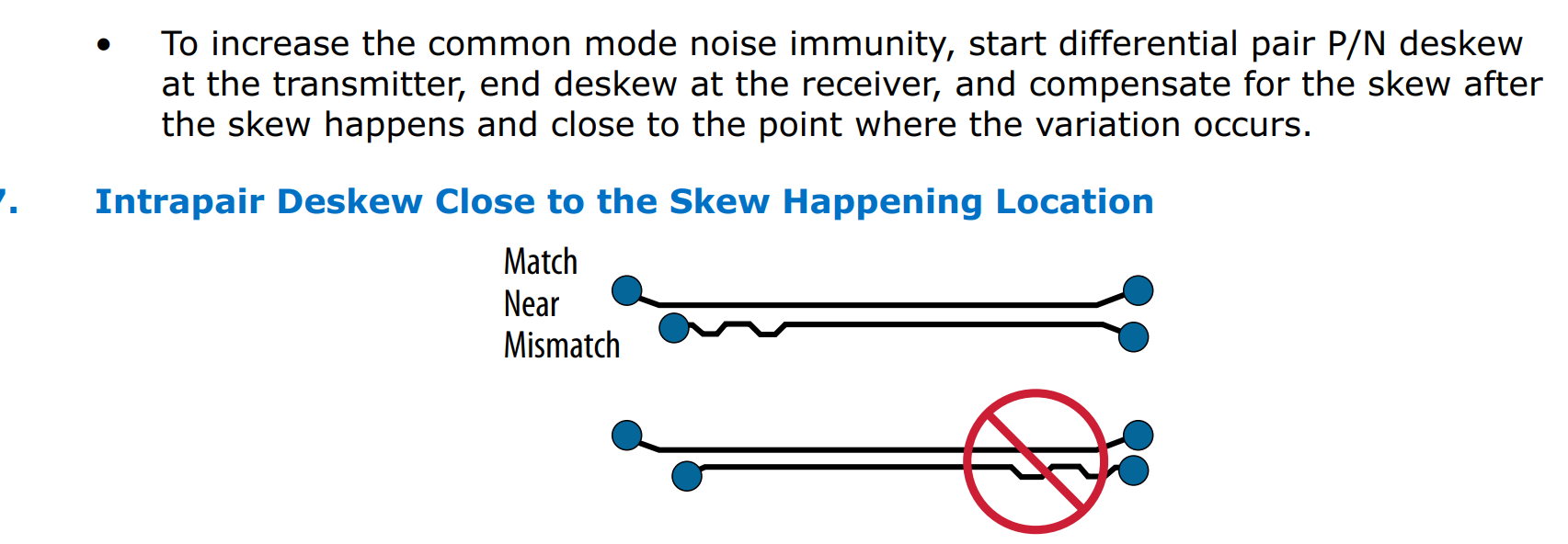

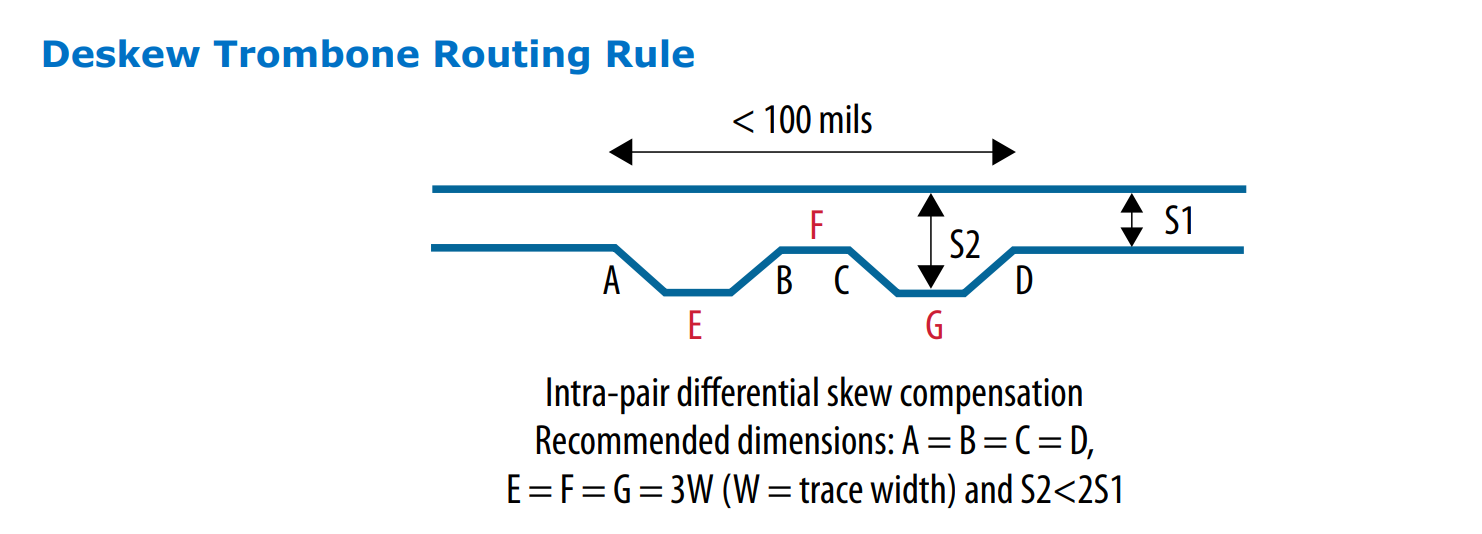

因蛇形走线会给差分阻抗带来不连续,尽量使电长度(electrical length)低于信号上升时间来最小化蛇形走线。一般情况下,保持蛇形布线长度< 100mil,弧度和弯度为45度,如下图:

关于差分信号其余需要注意的地方:

①差分间距一般是走线宽度的1~2倍

②高速差分信号(>10GHz)采用圆弧走线

③在高速差分信号的过孔和焊盘使用泪滴减少阻抗不连续

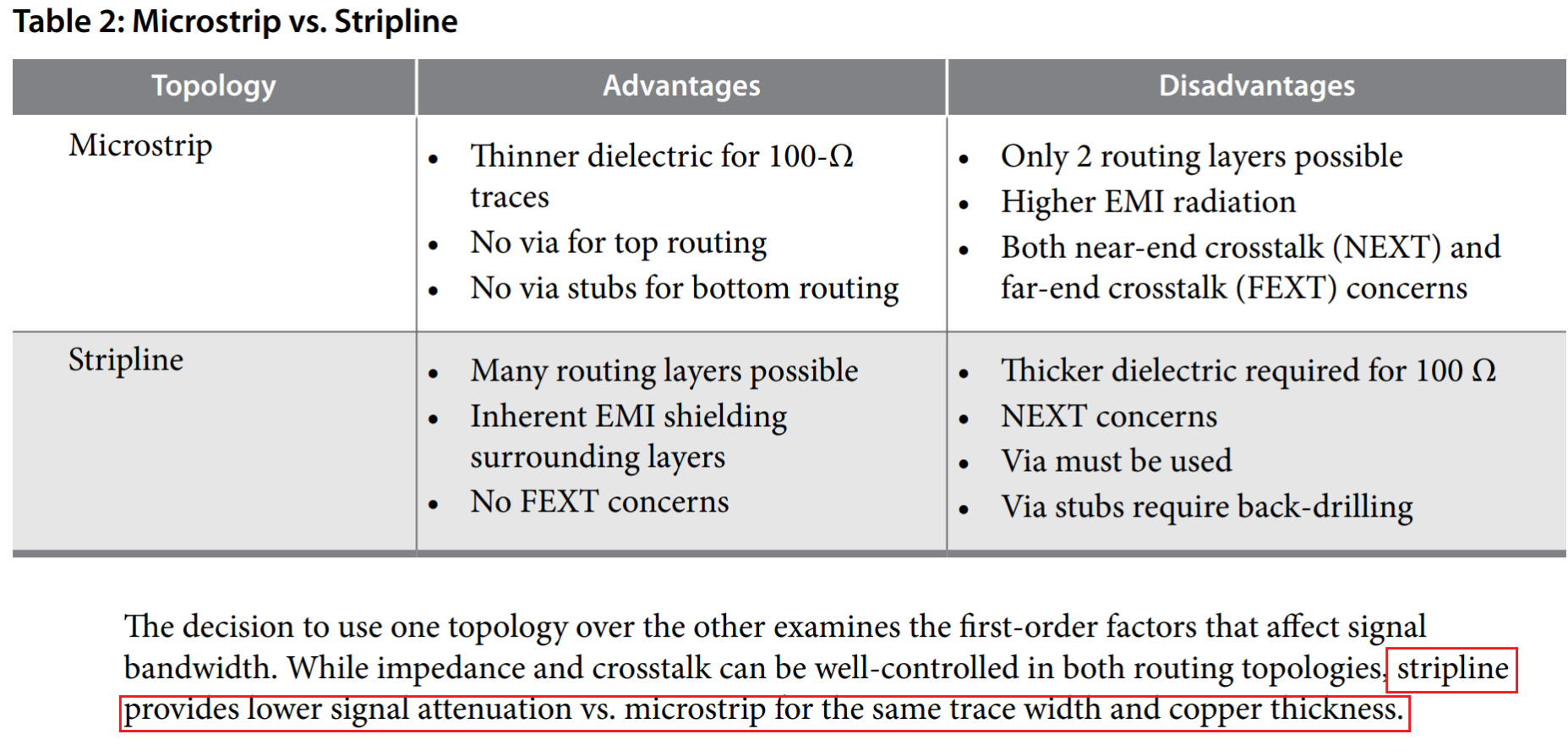

二、微带线和带状线

相同宽度和铜厚的带状线插损小于微带线

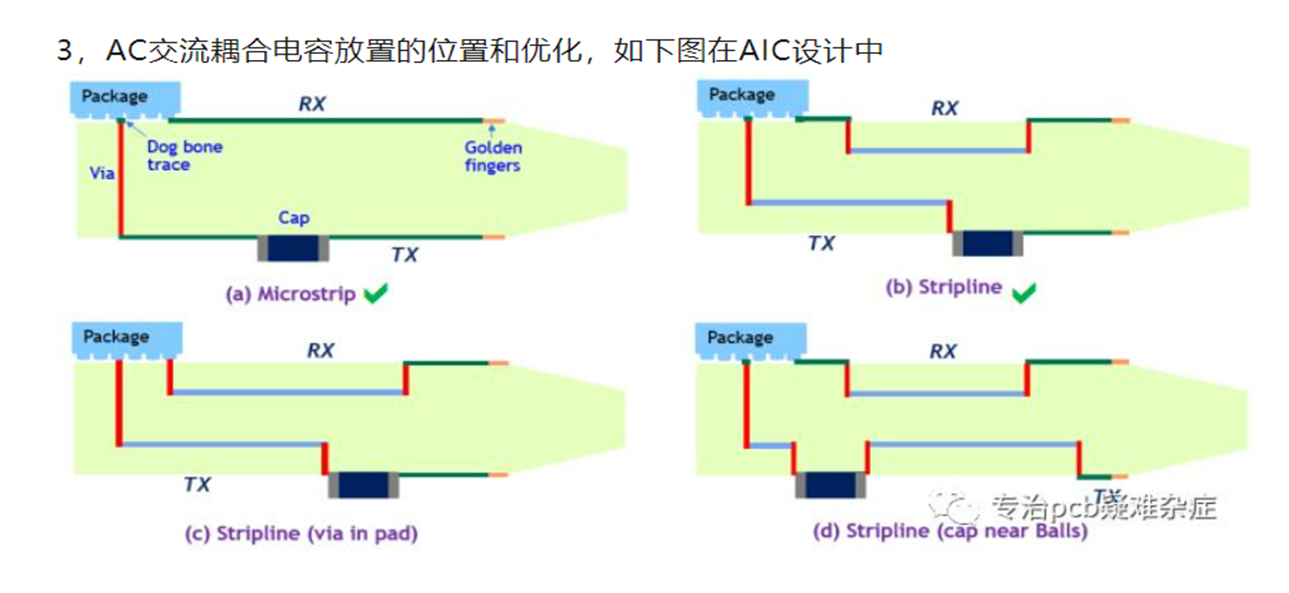

推荐的TX/RX走线方式和隔直电容摆放位置:

三、板材和介电常数

介电常数(在d

本文介绍了PCIe 5.0布局设计中的关键要素,包括松耦合与紧耦合的选择、微带线与带状线的特性、板材和介电常数的影响、走线策略、串扰控制以及AC端接等。通过理解这些要点,能有效提升高速信号的传输质量和系统的整体性能。

本文介绍了PCIe 5.0布局设计中的关键要素,包括松耦合与紧耦合的选择、微带线与带状线的特性、板材和介电常数的影响、走线策略、串扰控制以及AC端接等。通过理解这些要点,能有效提升高速信号的传输质量和系统的整体性能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1855

1855

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?