目录

1.3.2.3 RCiEP(Root Complex Integrated EndPoint) Rules

1.3.4 Root Complex Event Collector

1.4 Hardware/Software Model for Discovery, Configuration and Operation

1.5 PCI Express Layering Overview

1.5.4 各层功能及服务Layer Functions and Services

1. Introduction

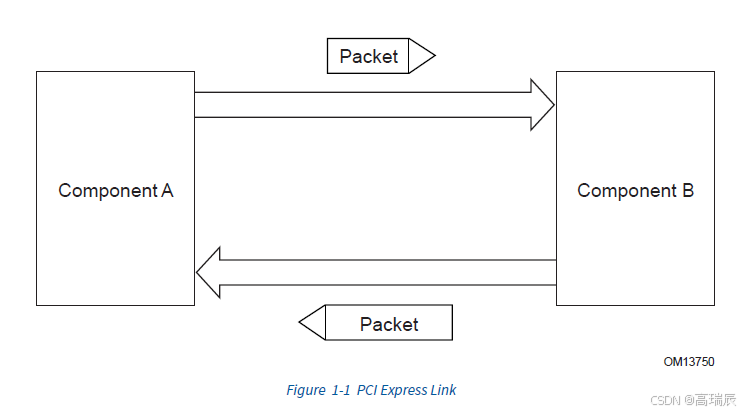

1.2 PCIE链路

链路表示两个组件之间的双单工通信信道。基本PCI Express链路由双单向差分信号对(dual unidirectional differential)组成:图1-1的传输对和接收对。PCI Express链路由第4章中定义的PCIe PHY组成。

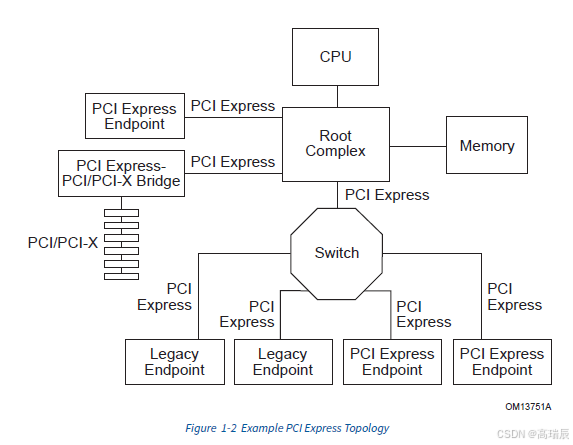

1.3 拓扑逻辑

1.3.1Root Complex (根联合体)

- RC便是IO层次的根,连接CPU/memory SubSys。

- RC可以支持一个或更多的Port,每个接口定义独立的分层结构。每个分层可以由独立EndPoint或者子分层(包含1个或更多的Switch和EndPoint)。

- 分层之间点对点的经过RC的Transaction是可选的,取决于实现。例如:一个implementation可以在RC内包含一个Real or Virtual Switch以软件透明传输方式使能完全的P2P支持。与Switch规则不同,RC被允许在两个分层结构之间的P2P transaction时拆分一个Packet,例如:拆分一个256-byte payload成两个128 bytes payload。产生的新packet内容要遵从本spec内的一般packet格式规定(例如Max_Payload_Size或Read Completion Boundary(RCB))。组件Designer应该知晓将大packet拆分可能导致消极的性能结果,尤其是寻址设备在PCI-E到PCI/PCI-X bridge后的transaction。

- 例外:支持Vendor_Defined信息的P2P routing的RC不允许将Vendor_Defined信息拆分为两个小packet除了128-byte边界(即,除了最后一个packet,其余packet均必须为128Bytes的整数倍)以保持经由PCI-E向PCI/PCI-X Bridge转发信息的能力。

- RC必须支持作为Requester产生配置请求。

- RC被允许支持作为Requester产生IO配置请求。

- RC被允许产生IO请求给80h或84h的任意一个或两个被选中的Root端口,不考虑该Root端口的PCI Bridge IO解码配置;建议这一机制尽在特别需要时启用。

- RC不能作为Completer支持Lock语义。

- RC可以作为Requester支持产生lock请求。

1.3.2 Endpoints

1.3.2.1 传统EP Rules

- 传统EP一定是00h类型的配置空间header的function。

- 传统EP作为Completer一定支持配置请求。

- 传统EP作为Completer可以支持IO请求。

- 传统EP被允许接受IO任意给80h或84h(任一或both)的请求,不需要考虑EP的IO解码配置。

- 传统EP可以产生IO请求。

- 传统EP可以作为Completer支持lock memory语义,如果Legacy软件支持需要。

- 传统EP不能发起lock请求。

- 传统EP可以实现扩展配置空间功能,但这些功能可能被软件忽视。

- 传统EP作为Memory Transaction的Requester时,不要求能够产生4GB或更大的地址。

- 如果中断源需要,传统EP需要支持MSI或MSI-X。如果MSI被实现,传统EP可以被允许支持32或64bits版本的MSI 功能结构消息地址。

- 传统EP被允许支持请求内存资源的32bit的基地址寄存器(Base Address Register,BAR)寻址。

- 传统EP必须出现在RC产生的结构域之一中。

1.3.2.2 PCIE EP Rules

- PCIE EP一定是具有00h类型的配置空间header。

- PCIE EP作为Completer一定支持配置请求。

- PCIE EP不得依赖于操作系统的通过BAR声明的IO资源分配。

- PCIE EP不能产生IO请求。

- PCIE EP不能作为Completer支持Lock请求,也不能作为Requester产生Lock请求。

- PCIE 软件驱动和应用在访问PCIE EP时不得使用Lock语义。

- PCIE EP作为Memory Transaction的Requester时,需要能够产生大于4GB的寻址。

- 如果中断源需要,PCIE EP需要支持任意的MSI或MSI-X,如果MSI被实现,PCIE EP必须支持MSI功能结构的64-bit的消息地址版本。

- PCIE EP经由BAR申请内存资源必须设置BAR的Prefetchable bit,除非范围包含读取副作用的地址或该function不允许写入合并的地址

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1898

1898

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?