Cache 一般设计

Cache 一般设计

Cache 的原理

- 时间相关性

- 最近使用到的 cache line 在接下来使用到的概率更高

- 存放在 cache 中的数据使用概率大

- 空间相关性

- 最近使用到的数据在接下来使用到的概率更高

- 一条 cache line 中的数据使用概率大

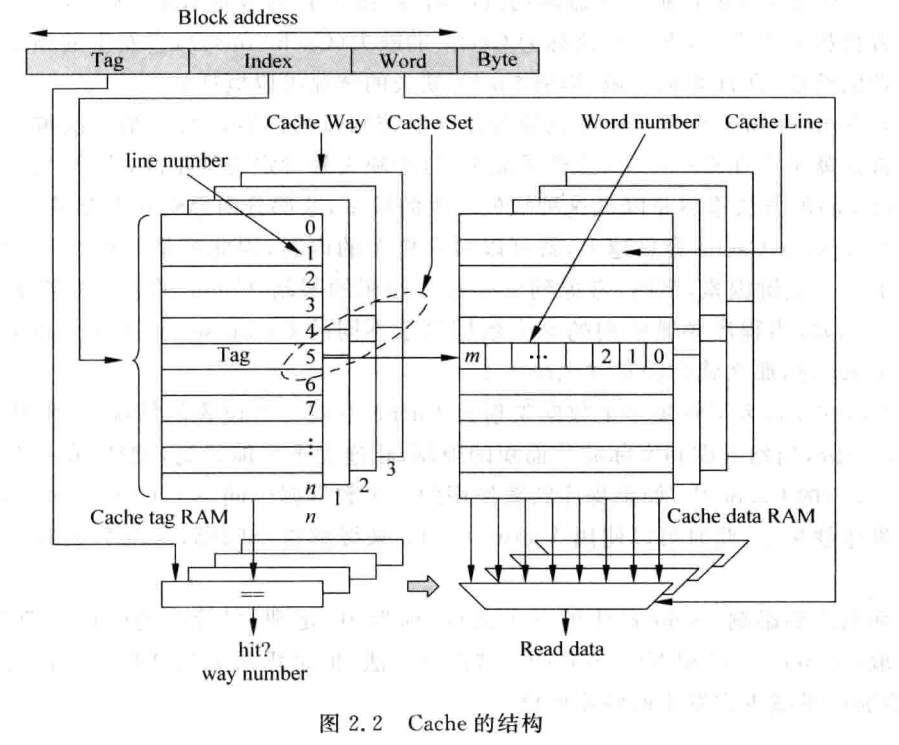

Cache 结构如下

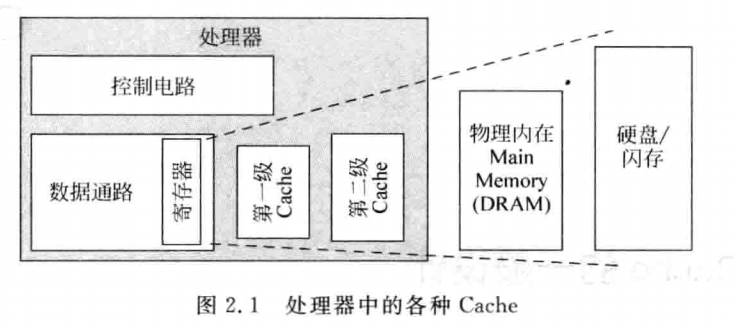

假设 2GHz 的 4-way 超标量处理器,执行 1 条指令时间为 1.25*10^(-10) s

访问 DRAM 一次 100ns,可以执行 800 条指令,由此 L2 的命中率很关键

L1 和 L2 (MB 级别)通常单核私有,L3 多核共有

多端口(多个 Load Store 读写端口)设计的缺点:占用硅片面积、延迟较大

端口的组成部分:地址解码器、多路选择器、比较器等

容量小的部件(寄存器堆):其端口所需要的资源较少,所以新增端口开销不大

容量大的部件( 缓存 ):其端口所需要的资源较大,所以新增端口开销大

Data 部分和 Tag 部分,data 部分保存连续地址的数据中,Tag 存储连续数据的公共地址。

1 个 Tag 和对应的所有数据中称为 cache line

Data :保存一片连续地址的数据

Tag: 存储连续数据的公共地址

Cache Line:一个 Tag 和对应的所有数据组成的一行

数据块:Cache line 中的数据部分

Cache Set:同一个地址找到的多个 cache Line

不同的 cache way 之间的关系:存储不同的 data 和 tag

不同的 cache set 之间的关系:所有 way 里,相同 index,不同 tag

Line number 之间的关系:不同 index 对应的 tag

Tag 和 data 之间的关系:tag + index 索引到 data

word number :确定 index 和 tag 之后,根据 word 选择确定索引的字节数

对于物理内存的数据来说

直接映射:Cache 中只有一个地方可以容纳

组相联:Cache 中多个地方可以存放一个数据

全相联:Cache 中任何地方都可以存放该数据

TLB 和 Victim Cache 采用全相联

I-Cache 和 D-Cache 采用组相联

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

797

797

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?