下载固件gd32e230c8t6固件官方下载(需登录)

或

蓝奏云

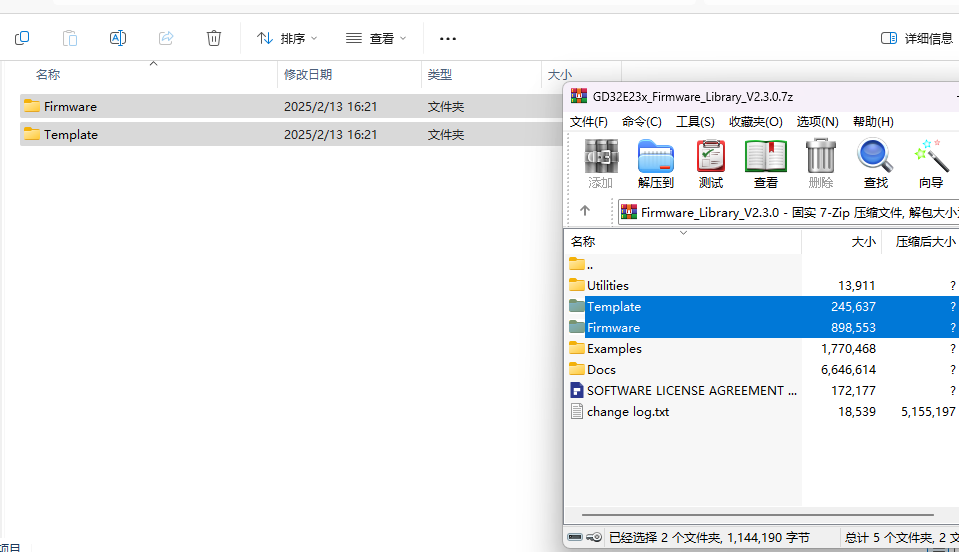

新建一个文件夹,把固件压缩包里的里的Firmware和Template拖进去

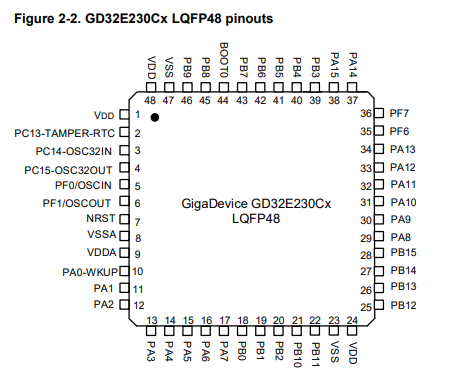

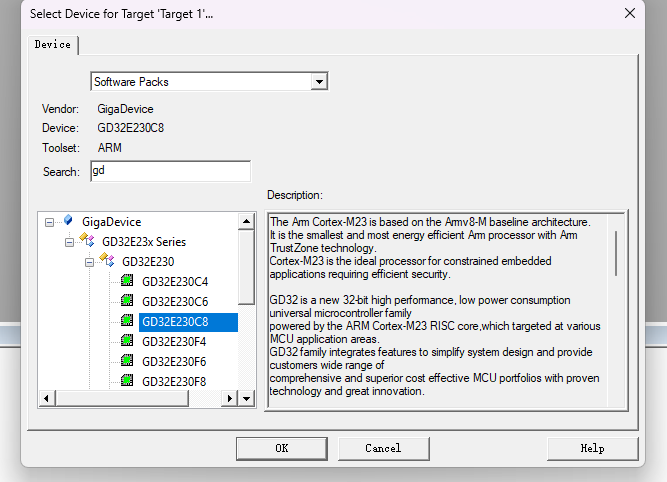

keil新建gd32e230c8工程

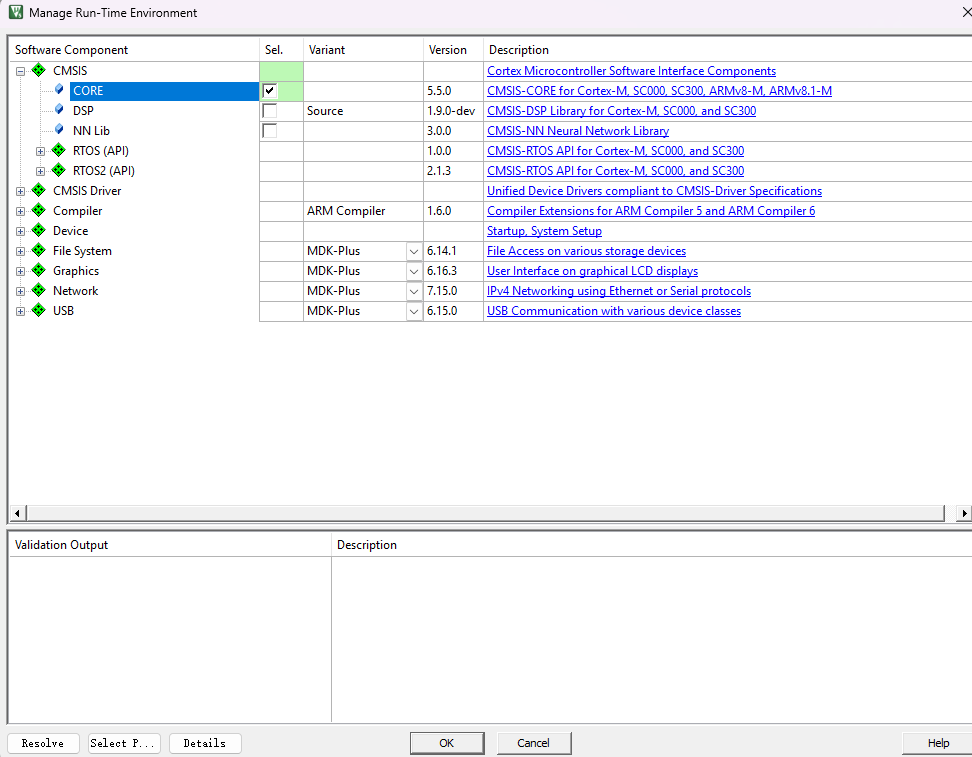

必须勾选CMSIS-CORE

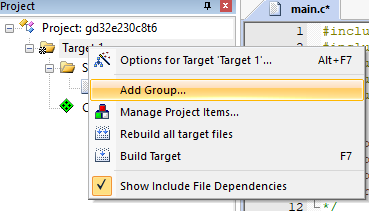

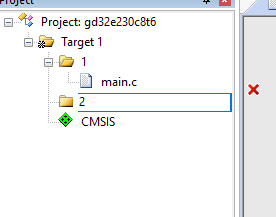

新建一个文件夹,双击任意改名

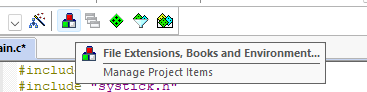

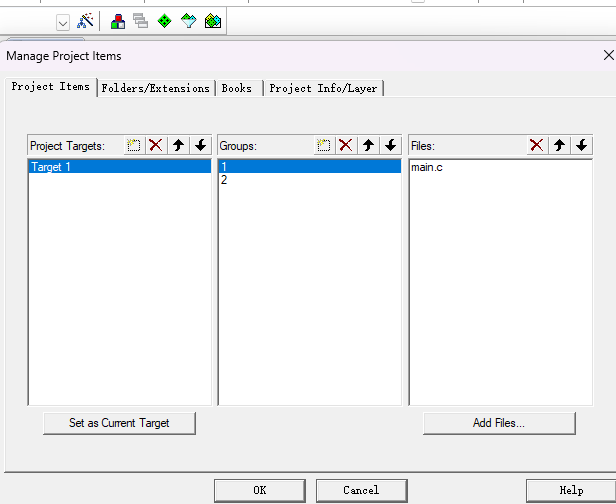

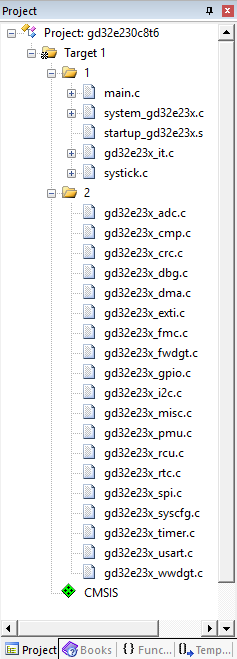

点击manage project items导入.c和.s文件

文件夹1

Template\main.c

Template\gd32e23x_it.c

Template\systick.c

Firmware\CMSIS\GD\GD32E23x\Source\ARM\startup_gd32e23x.s

Firmware\CMSIS\GD\GD32E23x\Source\system_gd32e23x.c

文件夹2

Firmware\GD32E23x_standard_peripheral\Source-所有的.c文件

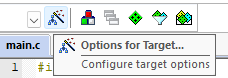

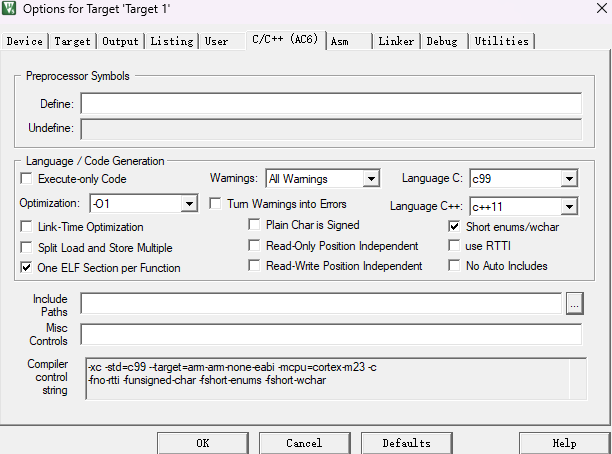

再导入.h文件,打开options for target----C/C++(AC6)—include Paths

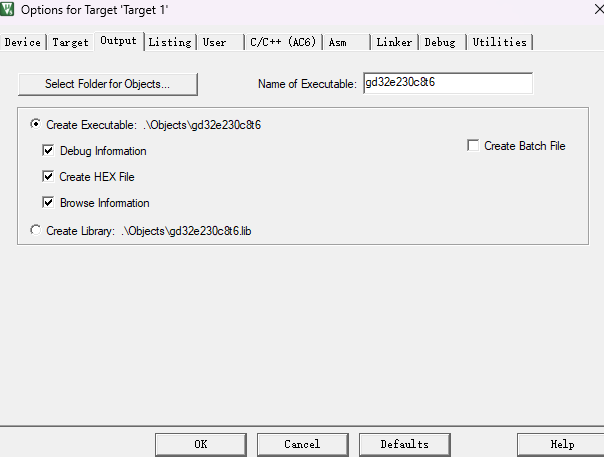

output勾选Create HEX File

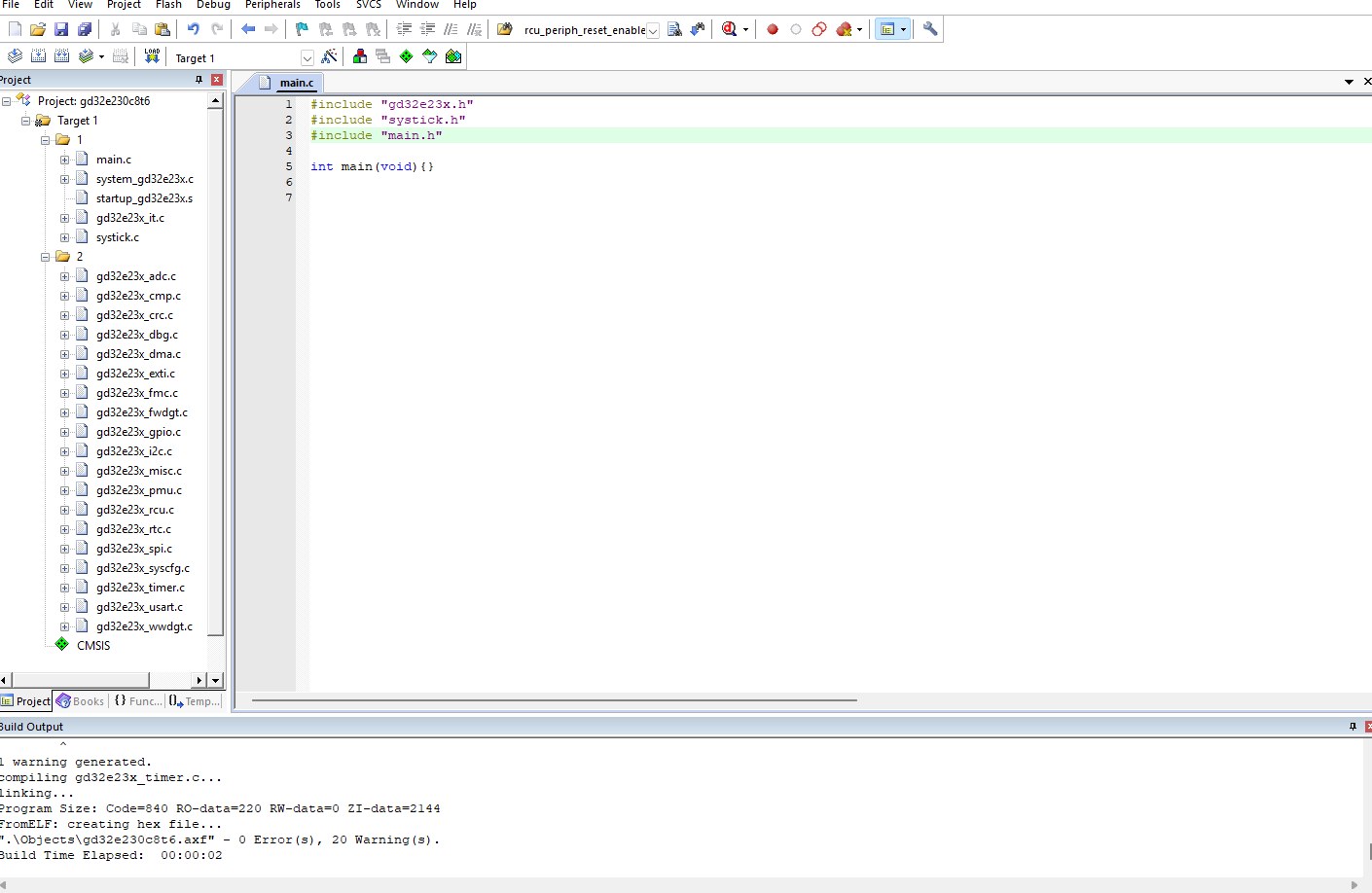

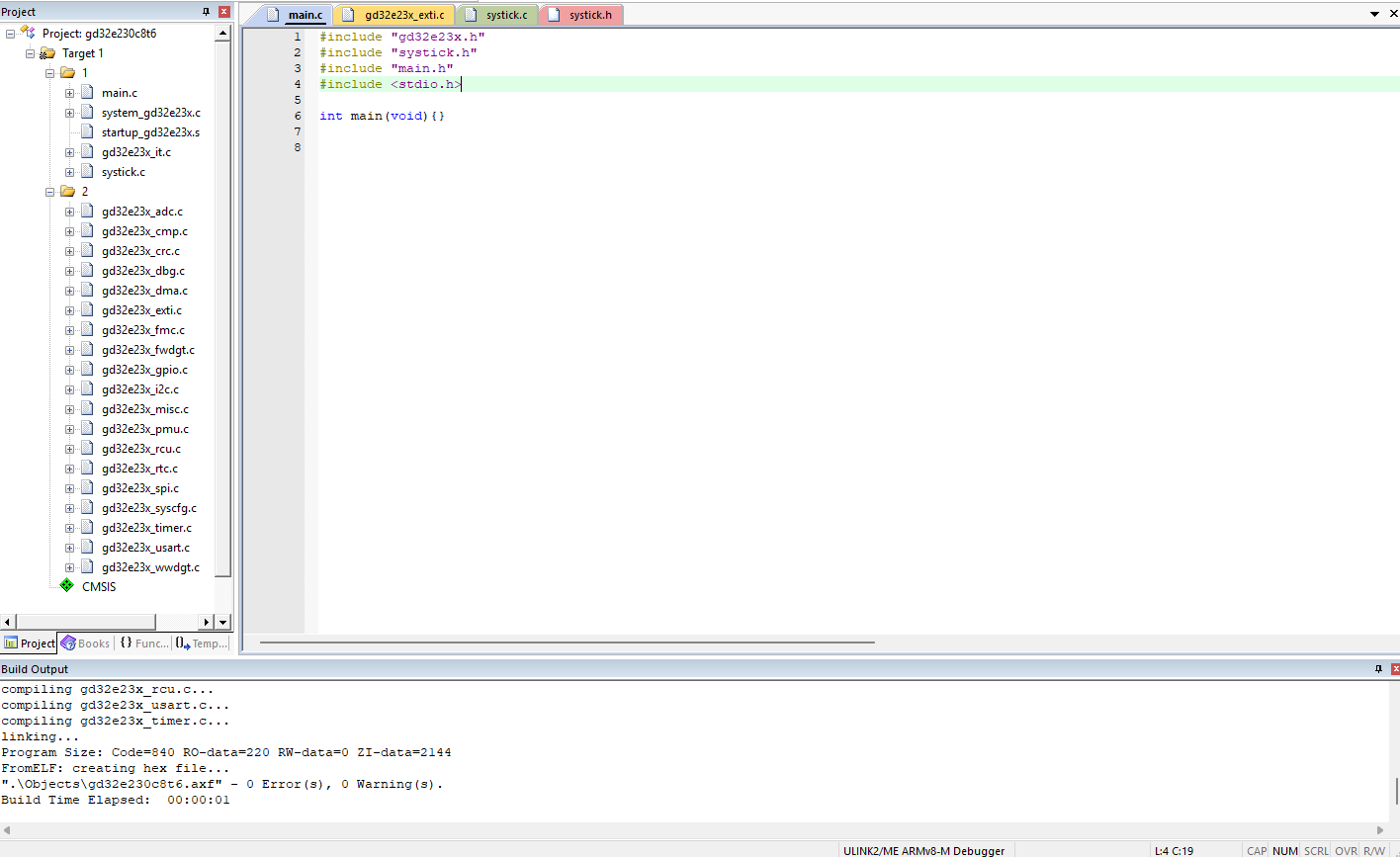

修改main.c

#include "gd32e23x.h"

#include "systick.h"

#include "main.h"

int main(void){}

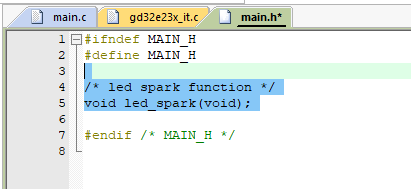

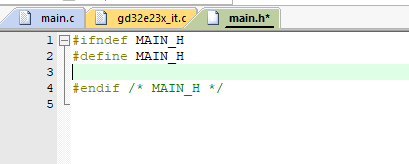

修改main.h,删除选中内容保存

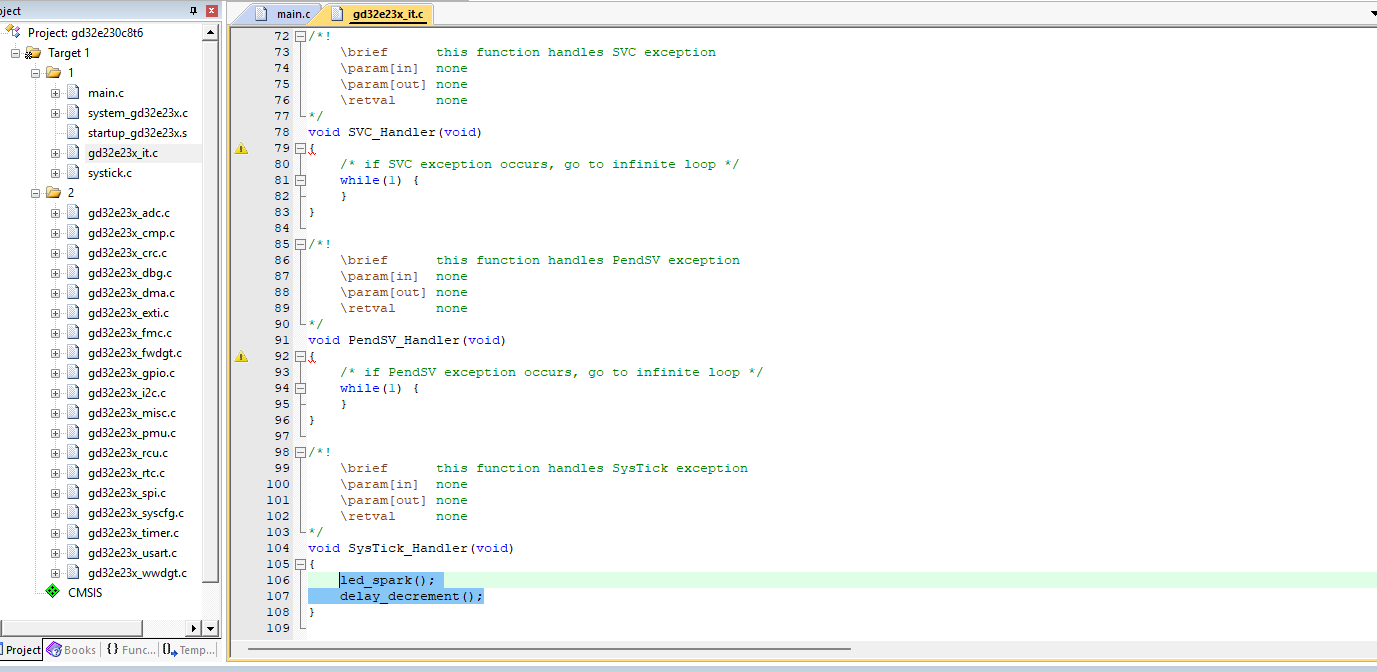

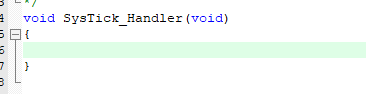

修改gd32e23x_it.c,删除选中内容保存

编译,无报错,有警告

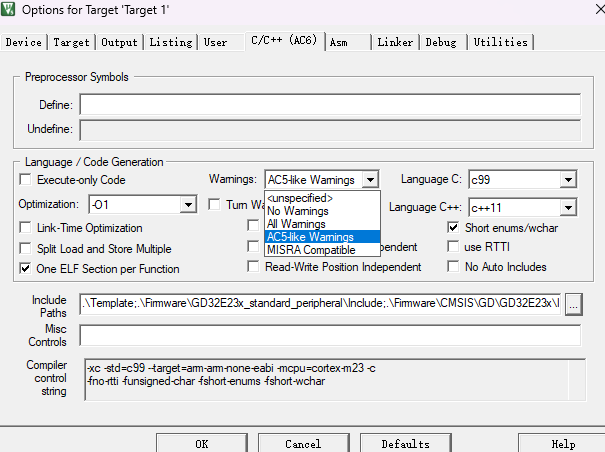

这里改成AC-5

无警告了

------------测试用----------

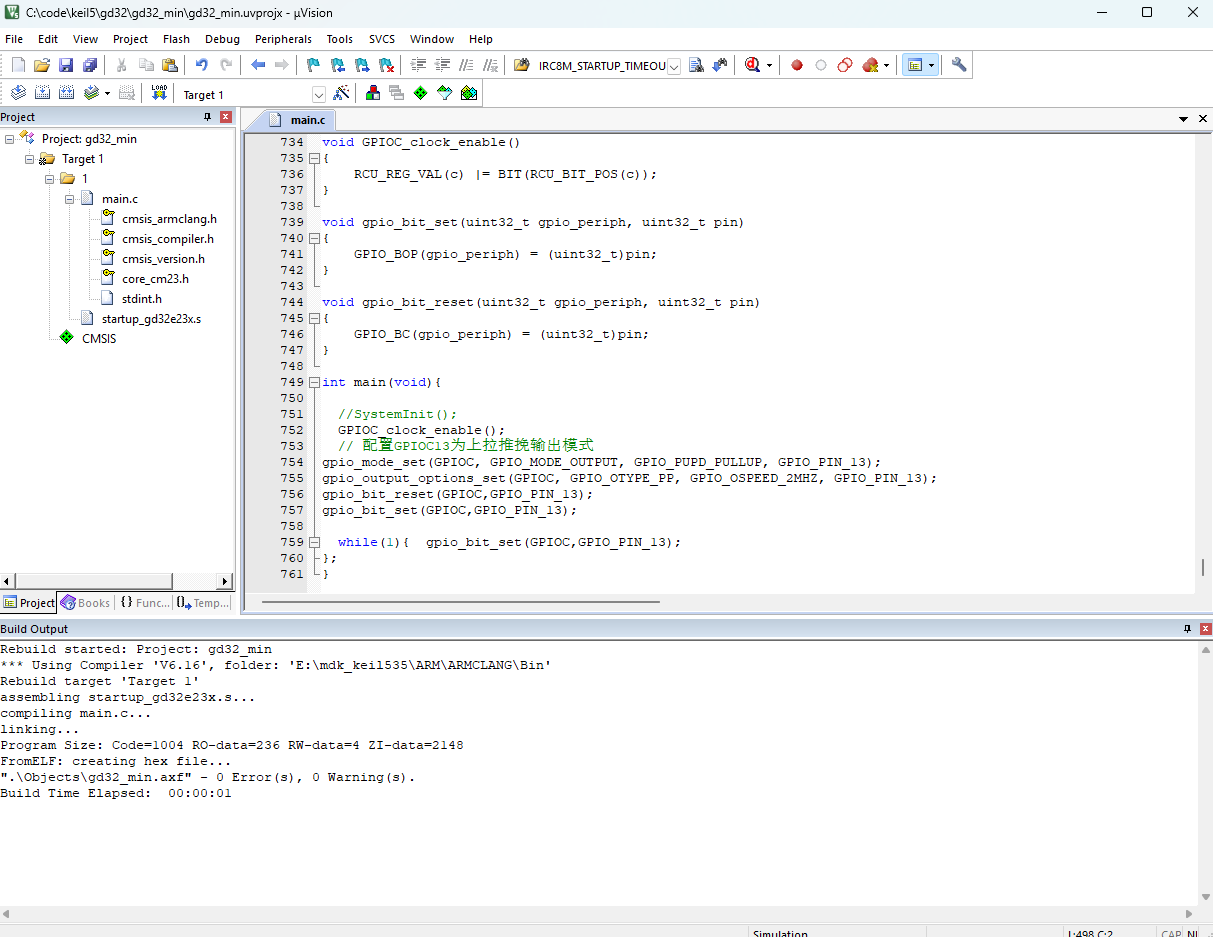

只用main.c加上startup_gd32e23x.s编译

#if !defined (IRC8M_STARTUP_TIMEOUT)

#define IRC8M_STARTUP_TIMEOUT ((uint16_t)0x0500)

#endif /* internal 8MHz RC oscillator startup timeout */

/* bit operations */

#define REG32(addr) (*(volatile uint32_t *)(uint32_t)(addr))

#define REG16(addr) (*(volatile uint16_t *)(uint32_t)(addr))

#define REG8(addr) (*(volatile uint8_t *)(uint32_t)(addr))

#define BIT(x) ((uint32_t)((uint32_t)0x01U<<(x)))

#define BITS(start, end) ((0xFFFFFFFFUL << (start)) & (0xFFFFFFFFUL >> (31U - (uint32_t)(end))))

#define GET_BITS(regval, start, end) (((regval) & BITS((start),(end))) >> (start))

/* main flash and SRAM memory map */

#define FLASH_BASE ((uint32_t)0x08000000U) /*!< main FLASH base address */

#define SRAM_BASE ((uint32_t)0x20000000U) /*!< SRAM base address */

/* SRAM and peripheral base bit-band region */

#define SRAM_BB_BASE ((uint32_t)0x22000000U) /*!< SRAM bit-band base address */

#define PERIPH_BB_BASE ((uint32_t)0x42000000U) /*!< peripheral bit-band base address */

/* peripheral memory map */

#define APB1_BUS_BASE ((uint32_t)0x40000000U) /*!< apb1 base address */

#define APB2_BUS_BASE ((uint32_t)0x40010000U) /*!< apb2 base address */

#define AHB1_BUS_BASE ((uint32_t)0x40020000U) /*!< ahb1 base address */

#define AHB2_BUS_BASE ((uint32_t)0x48000000U) /*!< ahb2 base address */

/* advanced peripheral bus 1 memory map */

#define TIMER_BASE (APB1_BUS_BASE + 0x00000000U) /*!< TIMER base address */

#define RTC_BASE (APB1_BUS_BASE + 0x00002800U) /*!< RTC base address */

#define WWDGT_BASE (APB1_BUS_BASE + 0x00002C00U) /*!< WWDGT base address */

#define FWDGT_BASE (APB1_BUS_BASE + 0x00003000U) /*!< FWDGT base address */

#define SPI_BASE (APB1_BUS_BASE + 0x00003800U) /*!< SPI base address */

#define USART_BASE (APB1_BUS_BASE + 0x00004400U) /*!< USART base address */

#define I2C_BASE (APB1_BUS_BASE + 0x00005400U) /*!< I2C base address */

#define PMU_BASE (APB1_BUS_BASE + 0x00007000U) /*!< PMU base address */

/* advanced peripheral bus 2 memory map */

#define SYSCFG_BASE (APB2_BUS_BASE + 0x00000000U) /*!< SYSCFG base address */

#define CMP_BASE (APB2_BUS_BASE + 0x0000001CU) /*!< CMP base address */

#define EXTI_BASE (APB2_BUS_BASE + 0x00000400U) /*!< EXTI base address */

#define ADC_BASE (APB2_BUS_BASE + 0x00002400U) /*!< ADC base address */

/* advanced high performance bus 1 memory map */

#define DMA_BASE (AHB1_BUS_BASE + 0x00000000U) /*!< DMA base address */

#define DMA_CHANNEL_BASE (DMA_BASE + 0x00000008U) /*!< DMA channel base address */

#define RCU_BASE (AHB1_BUS_BASE + 0x00001000U) /*!< RCU base address */

#define FMC_BASE (AHB1_BUS_BASE + 0x00002000U) /*!< FMC base address */

#define CRC_BASE (AHB1_BUS_BASE + 0x00003000U) /*!< CRC base address */

/* advanced high performance bus 2 memory map */

#define GPIO_BASE (AHB2_BUS_BASE + 0x00000000U) /*!< GPIO base address */

/* option byte and debug memory map */

#define OB_BASE ((uint32_t)0x1FFFF800U) /*!< OB base address */

#define DBG_BASE ((uint32_t)0x40015800U) /*!< DBG base address */

/* GD32E23x firmware library version number V1.0 */

#define __GD32E23x_STDPERIPH_VERSION_MAIN (0x02) /*!< [31:24] main version */

#define __GD32E23x_STDPERIPH_VERSION_SUB1 (0x03) /*!< [23:16] sub1 version */

#define __GD32E23x_STDPERIPH_VERSION_SUB2 (0x00) /*!< [15:8] sub2 version */

#define __GD32E23x_STDPERIPH_VERSION_RC (0x00) /*!< [7:0] release candidate */

#define __GD32E23x_STDPERIPH_VERSION ((__GD32E23x_STDPERIPH_VERSION_MAIN << 24)\

|(__GD32E23x_STDPERIPH_VERSION_SUB1 << 16)\

|(__GD32E23x_STDPERIPH_VERSION_SUB2 << 8)\

|(__GD32E23x_STDPERIPH_VERSION_RC))

/* configuration of the Cortex-M23 processor and core peripherals */

#define __CM23_REV 0x0100U /*!< Core revision r1p0 */

#define __SAUREGION_PRESENT 0U /*!< SAU regions are not present */

#define __MPU_PRESENT 0U /*!< MPU is present */

#define __VTOR_PRESENT 1U /*!< VTOR is present */

#define __NVIC_PRIO_BITS 2U /*!< Number of Bits used for Priority Levels */

#define __Vendor_SysTickConfig 0U /*!< Set to 1 if different SysTick Config is used */

typedef enum IRQn

{

/* Cortex-M23 processor exceptions numbers */

NonMaskableInt_IRQn = -14, /*!< non maskable interrupt */

HardFault_IRQn = -13, /*!< hardfault interrupt */

SVCall_IRQn = -5, /*!< sv call interrupt */

PendSV_IRQn = -2, /*!< pend sv interrupt */

SysTick_IRQn = -1, /*!< system tick interrupt */

/* interruput numbers */

WWDGT_IRQn = 0, /*!< window watchdog timer interrupt */

LVD_IRQn = 1, /*!< LVD through EXTI line detect interrupt */

RTC_IRQn = 2, /*!< RTC through EXTI line interrupt */

FMC_IRQn = 3, /*!< FMC interrupt */

RCU_IRQn = 4, /*!< RCU interrupt */

EXTI0_1_IRQn = 5, /*!< EXTI line 0 and 1 interrupts */

EXTI2_3_IRQn = 6, /*!< EXTI line 2 and 3 interrupts */

EXTI4_15_IRQn = 7, /*!< EXTI line 4 to 15 interrupts */

DMA_Channel0_IRQn = 9, /*!< DMA channel 0 interrupt */

DMA_Channel1_2_IRQn = 10, /*!< DMA channel 1 and channel 2 interrupts */

DMA_Channel3_4_IRQn = 11, /*!< DMA channel 3 and channel 4 interrupts */

ADC_CMP_IRQn = 12, /*!< ADC, CMP interrupts */

TIMER0_BRK_UP_TRG_COM_IRQn = 13, /*!< TIMER0 break, update, trigger and commutation interrupts */

TIMER0_Channel_IRQn = 14, /*!< TIMER0 channel capture compare interrupts */

TIMER2_IRQn = 16, /*!< TIMER2 interrupt */

TIMER5_IRQn = 17, /*!< TIMER5 interrupt */

TIMER13_IRQn = 19, /*!< TIMER13 interrupt */

TIMER14_IRQn = 20, /*!< TIMER14 interrupt */

TIMER15_IRQn = 21, /*!< TIMER15 interrupt */

TIMER16_IRQn = 22, /*!< TIMER16 interrupt */

I2C0_EV_IRQn = 23, /*!< I2C0 event interrupt */

I2C1_EV_IRQn = 24, /*!< I2C1 event interrupt */

SPI0_IRQn = 25, /*!< SPI0 interrupt */

SPI1_IRQn = 26, /*!< SPI1 interrupt */

USART0_IRQn = 27, /*!< USART0 interrupt */

USART1_IRQn = 28, /*!< USART1 interrupt */

I2C0_ER_IRQn = 32, /*!< I2C0 error interrupt */

I2C1_ER_IRQn = 34, /*!< I2C1 error interrupt */

} IRQn_Type;

#include "core_cm23.h"

#include <stdint.h>

/* RCU definitions */

#define RCU RCU_BASE

/* registers definitions */

#define RCU_CTL0 REG32(RCU + 0x00000000U) /*!< control register 0 */

#define RCU_CFG0 REG32(RCU + 0x00000004U) /*!< configuration register 0 */

#define RCU_INT REG32(RCU + 0x00000008U) /*!< interrupt register */

#define RCU_APB2RST REG32(RCU + 0x0000000CU) /*!< APB2 reset register */

#define RCU_APB1RST REG32(RCU + 0x00000010U) /*!< APB1 reset register */

#define RCU_AHBEN REG32(RCU + 0x00000014U) /*!< AHB enable register */

#define RCU_APB2EN REG32(RCU + 0x00000018U) /*!< APB2 enable register */

#define RCU_APB1EN REG32(RCU + 0x0000001CU) /*!< APB1 enable register */

#define RCU_BDCTL REG32(RCU + 0x00000020U) /*!< backup domain control register */

#define RCU_RSTSCK REG32(RCU + 0x00000024U) /*!< reset source /clock register */

#define RCU_AHBRST REG32(RCU + 0x00000028U) /*!< AHB reset register */

#define RCU_CFG1 REG32(RCU + 0x0000002CU) /*!< configuration register 1 */

#define RCU_CFG2 REG32(RCU + 0x00000030U) /*!< configuration register 2 */

#define RCU_CTL1 REG32(RCU + 0x00000034U) /*!< control register 1 */

#define RCU_VKEY REG32(RCU + 0x00000100U) /*!< voltage key register */

#define RCU_DSV REG32(RCU + 0x00000134U) /*!< deep-sleep mode voltage register */

/* bits definitions */

/* RCU_CTL0 */

#define RCU_CTL0_IRC8MEN BIT(0) /*!< internal high speed oscillator enable */

#define RCU_CTL0_IRC8MSTB BIT(1) /*!< IRC8M high speed internal oscillator stabilization flag */

#define RCU_CTL0_IRC8MADJ BITS(3,7) /*!< high speed internal oscillator clock trim adjust value */

#define RCU_CTL0_IRC8MCALIB BITS(8,15) /*!< high speed internal oscillator calibration value register */

#define RCU_CTL0_HXTALEN BIT(16) /*!< external high speed oscillator enable */

#define RCU_CTL0_HXTALSTB BIT(17) /*!< external crystal oscillator clock stabilization flag */

#define RCU_CTL0_HXTALBPS BIT(18) /*!< external crystal oscillator clock bypass mode enable */

#define RCU_CTL0_CKMEN BIT(19) /*!< HXTAL clock monitor enable */

#define RCU_CTL0_PLLEN BIT(24) /*!< PLL enable */

#define RCU_CTL0_PLLSTB BIT(25) /*!< PLL clock stabilization flag */

/* RCU_CFG0 */

#define RCU_CFG0_SCS BITS(0,1) /*!< system clock switch */

#define RCU_CFG0_SCSS BITS(2,3) /*!< system clock switch status */

#define RCU_CFG0_AHBPSC BITS(4,7) /*!< AHB prescaler selection */

#define RCU_CFG0_APB1PSC BITS(8,10) /*!< APB1 prescaler selection */

#define RCU_CFG0_APB2PSC BITS(11,13) /*!< APB2 prescaler selection */

#define RCU_CFG0_ADCPSC BITS(14,15) /*!< ADC clock prescaler selection */

#define RCU_CFG0_PLLSEL BIT(16) /*!< PLL clock source selection */

#define RCU_CFG0_PLLPREDV BIT(17) /*!< divider for PLL source clock selection */

#define RCU_CFG0_PLLMF (BIT(27) | BITS(18,21)) /*!< PLL multiply factor */

#define RCU_CFG0_CKOUTSEL BITS(24,26) /*!< CK_OUT clock source selection */

#define RCU_CFG0_PLLMF4 BIT(27) /*!< bit 4 of PLLMF */

#define RCU_CFG0_CKOUTDIV BITS(28,30) /*!< CK_OUT divider which the CK_OUT frequency can be reduced */

#define RCU_CFG0_PLLDV BIT(31) /*!< CK_PLL divide by 1 or 2 */

/* RCU_INT */

#define RCU_INT_IRC40KSTBIF BIT(0) /*!< IRC40K stabilization interrupt flag */

#define RCU_INT_LXTALSTBIF BIT(1) /*!< LXTAL stabilization interrupt flag */

#define RCU_INT_IRC8MSTBIF BIT(2) /*!< IRC8M stabilization interrupt flag */

#define RCU_INT_HXTALSTBIF BIT(3) /*!< HXTAL stabilization interrupt flag */

#define RCU_INT_PLLSTBIF BIT(4) /*!< PLL stabilization interrupt flag */

#define RCU_INT_IRC28MSTBIF BIT(5) /*!< IRC28M stabilization interrupt flag */

#define RCU_INT_CKMIF BIT(7) /*!< HXTAL clock stuck interrupt flag */

#define RCU_INT_IRC40KSTBIE BIT(8) /*!< IRC40K stabilization interrupt enable */

#define RCU_INT_LXTALSTBIE BIT(9) /*!< LXTAL stabilization interrupt enable */

#define RCU_INT_IRC8MSTBIE BIT(10) /*!< IRC8M stabilization interrupt enable */

#define RCU_INT_HXTALSTBIE BIT(11) /*!< HXTAL stabilization interrupt enable */

#define RCU_INT_PLLSTBIE BIT(12) /*!< PLL stabilization interrupt enable */

#define RCU_INT_IRC28MSTBIE BIT(13) /*!< IRC28M stabilization interrupt enable */

#define RCU_INT_IRC40KSTBIC BIT(16) /*!< IRC40K stabilization interrupt clear */

#define RCU_INT_LXTALSTBIC BIT(17) /*!< LXTAL stabilization interrupt clear */

#define RCU_INT_IRC8MSTBIC BIT(18) /*!< IRC8M stabilization interrupt clear */

#define RCU_INT_HXTALSTBIC BIT(19) /*!< HXTAL stabilization interrupt clear */

#define RCU_INT_PLLSTBIC BIT(20) /*!< PLL stabilization interrupt clear */

#define RCU_INT_IRC28MSTBIC BIT(21) /*!< IRC28M stabilization interrupt clear */

#define RCU_INT_CKMIC BIT(23) /*!< HXTAL clock stuck interrupt clear */

/* RCU_APB2RST */

#define RCU_APB2RST_CFGCMPRST BIT(0) /*!< system configuration and comparator reset */

#define RCU_APB2RST_ADCRST BIT(9) /*!< ADC reset */

#define RCU_APB2RST_TIMER0RST BIT(11) /*!< TIMER0 reset */

#define RCU_APB2RST_SPI0RST BIT(12) /*!< SPI0 reset */

#define RCU_APB2RST_USART0RST BIT(14) /*!< USART0 reset */

#define RCU_APB2RST_TIMER14RST BIT(16) /*!< TIMER14 reset */

#define RCU_APB2RST_TIMER15RST BIT(17) /*!< TIMER15 reset */

#define RCU_APB2RST_TIMER16RST BIT(18) /*!< TIMER16 reset */

/* RCU_APB1RST */

#define RCU_APB1RST_TIMER2RST BIT(1) /*!< TIMER2 timer reset */

#define RCU_APB1RST_TIMER5RST BIT(4) /*!< TIMER5 timer reset */

#define RCU_APB1RST_TIMER13RST BIT(8) /*!< TIMER13 timer reset */

#define RCU_APB1RST_WWDGTRST BIT(11) /*!< window watchdog timer reset */

#define RCU_APB1RST_SPI1RST BIT(14) /*!< SPI1 reset */

#define RCU_APB1RST_USART1RST BIT(17) /*!< USART1 reset */

#define RCU_APB1RST_I2C0RST BIT(21) /*!< I2C0 reset */

#define RCU_APB1RST_I2C1RST BIT(22) /*!< I2C1 reset */

#define RCU_APB1RST_PMURST BIT(28) /*!< power control reset */

/* RCU_AHBEN */

#define RCU_AHBEN_DMAEN BIT(0) /*!< DMA clock enable */

#define RCU_AHBEN_SRAMSPEN BIT(2) /*!< SRAM interface clock enable */

#define RCU_AHBEN_FMCSPEN BIT(4) /*!< FMC clock enable */

#define RCU_AHBEN_CRCEN BIT(6) /*!< CRC clock enable */

#define RCU_AHBEN_PAEN BIT(17) /*!< GPIO port A clock enable */

#define RCU_AHBEN_PBEN BIT(18) /*!< GPIO port B clock enable */

#define RCU_AHBEN_PCEN BIT(19) /*!< GPIO port C clock enable */

#define RCU_AHBEN_PFEN BIT(22) /*!< GPIO port F clock enable */

/* RCU_APB2EN */

#define RCU_APB2EN_CFGCMPEN BIT(0) /*!< system configuration and comparator clock enable */

#define RCU_APB2EN_ADCEN BIT(9) /*!< ADC interface clock enable */

#define RCU_APB2EN_TIMER0EN BIT(11) /*!< TIMER0 timer clock enable */

#define RCU_APB2EN_SPI0EN BIT(12) /*!< SPI0 clock enable */

#define RCU_APB2EN_USART0EN BIT(14) /*!< USART0 clock enable */

#define RCU_APB2EN_TIMER14EN BIT(16) /*!< TIMER14 timer clock enable */

#define RCU_APB2EN_TIMER15EN BIT(17) /*!< TIMER15 timer clock enable */

#define RCU_APB2EN_TIMER16EN BIT(18) /*!< TIMER16 timer clock enable */

#define RCU_APB2EN_DBGMCUEN BIT(22) /*!< DBGMCU clock enable */

/* RCU_APB1EN */

#define RCU_APB1EN_TIMER2EN BIT(1) /*!< TIMER2 timer clock enable */

#define RCU_APB1EN_TIMER5EN BIT(4) /*!< TIMER5 timer clock enable */

#define RCU_APB1EN_TIMER13EN BIT(8) /*!< TIMER13 timer clock enable */

#define RCU_APB1EN_WWDGTEN BIT(11) /*!< window watchdog timer clock enable */

#define RCU_APB1EN_SPI1EN BIT(14) /*!< SPI1 clock enable */

#define RCU_APB1EN_USART1EN BIT(17) /*!< USART1 clock enable */

#define RCU_APB1EN_I2C0EN BIT(21) /*!< I2C0 clock enable */

#define RCU_APB1EN_I2C1EN BIT(22) /*!< I2C1 clock enable */

#define RCU_APB1EN_PMUEN BIT(28) /*!< power interface clock enable */

/* RCU_BDCTL */

#define RCU_BDCTL_LXTALEN BIT(0) /*!< LXTAL enable */

#define RCU_BDCTL_LXTALSTB BIT(1) /*!< external low-speed oscillator stabilization */

#define RCU_BDCTL_LXTALBPS BIT(2) /*!< LXTAL bypass mode enable */

#define RCU_BDCTL_LXTALDRI BITS(3,4) /*!< LXTAL drive capability */

#define RCU_BDCTL_RTCSRC BITS(8,9) /*!< RTC clock entry selection */

#define RCU_BDCTL_RTCEN BIT(15) /*!< RTC clock enable */

#define RCU_BDCTL_BKPRST BIT(16) /*!< backup domain reset */

/* RCU_RSTSCK */

#define RCU_RSTSCK_IRC40KEN BIT(0) /*!< IRC40K enable */

#define RCU_RSTSCK_IRC40KSTB BIT(1) /*!< IRC40K stabilization */

#define RCU_RSTSCK_V12RSTF BIT(23) /*!< V12 domain power reset flag */

#define RCU_RSTSCK_RSTFC BIT(24) /*!< reset flag clear */

#define RCU_RSTSCK_OBLRSTF BIT(25) /*!< option byte loader reset flag */

#define RCU_RSTSCK_EPRSTF BIT(26) /*!< external pin reset flag */

#define RCU_RSTSCK_PORRSTF BIT(27) /*!< power reset flag */

#define RCU_RSTSCK_SWRSTF BIT(28) /*!< software reset flag */

#define RCU_RSTSCK_FWDGTRSTF BIT(29) /*!< free watchdog timer reset flag */

#define RCU_RSTSCK_WWDGTRSTF BIT(30) /*!< window watchdog timer reset flag */

#define RCU_RSTSCK_LPRSTF BIT(31) /*!< low-power reset flag */

/* RCU_AHBRST */

#define RCU_AHBRST_PARST BIT(17) /*!< GPIO port A reset */

#define RCU_AHBRST_PBRST BIT(18) /*!< GPIO port B reset */

#define RCU_AHBRST_PCRST BIT(19) /*!< GPIO port C reset */

#define RCU_AHBRST_PFRST BIT(22) /*!< GPIO port F reset */

/* RCU_CFG1 */

#define RCU_CFG1_PREDV BITS(0,3) /*!< CK_HXTAL divider previous PLL */

/* RCU_CFG2 */

#define RCU_CFG2_USART0SEL BITS(0,1) /*!< CK_USART0 clock source selection */

#define RCU_CFG2_ADCSEL BIT(8) /*!< CK_ADC clock source selection */

#define RCU_CFG2_IRC28MDIV BIT(16) /*!< CK_IRC28M divider 2 or not */

#define RCU_CFG2_ADCPSC2 BIT(31) /*!< bit 2 of ADCPSC */

/* RCU_CTL1 */

#define RCU_CTL1_IRC28MEN BIT(0) /*!< IRC28M internal 28M RC oscillator enable */

#define RCU_CTL1_IRC28MSTB BIT(1) /*!< IRC28M internal 28M RC oscillator stabilization flag */

#define RCU_CTL1_IRC28MADJ BITS(3,7) /*!< internal 28M RC oscillator clock trim adjust value */

#define RCU_CTL1_IRC28MCALIB BITS(8,15) /*!< internal 28M RC oscillator calibration value register */

/* RCU_VKEY */

#define RCU_VKEY_KEY BITS(0,31) /*!< key of RCU_DSV register */

/* RCU_DSV */

#define RCU_DSV_DSLPVS BITS(0,1) /*!< deep-sleep mode voltage select */

/* constants definitions */

/* define the peripheral clock enable bit position and its register index offset */

#define RCU_REGIDX_BIT(regidx, bitpos) (((uint32_t)(regidx)<<6) | (uint32_t)(bitpos))

#define RCU_REG_VAL(periph) (REG32(RCU + ((uint32_t)(periph)>>6)))

#define RCU_BIT_POS(val) ((uint32_t)(val) & 0x1FU)

/* define the voltage key unlock value */

#define RCU_VKEY_UNLOCK ((uint32_t)0x1A2B3C4D)

/* system clock source select */

#define CFG0_SCS(regval) (BITS(0,1) & ((uint32_t)(regval) << 0))

#define RCU_CKSYSSRC_IRC8M CFG0_SCS(0) /*!< system clock source select IRC8M */

#define RCU_CKSYSSRC_HXTAL CFG0_SCS(1) /*!< system clock source select HXTAL */

#define RCU_CKSYSSRC_PLL CFG0_SCS(2) /*!< system clock source select PLL */

/* system clock source select status */

#define CFG0_SCSS(regval) (BITS(2,3) & ((uint32_t)(regval) << 2))

#define RCU_SCSS_IRC8M CFG0_SCSS(0) /*!< system clock source select IRC8M */

#define RCU_SCSS_HXTAL CFG0_SCSS(1) /*!< system clock source select HXTAL */

#define RCU_SCSS_PLL CFG0_SCSS(2) /*!< system clock source select PLL */

/* AHB prescaler selection */

#define CFG0_AHBPSC(regval) (BITS(4,7) & ((uint32_t)(regval) << 4))

#define RCU_AHB_CKSYS_DIV1 CFG0_AHBPSC(0) /*!< AHB prescaler select CK_SYS */

#define RCU_AHB_CKSYS_DIV2 CFG0_AHBPSC(8) /*!< AHB prescaler select CK_SYS/2 */

#define RCU_AHB_CKSYS_DIV4 CFG0_AHBPSC(9) /*!< AHB prescaler select CK_SYS/4 */

#define RCU_AHB_CKSYS_DIV8 CFG0_AHBPSC(10) /*!< AHB prescaler select CK_SYS/8 */

#define RCU_AHB_CKSYS_DIV16 CFG0_AHBPSC(11) /*!< AHB prescaler select CK_SYS/16 */

#define RCU_AHB_CKSYS_DIV64 CFG0_AHBPSC(12) /*!< AHB prescaler select CK_SYS/64 */

#define RCU_AHB_CKSYS_DIV128 CFG0_AHBPSC(13) /*!< AHB prescaler select CK_SYS/128 */

#define RCU_AHB_CKSYS_DIV256 CFG0_AHBPSC(14) /*!< AHB prescaler select CK_SYS/256 */

#define RCU_AHB_CKSYS_DIV512 CFG0_AHBPSC(15) /*!< AHB prescaler select CK_SYS/512 */

/* APB1 prescaler selection */

#define CFG0_APB1PSC(regval) (BITS(8,10) & ((uint32_t)(regval) << 8))

#define RCU_APB1_CKAHB_DIV1 CFG0_APB1PSC(0) /*!< APB1 prescaler select CK_AHB */

#define RCU_APB1_CKAHB_DIV2 CFG0_APB1PSC(4) /*!< APB1 prescaler select CK_AHB/2 */

#define RCU_APB1_CKAHB_DIV4 CFG0_APB1PSC(5) /*!< APB1 prescaler select CK_AHB/4 */

#define RCU_APB1_CKAHB_DIV8 CFG0_APB1PSC(6) /*!< APB1 prescaler select CK_AHB/8 */

#define RCU_APB1_CKAHB_DIV16 CFG0_APB1PSC(7) /*!< APB1 prescaler select CK_AHB/16 */

/* APB2 prescaler selection */

#define CFG0_APB2PSC(regval) (BITS(11,13) & ((uint32_t)(regval) << 11))

#define RCU_APB2_CKAHB_DIV1 CFG0_APB2PSC(0) /*!< APB2 prescaler select CK_AHB */

#define RCU_APB2_CKAHB_DIV2 CFG0_APB2PSC(4) /*!< APB2 prescaler select CK_AHB/2 */

#define RCU_APB2_CKAHB_DIV4 CFG0_APB2PSC(5) /*!< APB2 prescaler select CK_AHB/4 */

#define RCU_APB2_CKAHB_DIV8 CFG0_APB2PSC(6) /*!< APB2 prescaler select CK_AHB/8 */

#define RCU_APB2_CKAHB_DIV16 CFG0_APB2PSC(7) /*!< APB2 prescaler select CK_AHB/16 */

/* ADC clock prescaler selection */

#define CFG0_ADCPSC(regval) (BITS(14,15) & ((uint32_t)(regval) << 14))

#define RCU_ADC_CKAPB2_DIV2 CFG0_ADCPSC(0) /*!< ADC clock prescaler select CK_APB2/2 */

#define RCU_ADC_CKAPB2_DIV4 CFG0_ADCPSC(1) /*!< ADC clock prescaler select CK_APB2/4 */

#define RCU_ADC_CKAPB2_DIV6 CFG0_ADCPSC(2) /*!< ADC clock prescaler select CK_APB2/6 */

#define RCU_ADC_CKAPB2_DIV8 CFG0_ADCPSC(3) /*!< ADC clock prescaler select CK_APB2/8 */

/* PLL clock source selection */

#define RCU_PLLSRC_IRC8M_DIV2 (uint32_t)0x00000000U /*!< PLL clock source select IRC8M/2 */

#define RCU_PLLSRC_HXTAL RCU_CFG0_PLLSEL /*!< PLL clock source select HXTAL */

/* HXTAL divider for PLL source clock selection */

#define RCU_PLLPREDV (uint32_t)0x00000000U /*!< HXTAL clock selected */

#define RCU_PLLPREDV_DIV2 RCU_CFG0_PLLPREDV /*!< HXTAL/2 clock selected */

/* PLL multiply factor */

#define CFG0_PLLMF(regval) (BITS(18,21) & ((uint32_t)(regval) << 18))

#define RCU_PLL_MUL2 CFG0_PLLMF(0) /*!< PLL source clock multiply by 2 */

#define RCU_PLL_MUL3 CFG0_PLLMF(1) /*!< PLL source clock multiply by 3 */

#define RCU_PLL_MUL4 CFG0_PLLMF(2) /*!< PLL source clock multiply by 4 */

#define RCU_PLL_MUL5 CFG0_PLLMF(3) /*!< PLL source clock multiply by 5 */

#define RCU_PLL_MUL6 CFG0_PLLMF(4) /*!< PLL source clock multiply by 6 */

#define RCU_PLL_MUL7 CFG0_PLLMF(5) /*!< PLL source clock multiply by 7 */

#define RCU_PLL_MUL8 CFG0_PLLMF(6) /*!< PLL source clock multiply by 8 */

#define RCU_PLL_MUL9 CFG0_PLLMF(7) /*!< PLL source clock multiply by 9 */

#define RCU_PLL_MUL10 CFG0_PLLMF(8) /*!< PLL source clock multiply by 10 */

#define RCU_PLL_MUL11 CFG0_PLLMF(9) /*!< PLL source clock multiply by 11 */

#define RCU_PLL_MUL12 CFG0_PLLMF(10) /*!< PLL source clock multiply by 12 */

#define RCU_PLL_MUL13 CFG0_PLLMF(11) /*!< PLL source clock multiply by 13 */

#define RCU_PLL_MUL14 CFG0_PLLMF(12) /*!< PLL source clock multiply by 14 */

#define RCU_PLL_MUL15 CFG0_PLLMF(13) /*!< PLL source clock multiply by 15 */

#define RCU_PLL_MUL16 CFG0_PLLMF(14) /*!< PLL source clock multiply by 16 */

#define RCU_PLL_MUL17 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(0)) /*!< PLL source clock multiply by 17 */

#define RCU_PLL_MUL18 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(1)) /*!< PLL source clock multiply by 18 */

#define RCU_PLL_MUL19 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(2)) /*!< PLL source clock multiply by 19 */

#define RCU_PLL_MUL20 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(3)) /*!< PLL source clock multiply by 20 */

#define RCU_PLL_MUL21 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(4)) /*!< PLL source clock multiply by 21 */

#define RCU_PLL_MUL22 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(5)) /*!< PLL source clock multiply by 22 */

#define RCU_PLL_MUL23 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(6)) /*!< PLL source clock multiply by 23 */

#define RCU_PLL_MUL24 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(7)) /*!< PLL source clock multiply by 24 */

#define RCU_PLL_MUL25 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(8)) /*!< PLL source clock multiply by 25 */

#define RCU_PLL_MUL26 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(9)) /*!< PLL source clock multiply by 26 */

#define RCU_PLL_MUL27 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(10)) /*!< PLL source clock multiply by 27 */

#define RCU_PLL_MUL28 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(11)) /*!< PLL source clock multiply by 28 */

#define RCU_PLL_MUL29 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(12)) /*!< PLL source clock multiply by 29 */

#define RCU_PLL_MUL30 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(13)) /*!< PLL source clock multiply by 30 */

#define RCU_PLL_MUL31 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(14)) /*!< PLL source clock multiply by 31 */

#define RCU_PLL_MUL32 (RCU_CFG0_PLLMF4 | CFG0_PLLMF(15)) /*!< PLL source clock multiply by 32 */

/* CK_OUT clock source selection */

#define CFG0_CKOUTSEL(regval) (BITS(24,26) & ((uint32_t)(regval) << 24))

#define RCU_CKOUTSRC_NONE CFG0_CKOUTSEL(0) /*!< no clock selected */

#define RCU_CKOUTSRC_IRC28M CFG0_CKOUTSEL(1) /*!< CK_OUT clock source select IRC28M */

#define RCU_CKOUTSRC_IRC40K CFG0_CKOUTSEL(2) /*!< CK_OUT clock source select IRC40K */

#define RCU_CKOUTSRC_LXTAL CFG0_CKOUTSEL(3) /*!< CK_OUT clock source select LXTAL */

#define RCU_CKOUTSRC_CKSYS CFG0_CKOUTSEL(4) /*!< CK_OUT clock source select CKSYS */

#define RCU_CKOUTSRC_IRC8M CFG0_CKOUTSEL(5) /*!< CK_OUT clock source select IRC8M */

#define RCU_CKOUTSRC_HXTAL CFG0_CKOUTSEL(6) /*!< CK_OUT clock source select HXTAL */

#define RCU_CKOUTSRC_CKPLL_DIV1 (RCU_CFG0_PLLDV | CFG0_CKOUTSEL(7)) /*!< CK_OUT clock source select CK_PLL */

#define RCU_CKOUTSRC_CKPLL_DIV2 CFG0_CKOUTSEL(7) /*!< CK_OUT clock source select CK_PLL/2 */

/* CK_OUT divider */

#define CFG0_CKOUTDIV(regval) (BITS(28,30) & ((uint32_t)(regval) << 28))

#define RCU_CKOUT_DIV1 CFG0_CKOUTDIV(0) /*!< CK_OUT is divided by 1 */

#define RCU_CKOUT_DIV2 CFG0_CKOUTDIV(1) /*!< CK_OUT is divided by 2 */

#define RCU_CKOUT_DIV4 CFG0_CKOUTDIV(2) /*!< CK_OUT is divided by 4 */

#define RCU_CKOUT_DIV8 CFG0_CKOUTDIV(3) /*!< CK_OUT is divided by 8 */

#define RCU_CKOUT_DIV16 CFG0_CKOUTDIV(4) /*!< CK_OUT is divided by 16 */

#define RCU_CKOUT_DIV32 CFG0_CKOUTDIV(5) /*!< CK_OUT is divided by 32 */

#define RCU_CKOUT_DIV64 CFG0_CKOUTDIV(6) /*!< CK_OUT is divided by 64 */

#define RCU_CKOUT_DIV128 CFG0_CKOUTDIV(7) /*!< CK_OUT is divided by 128 */

/* CK_PLL divide by 1 or 2 for CK_OUT */

#define RCU_PLLDV_CKPLL_DIV2 (uint32_t)0x00000000U /*!< CK_PLL divide by 2 for CK_OUT */

#define RCU_PLLDV_CKPLL RCU_CFG0_PLLDV /*!< CK_PLL divide by 1 for CK_OUT */

/* LXTAL drive capability */

#define BDCTL_LXTALDRI(regval) (BITS(3,4) & ((uint32_t)(regval) << 3))

#define RCU_LXTAL_LOWDRI BDCTL_LXTALDRI(0) /*!< lower driving capability */

#define RCU_LXTAL_MED_LOWDRI BDCTL_LXTALDRI(1) /*!< medium low driving capability */

#define RCU_LXTAL_MED_HIGHDRI BDCTL_LXTALDRI(2) /*!< medium high driving capability */

#define RCU_LXTAL_HIGHDRI BDCTL_LXTALDRI(3) /*!< higher driving capability */

/* RTC clock entry selection */

#define BDCTL_RTCSRC(regval) (BITS(8,9) & ((uint32_t)(regval) << 8))

#define RCU_RTCSRC_NONE BDCTL_RTCSRC(0) /*!< no clock selected */

#define RCU_RTCSRC_LXTAL BDCTL_RTCSRC(1) /*!< LXTAL selected as RTC source clock */

#define RCU_RTCSRC_IRC40K BDCTL_RTCSRC(2) /*!< IRC40K selected as RTC source clock */

#define RCU_RTCSRC_HXTAL_DIV32 BDCTL_RTCSRC(3) /*!< HXTAL/32 selected as RTC source clock */

/* CK_HXTAL divider previous PLL */

#define CFG1_PREDV(regval) (BITS(0,3) & ((uint32_t)(regval) << 0))

#define RCU_PLL_PREDV1 CFG1_PREDV(0) /*!< PLL not divided */

#define RCU_PLL_PREDV2 CFG1_PREDV(1) /*!< PLL divided by 2 */

#define RCU_PLL_PREDV3 CFG1_PREDV(2) /*!< PLL divided by 3 */

#define RCU_PLL_PREDV4 CFG1_PREDV(3) /*!< PLL divided by 4 */

#define RCU_PLL_PREDV5 CFG1_PREDV(4) /*!< PLL divided by 5 */

#define RCU_PLL_PREDV6 CFG1_PREDV(5) /*!< PLL divided by 6 */

#define RCU_PLL_PREDV7 CFG1_PREDV(6) /*!< PLL divided by 7 */

#define RCU_PLL_PREDV8 CFG1_PREDV(7) /*!< PLL divided by 8 */

#define RCU_PLL_PREDV9 CFG1_PREDV(8) /*!< PLL divided by 9 */

#define RCU_PLL_PREDV10 CFG1_PREDV(9) /*!< PLL divided by 10 */

#define RCU_PLL_PREDV11 CFG1_PREDV(10) /*!< PLL divided by 11 */

#define RCU_PLL_PREDV12 CFG1_PREDV(11) /*!< PLL divided by 12 */

#define RCU_PLL_PREDV13 CFG1_PREDV(12) /*!< PLL divided by 13 */

#define RCU_PLL_PREDV14 CFG1_PREDV(13) /*!< PLL divided by 14 */

#define RCU_PLL_PREDV15 CFG1_PREDV(14) /*!< PLL divided by 15 */

#define RCU_PLL_PREDV16 CFG1_PREDV(15) /*!< PLL divided by 16 */

/* USART0 clock source selection */

#define CFG2_USART0SEL(regval) (BITS(0,1) & ((uint32_t)(regval) << 0))

#define RCU_USART0SRC_CKAPB2 CFG2_USART0SEL(0) /*!< CK_USART0 select CK_APB2 */

#define RCU_USART0SRC_CKSYS CFG2_USART0SEL(1) /*!< CK_USART0 select CK_SYS */

#define RCU_USART0SRC_LXTAL CFG2_USART0SEL(2) /*!< CK_USART0 select LXTAL */

#define RCU_USART0SRC_IRC8M CFG2_USART0SEL(3) /*!< CK_USART0 select IRC8M */

/* ADC clock source selection */

#define RCU_ADCSRC_IRC28M (uint32_t)0x00000000U /*!< ADC clock source select */

#define RCU_ADCSRC_AHB_APB2DIV RCU_CFG2_ADCSEL /*!< ADC clock source select */

/* IRC28M clock divider for ADC */

#define RCU_ADC_IRC28M_DIV2 (uint32_t)0x00000000U /*!< IRC28M/2 select to ADC clock */

#define RCU_ADC_IRC28M_DIV1 RCU_CFG2_IRC28MDIV /*!< IRC28M select to ADC clock */

/* Deep-sleep mode voltage */

#define DSV_DSLPVS(regval) (BITS(0,1) & ((uint32_t)(regval) << 0))

#define RCU_DEEPSLEEP_V_1_0 DSV_DSLPVS(0) /*!< core voltage is 1.0V in deep-sleep mode */

#define RCU_DEEPSLEEP_V_0_9 DSV_DSLPVS(1) /*!< core voltage is 0.9V in deep-sleep mode */

#define RCU_DEEPSLEEP_V_0_8 DSV_DSLPVS(2) /*!< core voltage is 0.8V in deep-sleep mode */

#define RCU_DEEPSLEEP_V_1_2 DSV_DSLPVS(3) /*!< core voltage is 1.2V in deep-sleep mode */

#define RCU_MODIFY(__delay) do{ \

volatile uint32_t i,reg; \

if(0 != __delay){ \

reg = RCU_CFG0; \

reg &= ~(RCU_CFG0_AHBPSC); \

/* CK_AHB = SYSCLK/2 */ \

reg |= RCU_AHB_CKSYS_DIV2; \

RCU_CFG0 = reg; \

for(i=0; i<__delay; i++){ \

} \

reg = RCU_CFG0; \

reg &= ~(RCU_CFG0_AHBPSC); \

reg |= RCU_AHB_CKSYS_DIV4; \

/* CK_AHB = SYSCLK/4 */ \

RCU_CFG0 = reg; \

for(i=0; i<__delay; i++){ \

} \

} \

}while(0)

#define SEL_IRC8M 0x00

#define SEL_HXTAL 0x01

#define SEL_PLL 0x02

#define NVIC_VECTTAB_RAM ((uint32_t)0x20000000U) /*!< RAM base address */

#define NVIC_VECTTAB_FLASH ((uint32_t)0x08000000U) /*!< Flash base address */

#define VECT_TAB_OFFSET (uint32_t)0x00 /* vector table base offset */

#define NVIC_VECTTAB_OFFSET_MASK ((uint32_t)0x1FFFFF80U) /*!< NVIC vector table offset mask */

static void _soft_delay_(uint32_t time)//延时

{

__IO uint32_t i;

for(i=0; i<time*10; i++){

}

}

void nvic_vector_table_set(uint32_t nvic_vict_tab, uint32_t offset)

{

SCB->VTOR = nvic_vict_tab | (offset & NVIC_VECTTAB_OFFSET_MASK);

__DSB();

}

static void system_clock_8m_irc8m(void)

{

uint32_t timeout = 0U;

uint32_t stab_flag = 0U;

__IO uint32_t reg_temp;

/* enable IRC8M */

RCU_CTL0 |= RCU_CTL0_IRC8MEN;

/* wait until IRC8M is stable or the startup time is longer than IRC8M_STARTUP_TIMEOUT */

do{

timeout++;

stab_flag = (RCU_CTL0 & RCU_CTL0_IRC8MSTB);

}

while((0U == stab_flag) && (IRC8M_STARTUP_TIMEOUT != timeout));

/* if fail */

if(0U == (RCU_CTL0 & RCU_CTL0_IRC8MSTB)){

while(1){

}

}

/* AHB = SYSCLK */

RCU_CFG0 |= RCU_AHB_CKSYS_DIV1;

/* APB2 = AHB */

RCU_CFG0 |= RCU_APB2_CKAHB_DIV1;

/* APB1 = AHB */

RCU_CFG0 |= RCU_APB1_CKAHB_DIV1;

reg_temp = RCU_CFG0;

/* select IRC8M as system clock */

reg_temp &= ~RCU_CFG0_SCS;

reg_temp |= RCU_CKSYSSRC_IRC8M;

RCU_CFG0 = reg_temp;

/* wait until IRC8M is selected as system clock */

while(RCU_SCSS_IRC8M != (RCU_CFG0 & RCU_CFG0_SCSS)){

}

}

static void system_clock_config(void)

{

#ifdef __SYSTEM_CLOCK_8M_HXTAL

system_clock_8m_hxtal();

#elif defined (__SYSTEM_CLOCK_72M_PLL_HXTAL)

system_clock_72m_hxtal();

#elif defined (__SYSTEM_CLOCK_72M_PLL_IRC8M_DIV2)

system_clock_72m_irc8m();

#elif defined (__SYSTEM_CLOCK_72M_PLL_IRC48M_DIV2)

system_clock_72m_irc48m();

#else

system_clock_8m_irc8m();

#endif /* __SYSTEM_CLOCK_8M_HXTAL */

}

void SystemInit (void)

{

/* enable IRC8M */

RCU_CTL0 |= RCU_CTL0_IRC8MEN;

while(0U == (RCU_CTL0 & RCU_CTL0_IRC8MSTB)){

}

if(((RCU_CFG0 & RCU_CFG0_SCSS) == RCU_SCSS_PLL)){

RCU_MODIFY(0x80);

}

RCU_CFG0 &= ~RCU_CFG0_SCS;

_soft_delay_(100);

RCU_CTL0 &= ~(RCU_CTL0_HXTALEN | RCU_CTL0_CKMEN | RCU_CTL0_PLLEN | RCU_CTL0_HXTALBPS);

/* reset RCU */

RCU_CFG0 &= ~(RCU_CFG0_SCS | RCU_CFG0_AHBPSC | RCU_CFG0_APB1PSC | RCU_CFG0_APB2PSC |\

RCU_CFG0_ADCPSC | RCU_CFG0_CKOUTSEL | RCU_CFG0_CKOUTDIV | RCU_CFG0_PLLDV);

RCU_CFG0 &= ~(RCU_CFG0_PLLSEL | RCU_CFG0_PLLMF | RCU_CFG0_PLLMF4 | RCU_CFG0_PLLDV);

RCU_CFG1 &= ~(RCU_CFG1_PREDV);

RCU_CFG2 &= ~(RCU_CFG2_USART0SEL | RCU_CFG2_ADCSEL);

RCU_CFG2 &= ~RCU_CFG2_IRC28MDIV;

RCU_CFG2 &= ~RCU_CFG2_ADCPSC2;

RCU_CTL1 &= ~RCU_CTL1_IRC28MEN;

RCU_INT = 0x00000000U;

/* configure system clock */

system_clock_config();

#ifdef VECT_TAB_SRAM

nvic_vector_table_set(NVIC_VECTTAB_RAM,VECT_TAB_OFFSET);

#else

nvic_vector_table_set(NVIC_VECTTAB_FLASH,VECT_TAB_OFFSET);

#endif

}

//gpio配置

#define GPIOA (GPIO_BASE + 0x00000000U)

#define GPIOB (GPIO_BASE + 0x00000400U)

#define GPIOC (GPIO_BASE + 0x00000800U)

#define GPIOF (GPIO_BASE + 0x00001400U)

/* GPIO pin definitions */

#define GPIO_PIN_0 BIT(0) /*!< GPIO pin 0 */

#define GPIO_PIN_1 BIT(1) /*!< GPIO pin 1 */

#define GPIO_PIN_2 BIT(2) /*!< GPIO pin 2 */

#define GPIO_PIN_3 BIT(3) /*!< GPIO pin 3 */

#define GPIO_PIN_4 BIT(4) /*!< GPIO pin 4 */

#define GPIO_PIN_5 BIT(5) /*!< GPIO pin 5 */

#define GPIO_PIN_6 BIT(6) /*!< GPIO pin 6 */

#define GPIO_PIN_7 BIT(7) /*!< GPIO pin 7 */

#define GPIO_PIN_8 BIT(8) /*!< GPIO pin 8 */

#define GPIO_PIN_9 BIT(9) /*!< GPIO pin 9 */

#define GPIO_PIN_10 BIT(10) /*!< GPIO pin 10 */

#define GPIO_PIN_11 BIT(11) /*!< GPIO pin 11 */

#define GPIO_PIN_12 BIT(12) /*!< GPIO pin 12 */

#define GPIO_PIN_13 BIT(13) /*!< GPIO pin 13 */

#define GPIO_PIN_14 BIT(14) /*!< GPIO pin 14 */

#define GPIO_PIN_15 BIT(15) /*!< GPIO pin 15 */

#define GPIO_PIN_ALL BITS(0,15) /*!< GPIO pin all */

/* registers definitions */

#define GPIO_CTL(gpiox) REG32((gpiox) + 0x00U) /*!< GPIO port control register */

#define GPIO_OMODE(gpiox) REG32((gpiox) + 0x04U) /*!< GPIO port output mode register */

#define GPIO_OSPD(gpiox) REG32((gpiox) + 0x08U) /*!< GPIO port output speed register */

#define GPIO_PUD(gpiox) REG32((gpiox) + 0x0CU) /*!< GPIO port pull-up/pull-down register */

#define GPIO_ISTAT(gpiox) REG32((gpiox) + 0x10U) /*!< GPIO port input status register */

#define GPIO_OCTL(gpiox) REG32((gpiox) + 0x14U) /*!< GPIO port output control register */

#define GPIO_BOP(gpiox) REG32((gpiox) + 0x18U) /*!< GPIO port bit operation register */

#define GPIO_LOCK(gpiox) REG32((gpiox) + 0x1CU) /*!< GPIO port configuration lock register */

#define GPIO_AFSEL0(gpiox) REG32((gpiox) + 0x20U) /*!< GPIO alternate function selected register 0 */

#define GPIO_AFSEL1(gpiox) REG32((gpiox) + 0x24U) /*!< GPIO alternate function selected register 1 */

#define GPIO_BC(gpiox) REG32((gpiox) + 0x28U) /*!< GPIO bit clear register */

#define GPIO_TG(gpiox) REG32((gpiox) + 0x2CU) /*!< GPIO port bit toggle register */

/* output mode definitions */

#define CTL_CLTR(regval) (BITS(0,1) & ((uint32_t)(regval) << 0))

#define GPIO_MODE_INPUT CTL_CLTR(0) /*!< input mode */

#define GPIO_MODE_OUTPUT CTL_CLTR(1) /*!< output mode */

#define GPIO_MODE_AF CTL_CLTR(2) /*!< alternate function mode */

#define GPIO_MODE_ANALOG CTL_CLTR(3) /*!< analog mode */

/* pull-up/pull-down definitions */

#define PUD_PUPD(regval) (BITS(0,1) & ((uint32_t)(regval) << 0))

#define GPIO_PUPD_NONE PUD_PUPD(0) /*!< floating mode, no pull-up and pull-down resistors */

#define GPIO_PUPD_PULLUP PUD_PUPD(1) /*!< with pull-up resistor */

#define GPIO_PUPD_PULLDOWN PUD_PUPD(2) /*!< with pull-down resistor */

/* GPIO mode configuration values */

#define GPIO_MODE_SET(n, mode) ((uint32_t)((uint32_t)(mode) << (2U * (n))))

#define GPIO_MODE_MASK(n) (0x3U << (2U * (n)))

/* GPIO pull-up/pull-down values */

#define GPIO_PUPD_SET(n, pupd) ((uint32_t)((uint32_t)(pupd) << (2U * (n))))

#define GPIO_PUPD_MASK(n) (0x3U << (2U * (n)))

void gpio_mode_set(uint32_t gpio_periph, uint32_t mode, uint32_t pull_up_down, uint32_t pin)

{

uint16_t i;

uint32_t ctl, pupd;

ctl = GPIO_CTL(gpio_periph);

pupd = GPIO_PUD(gpio_periph);

for(i = 0U; i < 16U; i++) {

if((1U << i) & pin) {

/* clear the specified pin mode bits */

ctl &= ~GPIO_MODE_MASK(i);

/* set the specified pin mode bits */

ctl |= GPIO_MODE_SET(i, mode);

/* clear the specified pin pupd bits */

pupd &= ~GPIO_PUPD_MASK(i);

/* set the specified pin pupd bits */

pupd |= GPIO_PUPD_SET(i, pull_up_down);

}

}

GPIO_CTL(gpio_periph) = ctl;

GPIO_PUD(gpio_periph) = pupd;

}

/* GPIO output type */

#define GPIO_OTYPE_PP ((uint8_t)(0x00U)) /*!< push pull mode */

#define GPIO_OTYPE_OD ((uint8_t)(0x01U)) /*!< open drain mode */

/* GPIO output speed values */

#define GPIO_OSPEED_SET(n, speed) ((uint32_t)((uint32_t)(speed) << (2U * (n))))

#define GPIO_OSPEED_MASK(n) (0x3U << (2U * (n)))

/* GPIO output max speed value */

#define OSPD_OSPD0(regval) (BITS(0,1) & ((uint32_t)(regval) << 0))

#define GPIO_OSPEED_2MHZ OSPD_OSPD0(0) /*!< output max speed 2MHz */

#define GPIO_OSPEED_10MHZ OSPD_OSPD0(1) /*!< output max speed 10MHz */

#define GPIO_OSPEED_50MHZ OSPD_OSPD0(3) /*!< output max speed 50MHz */

void gpio_output_options_set(uint32_t gpio_periph, uint8_t otype, uint32_t speed, uint32_t pin)

{

uint16_t i;

uint32_t ospeed;

if(GPIO_OTYPE_OD == otype) {

GPIO_OMODE(gpio_periph) |= (uint32_t)pin;

} else {

GPIO_OMODE(gpio_periph) &= (uint32_t)(~pin);

}

/* get the specified pin output speed bits value */

ospeed = GPIO_OSPD(gpio_periph);

for(i = 0U; i < 16U; i++) {

if((1U << i) & pin) {

/* clear the specified pin output speed bits */

ospeed &= ~GPIO_OSPEED_MASK(i);

/* set the specified pin output speed bits */

ospeed |= GPIO_OSPEED_SET(i, speed);

}

}

GPIO_OSPD(gpio_periph) = ospeed;

}

//IDX_AHBEN = 0x14U,

//#define RCU_REGIDX_BIT(regidx, bitpos) (((uint32_t)(regidx)<<6) | (uint32_t)(bitpos))

//RCU_GPIOC = RCU_REGIDX_BIT(IDX_AHBEN, 19U),// =0x513 /*!< GPIOC clock */

//void rcu_periph_clock_enable(rcu_periph_enum periph)

//{

// RCU_REG_VAL(periph) |= BIT(RCU_BIT_POS(periph));

//}

#define abc(aaa,bbb,ccc) aaa+bbb+ccc;

uint32_t c=0x513;

void GPIOC_clock_enable()

{

RCU_REG_VAL(c) |= BIT(RCU_BIT_POS(c));

}

void gpio_bit_set(uint32_t gpio_periph, uint32_t pin)

{

GPIO_BOP(gpio_periph) = (uint32_t)pin;

}

void gpio_bit_reset(uint32_t gpio_periph, uint32_t pin)

{

GPIO_BC(gpio_periph) = (uint32_t)pin;

}

int main(void){

//SystemInit();

GPIOC_clock_enable();

// 配置GPIOC13为上拉推挽输出模式

gpio_mode_set(GPIOC, GPIO_MODE_OUTPUT, GPIO_PUPD_PULLUP, GPIO_PIN_13);

gpio_output_options_set(GPIOC, GPIO_OTYPE_PP, GPIO_OSPEED_2MHZ, GPIO_PIN_13);

gpio_bit_reset(GPIOC,GPIO_PIN_13);

gpio_bit_set(GPIOC,GPIO_PIN_13);

while(1){ gpio_bit_set(GPIOC,GPIO_PIN_13);

};

}

1258

1258

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?