实验七:集成电路版图识别与提取

作者: Saint

掘金:https://juejin.im/user/5aa1f89b6fb9a028bb18966a

微博:https://weibo.com/5458277467/profile?topnav=1&wvr=6&is_all=1

GitHub:github.com/saint-000

一、实验原理:

二、实验目的:

本实验是基于微电子技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,为IC设计性实验。其目的在于:

了解对塑封、陶瓷封装等不同封装形式的芯片解剖的方法及注意事项。

学习并掌握集成电路版图的图形识别、电路拓扑结构提取。

能对提取得到的电路进行功能分析、确定,并可运用PSPICE等ICCAD工具展开模拟仿真。

三、实验内容:

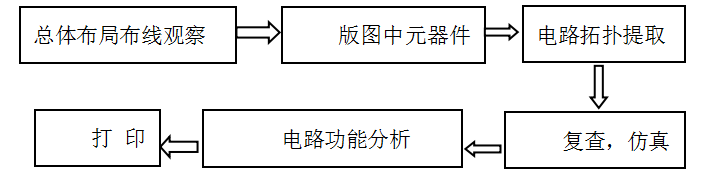

1、仔细观察芯片图形总体的布局布线,找出电源线、地线、输入端、输出端及其对应的压焊点。

2、判定此IC采用P阱还是N阱工艺;进行版图中元器件的辨认,要求分出MOS管、多晶硅电阻和MOS电容。

3、根据以上的判别依据,提取芯片上图形所表示的电路连接拓扑结构;复查,加以修正;完成电路的提取,并分析电路功能,应用Visio或Cadence等软件对电路进行复原。

四、实验器材:

(1)工作站或微机终端 1台

(2)芯片显微图片 1张

(3)版图编辑软件 1套

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?