本实验采用

UART

(

Universal Asynchronous Receiver Transmitter

)

接口。

UART

为低速接口,双工通信,在收发方向上采用相同的通信方式。

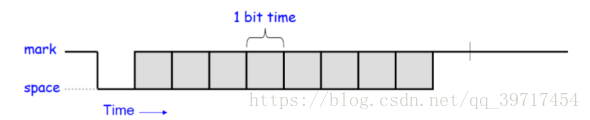

如图 所示, 空闲时, 信号处于高电平状态。当进行数据传输时,首先是 1 位起始位(低电平),然后是 8 位数据位,最后是 1 位终止位(高电平)。由于接口是串口,因此要进行“串行改并行”的操作。具体来说, rx 信号作为输入信号,每次只能传输一个二进制位,而接口控制器在进行操作时,根据状态寄存器来判断是否已经接收完了一个 8 位的数据,只在 8 位输入结束后将 8 位数据一起取走。从而完成了“串行改并行”。

根据实验要求,信号波特率为 9600 , AXI 总线的时钟频率为 100MHz , 需要对时钟信号进行分频。这一部分逻辑在 gps_v1_0_S00_AXI.v (见附录) 中实现。定义变量 CLOCK_DIVIDER ,其计算方式为:

CLOCK_DIVIDER = clock rate / (baud rate * bit width)

针对读数据过程,定义变量 tx_clk_divider ,每个时钟周期减 1,当该变量为 0 时,进入状态转移和操作的逻辑,并将该变量置为 CLOCK_DIVIDER 并重新开始计数。为了保证在波形的中间读数,设置变量 rx_countdown 。每一个 bit 的位宽度为 4 ,在进行状态转移和操作的时候,可以同时对该变量进行赋值。 由此可以控制两次操作之间的时

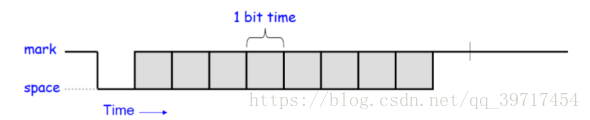

如图 所示, 空闲时, 信号处于高电平状态。当进行数据传输时,首先是 1 位起始位(低电平),然后是 8 位数据位,最后是 1 位终止位(高电平)。由于接口是串口,因此要进行“串行改并行”的操作。具体来说, rx 信号作为输入信号,每次只能传输一个二进制位,而接口控制器在进行操作时,根据状态寄存器来判断是否已经接收完了一个 8 位的数据,只在 8 位输入结束后将 8 位数据一起取走。从而完成了“串行改并行”。

根据实验要求,信号波特率为 9600 , AXI 总线的时钟频率为 100MHz , 需要对时钟信号进行分频。这一部分逻辑在 gps_v1_0_S00_AXI.v (见附录) 中实现。定义变量 CLOCK_DIVIDER ,其计算方式为:

CLOCK_DIVIDER = clock rate / (baud rate * bit width)

针对读数据过程,定义变量 tx_clk_divider ,每个时钟周期减 1,当该变量为 0 时,进入状态转移和操作的逻辑,并将该变量置为 CLOCK_DIVIDER 并重新开始计数。为了保证在波形的中间读数,设置变量 rx_countdown 。每一个 bit 的位宽度为 4 ,在进行状态转移和操作的时候,可以同时对该变量进行赋值。 由此可以控制两次操作之间的时

本文介绍了一个基于AXI总线的GPS导航系统ipcore设计,使用四个32位寄存器处理数据。slv_reg0存放读取数据,slv_reg2的状态寄存器用于指示接收错误和完成状态。特别地,通过temp变量解决received状态短暂无法读取的问题。在仿真中,系统接收"0110110111"信号,当rx为低电平时开始接收,数据存入rx_byte寄存器,接收完成后received变为1。后续可扩展至20位数据接收。

本文介绍了一个基于AXI总线的GPS导航系统ipcore设计,使用四个32位寄存器处理数据。slv_reg0存放读取数据,slv_reg2的状态寄存器用于指示接收错误和完成状态。特别地,通过temp变量解决received状态短暂无法读取的问题。在仿真中,系统接收"0110110111"信号,当rx为低电平时开始接收,数据存入rx_byte寄存器,接收完成后received变为1。后续可扩展至20位数据接收。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

17

17

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?