Verilog学习之路(11)—事件控制(时间延迟)

一、前言

事件控制是为行为语句的执行指定触发事件的信号延迟方式。

事件控制可以分为边沿触发事件控制和电平敏感事件控制。

边沿触发事件控制方式是指在指定的信号变化时刻,即指定的信号跳变边沿才触发语句的执行,而当信号处于稳定状态下时则不会触发语句的执行。

电平敏感事件是在指定的条件表达式为真时启动需要执行的语句。

二、事件表达式

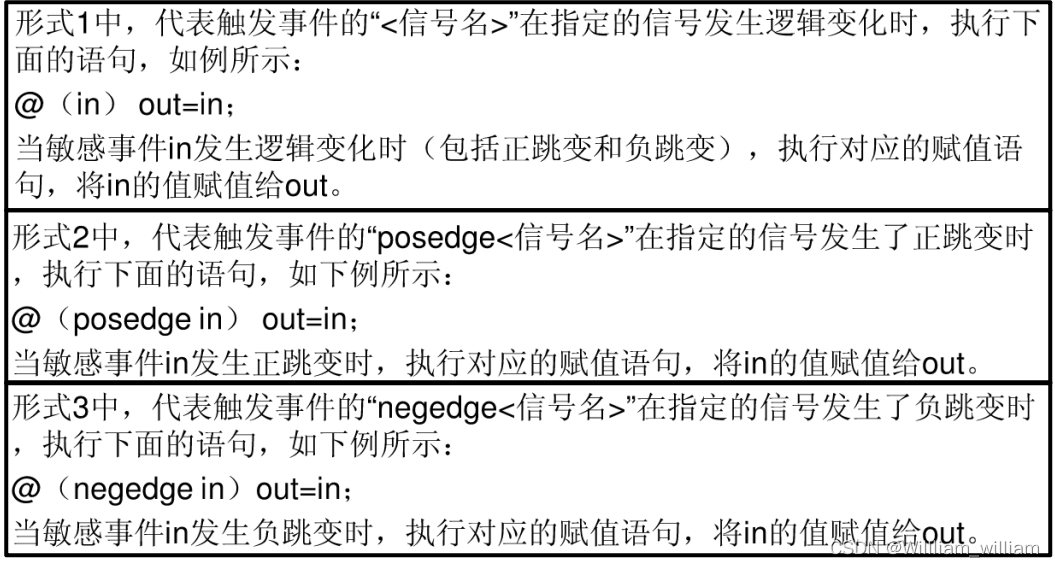

一个事件表达式可以以三种形式出现:

形式1: <信号名>

形式2: posedge<信号名>

形式3: negedge<信号名>

其中, <信号名> 可以是任何数据类型的标量或矢量。

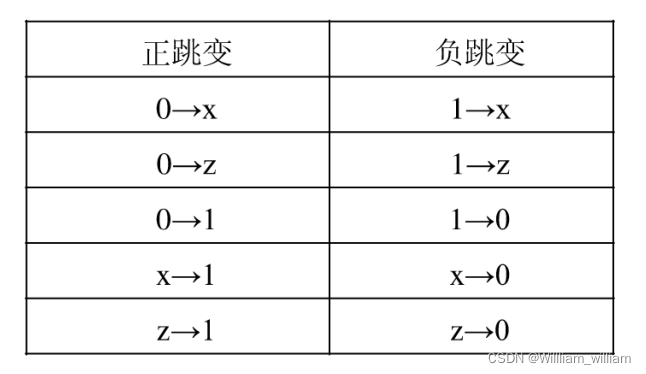

VerilogHDL中规定的正跳变和负跳变如下所示:

三、边沿触发事件控制

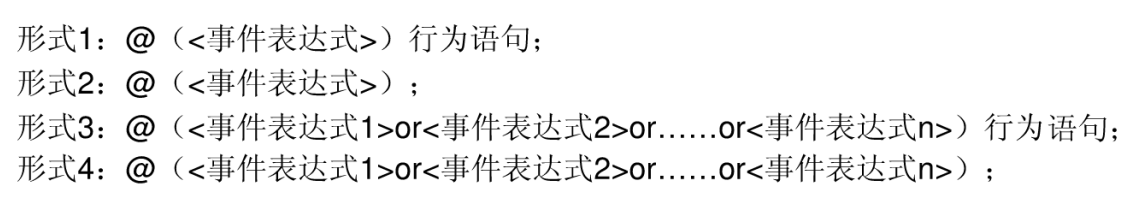

边沿触发事件控制的语法格式有如下四种形式:

1、形式1

@(<事件表达式>) 行为语句;

这种语法格式的敏感事件列表内只包含了一个触发事件,只有当这个指定的触发事件发生之后,后面的语句才能启动执行。如下所示的时钟脉冲计数器的示例中,触发事件时钟信号"clk"发生正跳变时,计数寄存器count_out增加1。

module clk_counter(clk, count_out);

input clk;

output reg [3:0] count_out;

initial count_out = 0;

always@(posedge clk)

counter_out = counter_out +1;

endmodule

2、形式2

@(<事件表达式>);

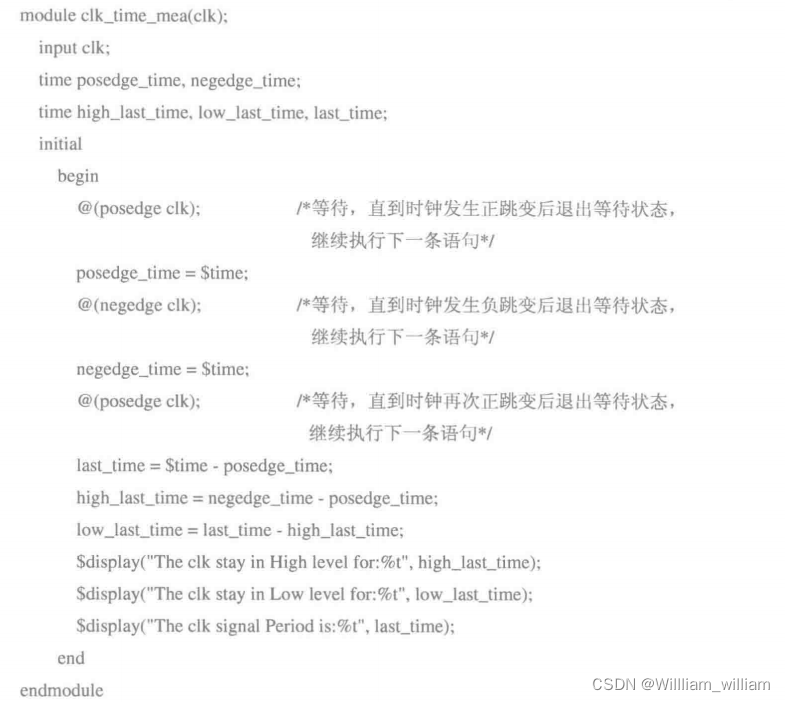

这种语法格式的敏感事件列表内只包含了一个触发事件,没有行为语句来指定触发事件发生时要执行的操作。用于测定输入时钟正电平、负电平持续时间以及时钟周期的模块示例如下所示:

3、形式3

@(<事件表达式1> or <事件表达式2> or ... or <事件表达式n>) 行为语句;

这种语法格式的敏感事件列表内指定了由不同<事件表达式>代表的多个触发事件,这些<事件表达式>之间要用关键词or组合起来,只要这些触发事件中的任何一个得到发生,就启动行为语句的执行。

3、形式4

@(<事件表达式1> or <事件表达式2> or ... or <事件表达式n>);

同第三种语法格式一样,这种语法格式内指定了多个触发事件,但是这种格式中没有行为语句。

四、电平敏感事件控制

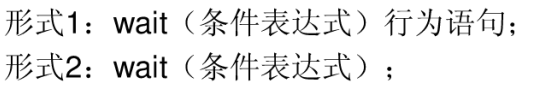

电平敏感事件控制用关键词wait来表示。电平敏感事件控制的语法格式如下所示:

电平敏感事件控制的第一种形式中包含了行为语句,它可以时串行块(begin-end)语句或并行块(fork-join)语句,也可以是单条行为语句。如下所示:

wait(enable==1) begin

d = a&b;

d = d|c;

end

wait语句的作用是根据条件表达式的真假来控制下面begin-end语句块的执行,在使能信号enable变为高电平后,也就是enable==1的语句为真时进行a,b,c之间的与或操作;若使能信号enable未变为高电平,则begin-end语句块的执行需要等到enable变为高电平之后才开始执行。

五、附录

上一篇:Verilog学习之路(10)—仿真使用的系统任务

下一篇:

1841

1841

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?