1、第一次使用VCU128,发现很坑,记录一下使用方法。

①首先需要在购买的包装盒子中找到密匙去官网下载个license

②在Vivado 2019.1版本中将2019.2的板卡数据导入,很奇怪把哈哈哈哈。下面是下载链接

https://github.com/Xilinx/XilinxBoardStore/tree/2019.2/boards/Xilinx/vcu128 https://github.com/Xilinx/XilinxBoardStore/tree/2019.2/boards/Xilinx/vcu128导入地址为 x:\xxx\2019.1\data\boards\board_files

https://github.com/Xilinx/XilinxBoardStore/tree/2019.2/boards/Xilinx/vcu128导入地址为 x:\xxx\2019.1\data\boards\board_files

2、上位机软件使用方法

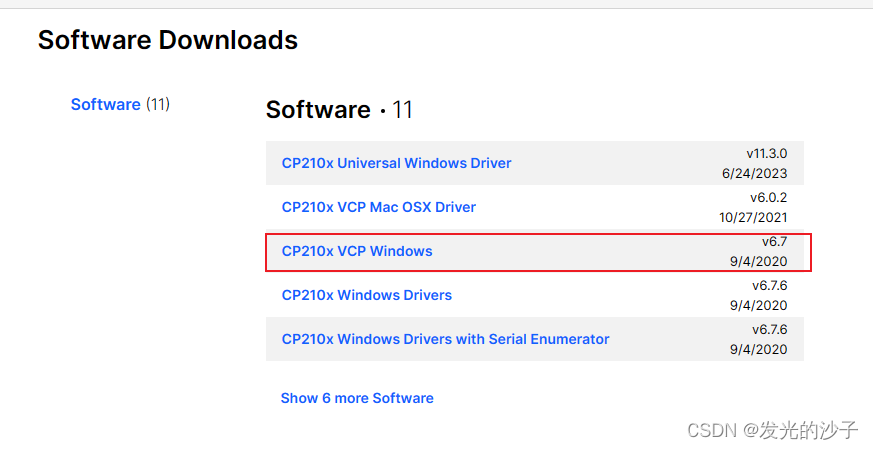

①首先需要安装cp120x驱动程序

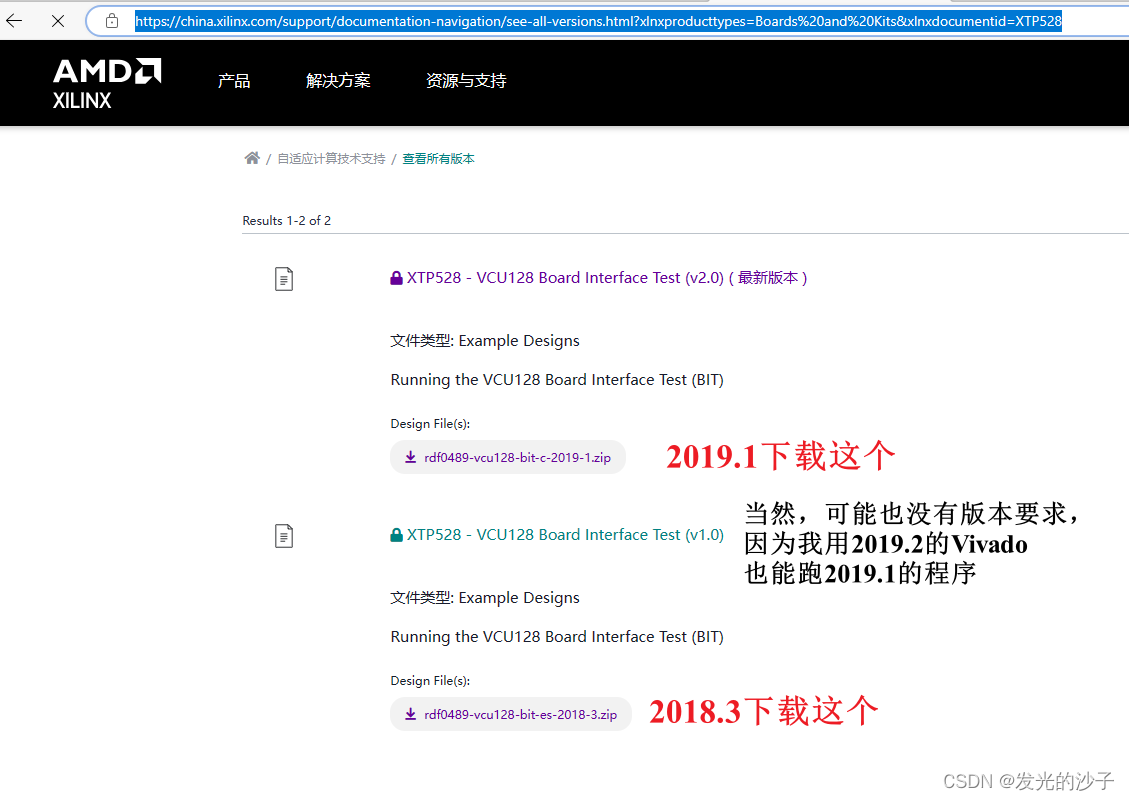

②下载scui程序

查看所有版本 https://china.xilinx.com/support/documentation-navigation/see-all-versions.html?xlnxproducttypes=Boards%20and%20Kits&xlnxdocumentid=XTP528

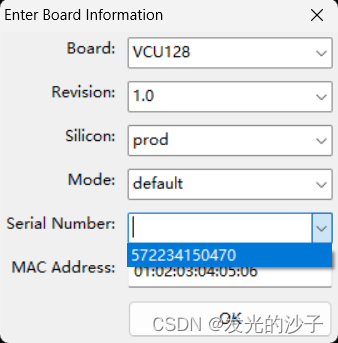

https://china.xilinx.com/support/documentation-navigation/see-all-versions.html?xlnxproducttypes=Boards%20and%20Kits&xlnxdocumentid=XTP528 ②解压后打开BoardUI.exe,如果驱动安装正确,则serial number可以被自动识别。然后点击ok按钮。

②解压后打开BoardUI.exe,如果驱动安装正确,则serial number可以被自动识别。然后点击ok按钮。

如果是ES版本,Board就选择VCU128;

如果是production版本,就选择Board就选择VCU128_PROD;一般应该选这VCU128_PROD。

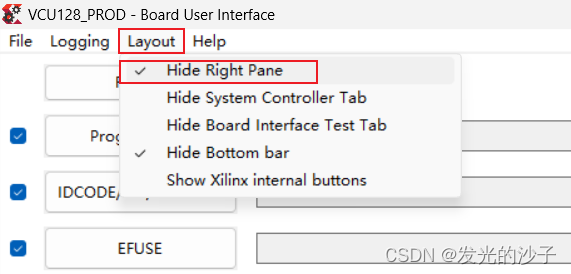

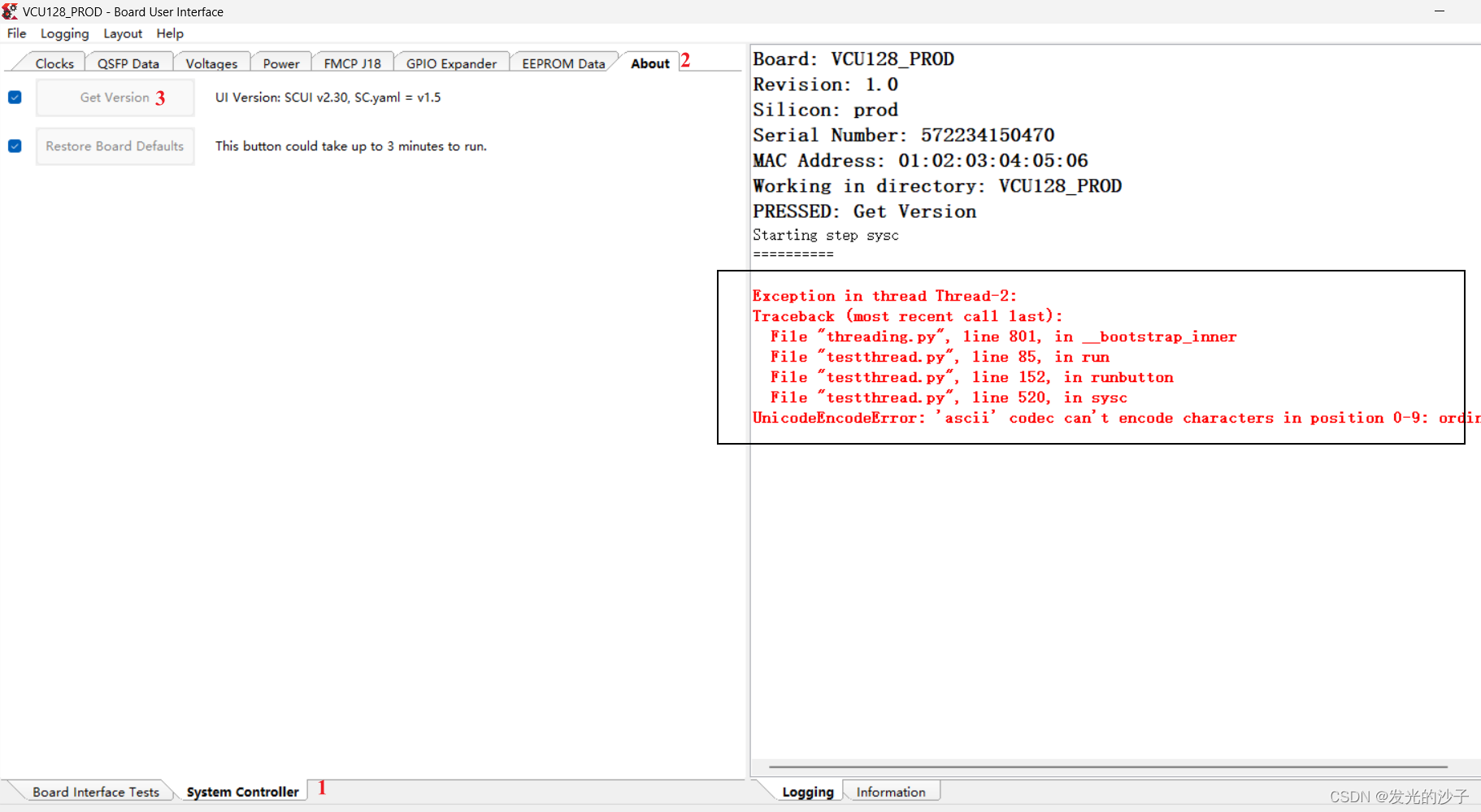

③打开侧边日志

④点击获取版本,可以看到如下错误。这是由于本软件是基于Python开发的,且开发人员是外国人,他并没有将 # -*- coding: UTF-8 -*- 写入文件。

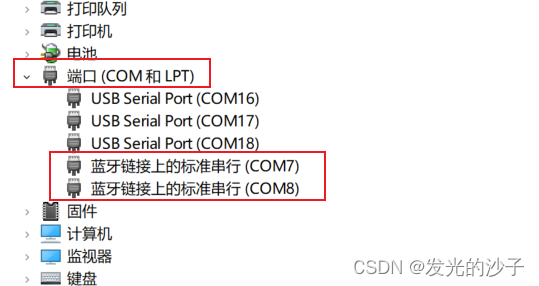

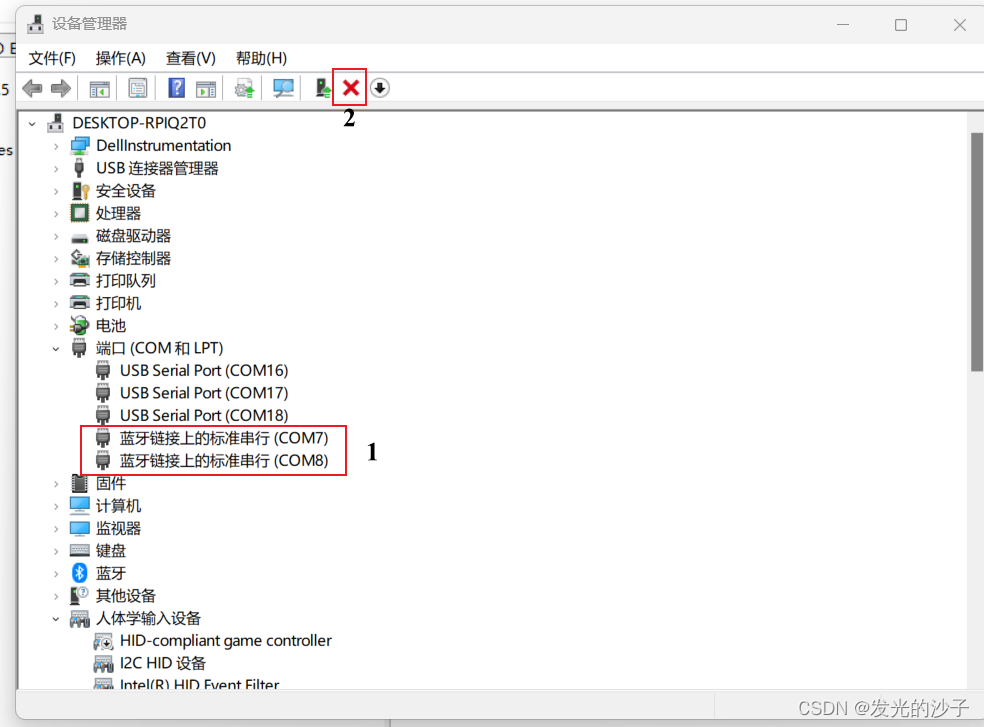

⑤打开设备管理的端口,端口下的所有除英文外的设备卸载,这里注意,只是卸载,千万不要删除驱动。

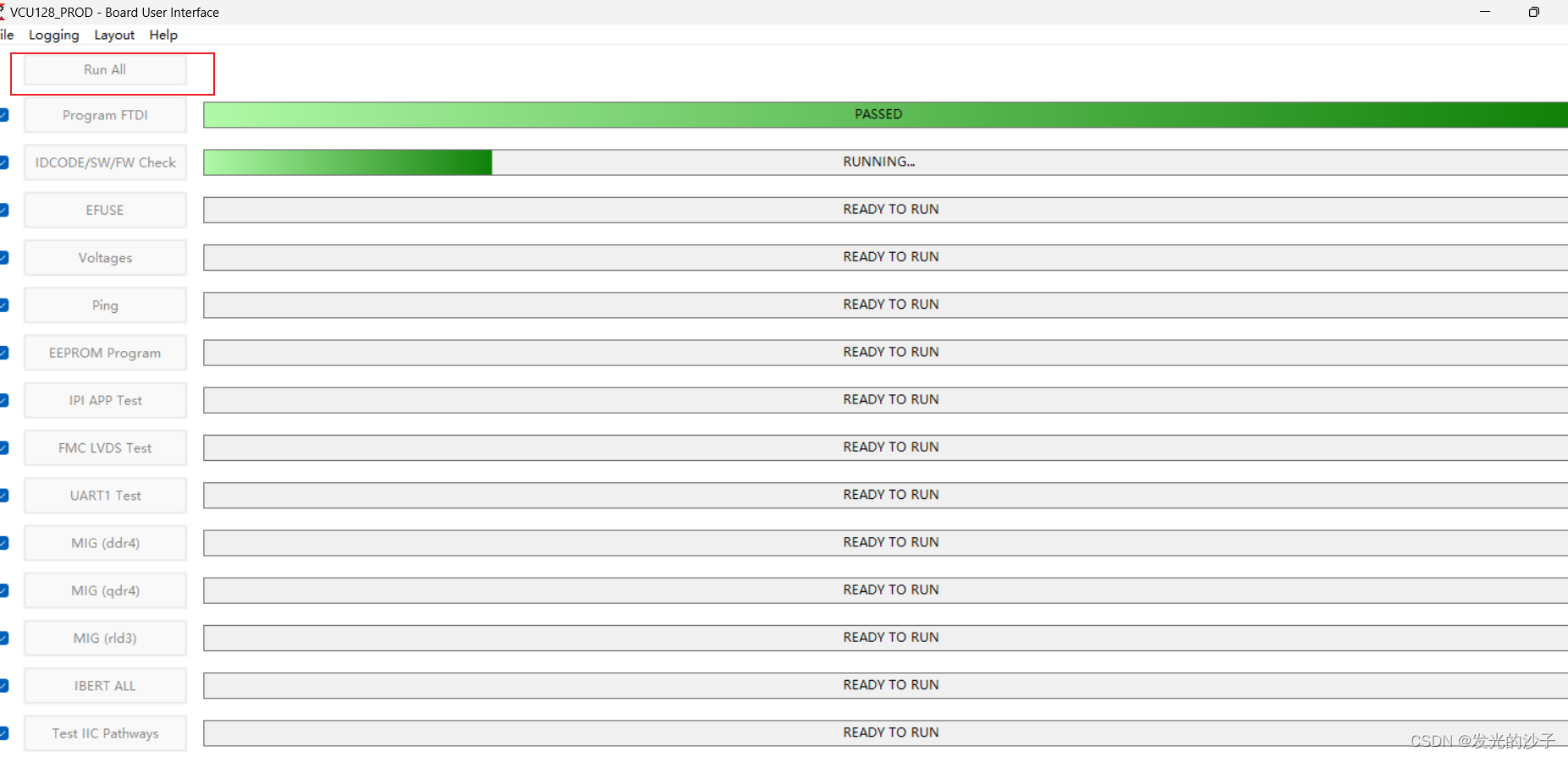

⑥关闭SCUI重新打开,点击RunAll

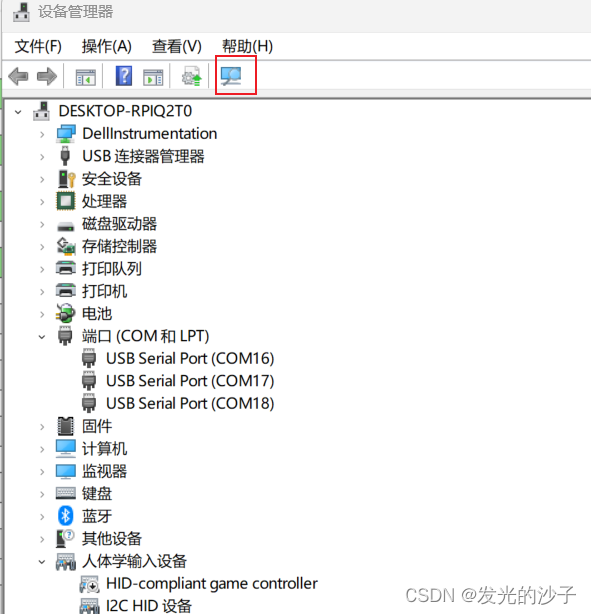

⑦如果想要恢复驱动,点击这个按钮即可

安装这个6.7版本的

安装这个6.7版本的

3684

3684

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?