3.1 IO约束

IO约束可以抽象为Lunch Reg Capture模型,只不过对于片外的Reg,路径时无法报告出来,需要根据场景查询对接器件的手册,器件手册会写明器件的延时信息等,再根据板级走线设计,估算出外部时序路径延时,通过Input Delay或者Output Delay模拟片外过约加严场景。常见的IO约束场景包括:input delay,时钟数据随路或者时钟数据回环;Output Delay包括时钟数据随路或者时钟数据回环。

3.1.1 Input Delay 随路场景

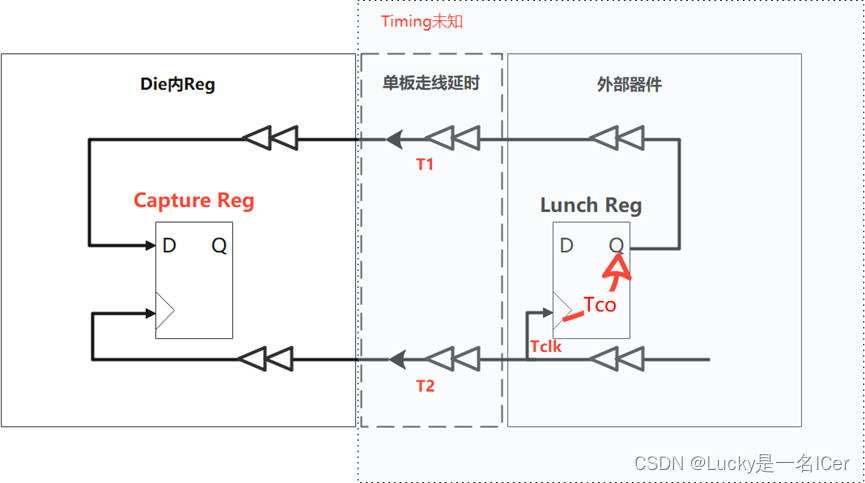

如图3.1.1.1所示为时钟数据随路场景,die内作为Slave,片外作为Master,测试die内从IO进入的路径都是已知的,可以通过Time Prime报告分析出来,而对于片外的Master,工具未知Timing,因此通过Set Input Delay设置过约束加严。

如图3.1.1.1所示,时钟信号和数据信号由外部器件给出,外部器件作为Master,将数据从随路时钟打给Die内寄存器,数据和随路时钟经过板级走线,通过IO进入Die内部,因为从IO到Die内reg的路径已知,因

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

844

844

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?