通用移位寄存器的设计

- 实验目的:

学习时序逻辑电路,学习寄存器的原理,学习VHDL语言。

- 实验内容:

编写一个8位的模式可控的移位寄存器的VHDL 代码并编译,仿真。

- 实验环境

PC 机(Pentium100 以上)、Altera Quartus II 6.0 CPLD/FPGA 集成开发环境。

- 实验原理

本实验就是设计一个模式可控的移位寄存器,该寄存器可以对8位信号通过MD输入端控制移位输出的模式,其功能表如表7-1所示。

模式可控移位寄存器功能表

|

CLK |

MD |

状态 |

|

↑ |

001 |

带进位循环左移 |

|

↑ |

010 |

带进位循环右移 |

|

↑ |

011 |

自循环左移 |

|

↑ |

100 |

自循环右移 |

|

↑ |

101 |

加载待移数据 |

|

↑ |

其他 |

保持 |

实验步骤:

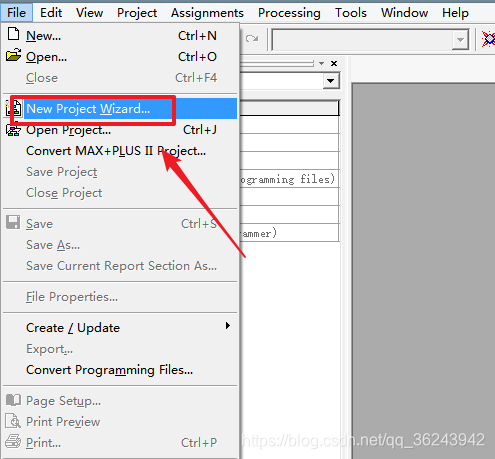

1.使用工程向导新建一个工程

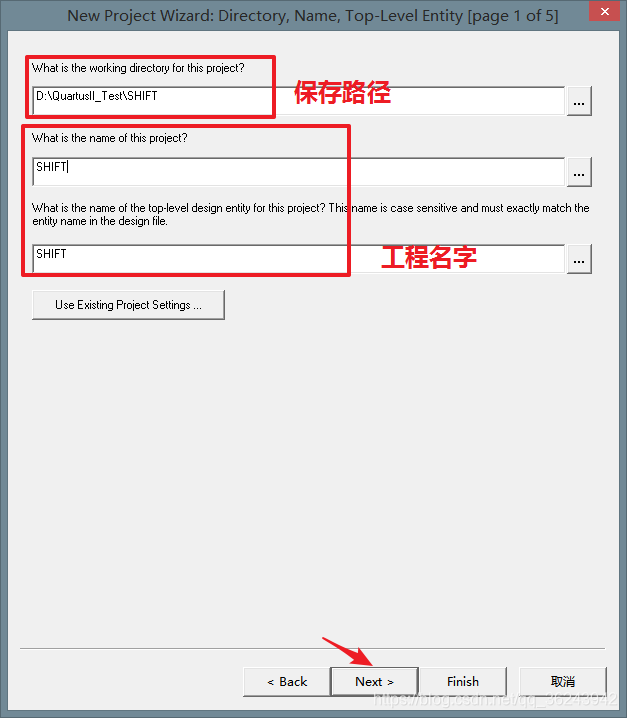

2.设置工程路径和工程名字

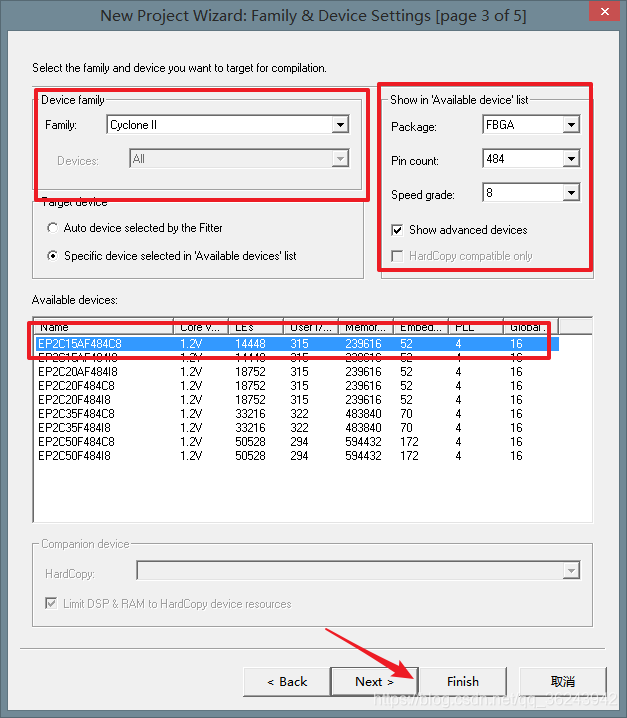

3.选择器件类型:

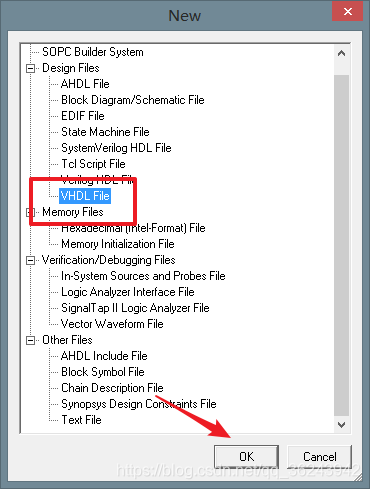

4.新建一个VHDL文件:

5.代码如下:

library ieee;

use ieee.std_logic_1164.all;

entity SHIFT is

port(

CLK,C0 :in std_logic;

MD :in std_logic_vector(2 downto 0);

D :in std_logic_vector(7 downto 0);

QB :out std_logic_vector(7 downto 0);

CN :out std_logic);

end entity SHIFT;

architecture BHV of SHIFT is

signal REG : std_logic_vector(7 downto 0);

signal CY : std_logic;

begin

process(CLK,MD,C0)

begin

if CLK'EVENT AND CLK='1' then

case MD is

when "001" =>REG(0)<=C0;

REG(7 downto 1)<=REG(6 downto 0); CY<=REG(7);

when "010" =>REG(7)<=C0;

REG(6 downto 0)<=REG(7 downto 1); CY<=REG(7);

when "011" =>REG(0)<=REG(7);

REG(7 downto 1)<=REG(6 downto 0); CY<=REG(7);

when "100" =>REG(7)<=REG(0);

REG(6 downto 0)<=REG(7 downto 1); CY<=REG(7);

when "101" =>REG(7 downto 0)<= D(7 downto 0);

when others =>REG<=REG; CY<=CY;

end case;

end if;

end process;

QB(7 downto 0)<=REG(7 downto 0); CN<=CY;

end BHV;

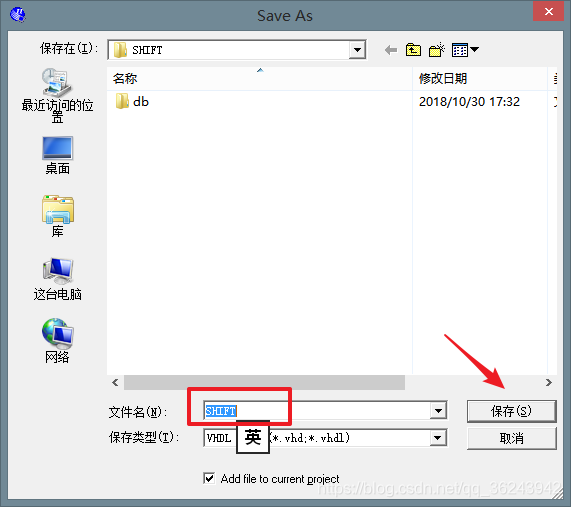

6.保存程序

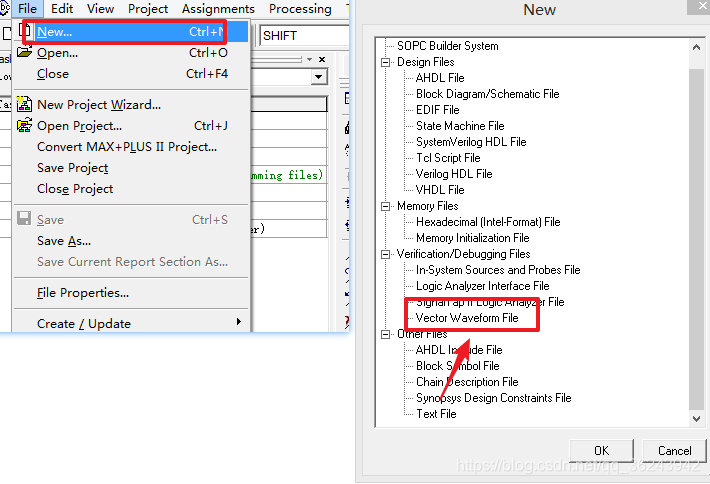

7.新建仿真文件

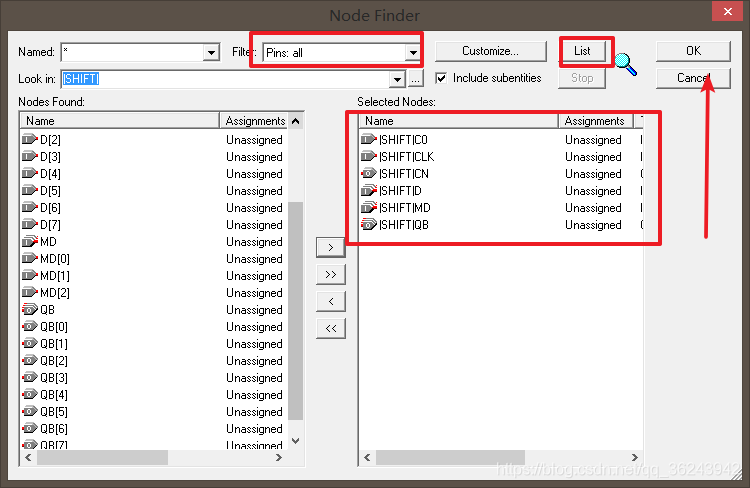

8.添加数据节点,然后设置时钟等参数保存仿真文件

9.波形仿真

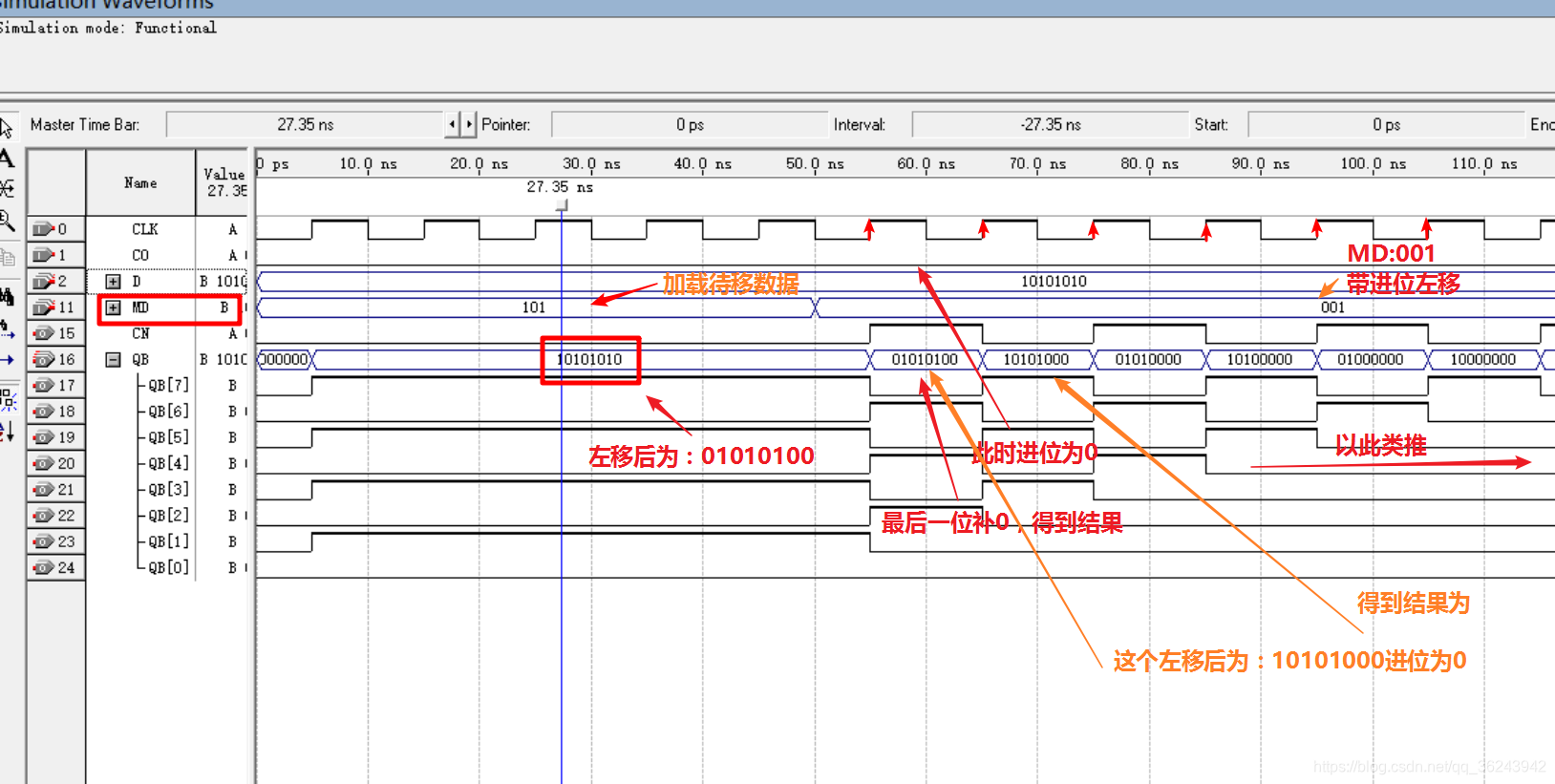

1.先使MD为101加载待移数据,然后时MD为001带进位左移:

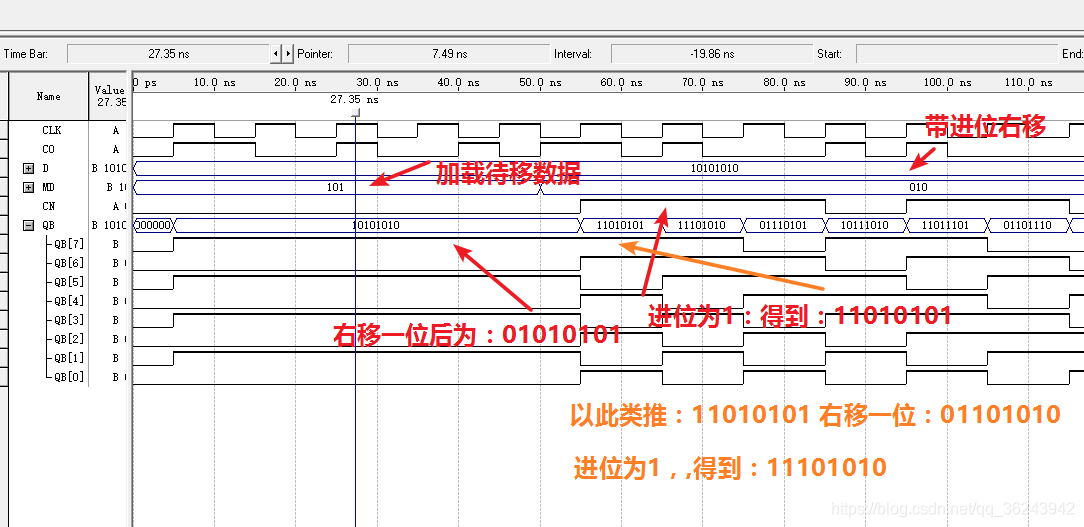

2.先使MD为101加载待移数据,然后时MD为010带进位右移:

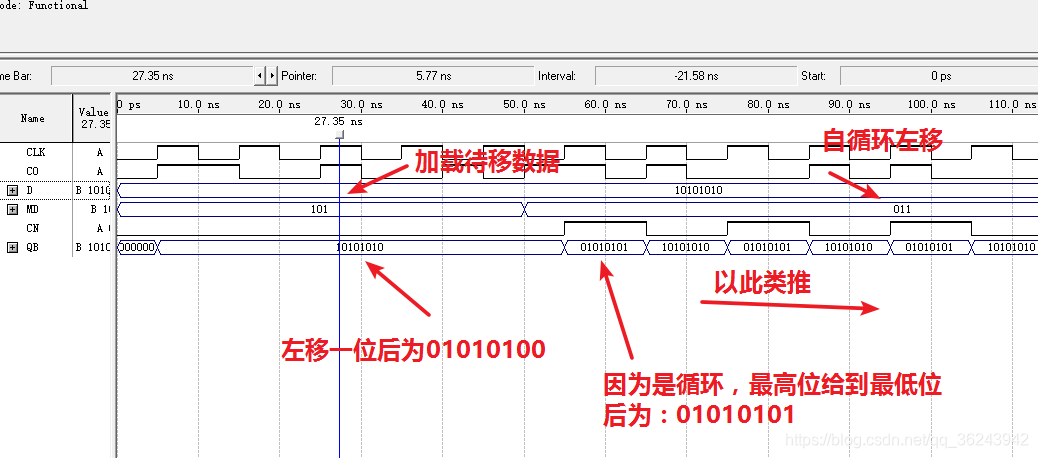

3.先使MD为101加载待移数据,然后时MD为011自循环左移:

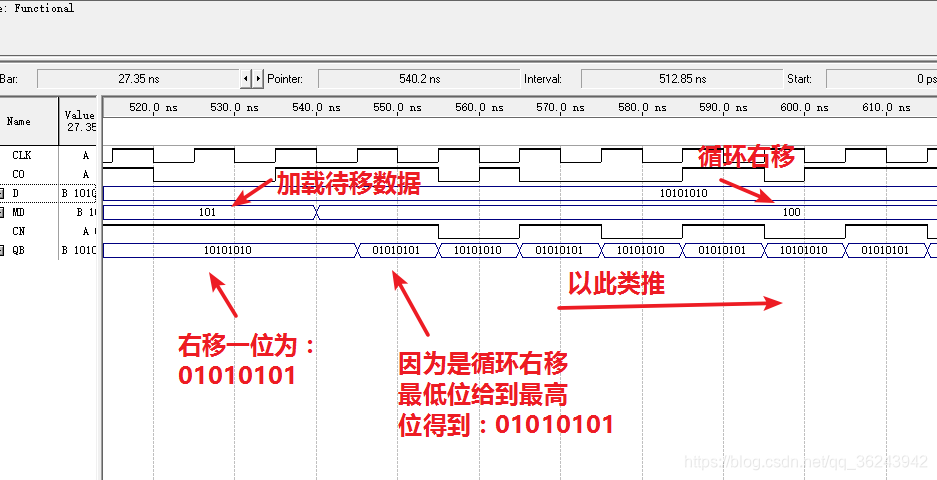

3.先使MD为101加载待移数据,然后时MD为100自循环左移:

本实验介绍了一个模式可控的8位移位寄存器设计,使用VHDL语言实现,可在不同模式下进行循环左移、循环右移、自循环移位及加载数据。实验基于AlteraQuartusII6.0CPLD/FPGA集成开发环境。

本实验介绍了一个模式可控的8位移位寄存器设计,使用VHDL语言实现,可在不同模式下进行循环左移、循环右移、自循环移位及加载数据。实验基于AlteraQuartusII6.0CPLD/FPGA集成开发环境。

1269

1269

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?