静态时序分析

静态时序分析是数字IC笔试和面试中常考的题目之一,主要考察参试者对时序电路建立时间和保持时间的理解,题目常考的点:

- 电路中是否存在时序违规

- 找出关键路径

- 计算最大时钟频率

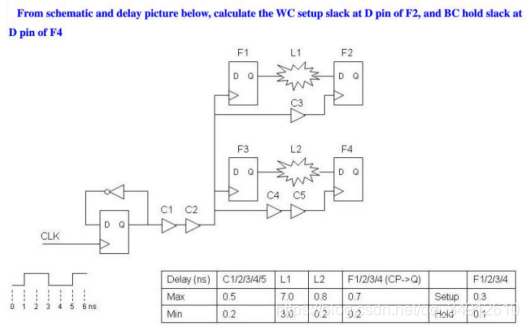

题目

- 题目解读:

求F2最坏情况下的保持时间裕量;

求F4最好情况下的建立时间裕量。 - 计算前的准备

F1/2/3/4时钟频率:由图可知,F1/2/3/4的时钟端口由一个二分频电路驱动,时钟频率为8ns。

F2-F1之间的Tskew: 0.2~0.5

F4-F3之间的Tskew: 0.4~1 - 写公式:

建立时间:Tcq + Tdelay <= Tclk + Tskew - Tsetup

所以最坏的建立时间裕量:setup slack = (Tclk + Tskew)min -( Tsetup + Tcq + Tdelay)max = 8 + 0.2 - 0.3 - 0.7 - 7 = 0.2

保持时间:Tcq +

静态时序分析在数字IC设计中至关重要,常用于评估时序电路的建立时间和保持时间。本文通过一道具体题目,解析如何确定关键路径、计算最大时钟频率,并分析保持时间裕量和建立时间裕量。最终,通过实例展示了分析过程。

静态时序分析在数字IC设计中至关重要,常用于评估时序电路的建立时间和保持时间。本文通过一道具体题目,解析如何确定关键路径、计算最大时钟频率,并分析保持时间裕量和建立时间裕量。最终,通过实例展示了分析过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3036

3036

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?