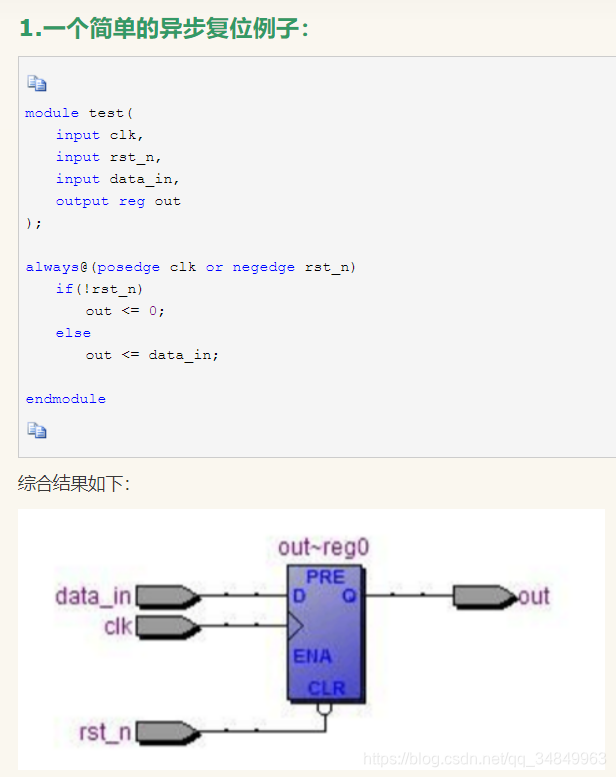

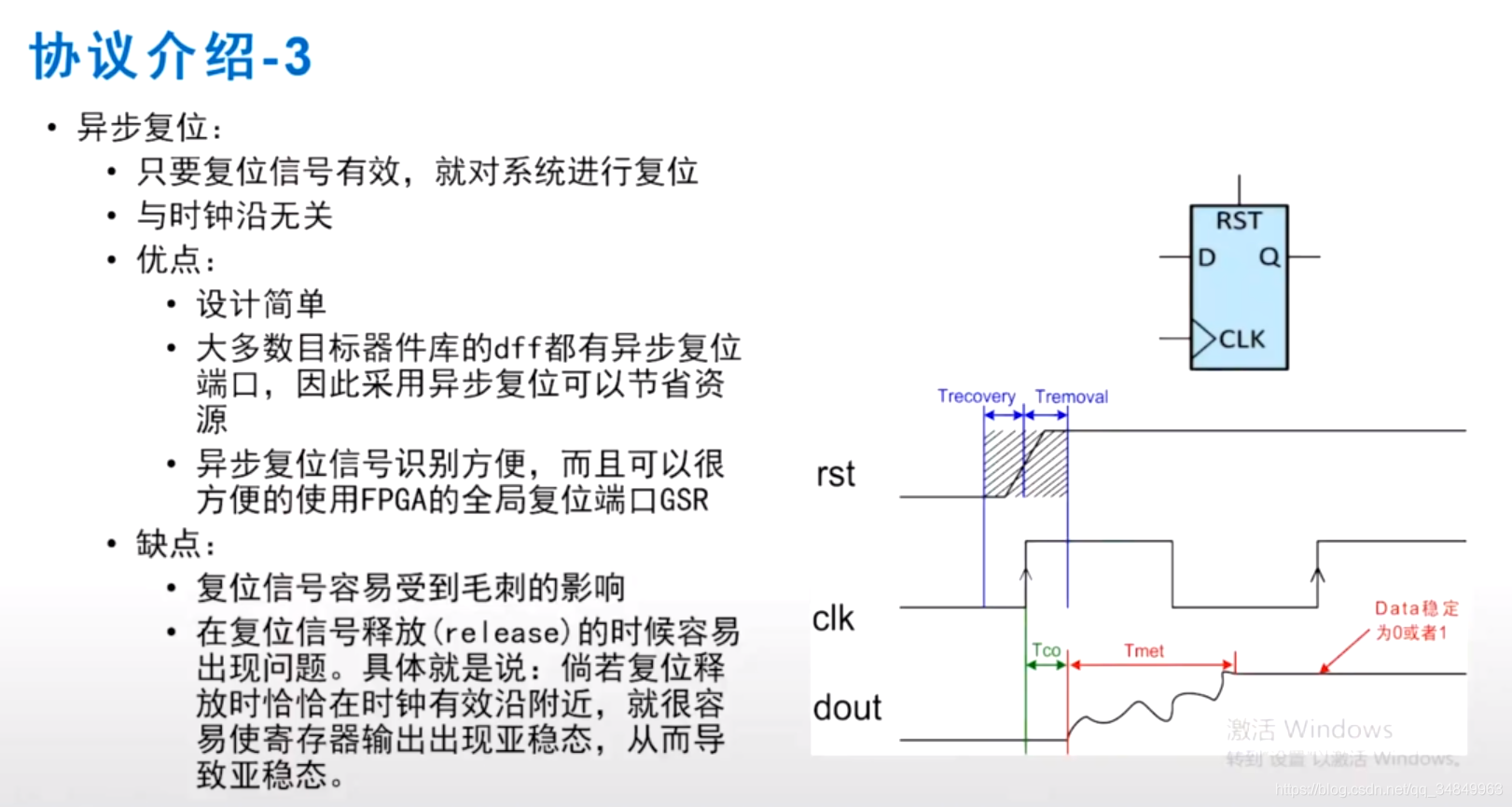

一、异步复位

verilog代码

always@(posedge clk or negedge rst_n)

if(!rst_n)

b <= 1'b0;

else

b <= a;

为何设计简单,节省资源?

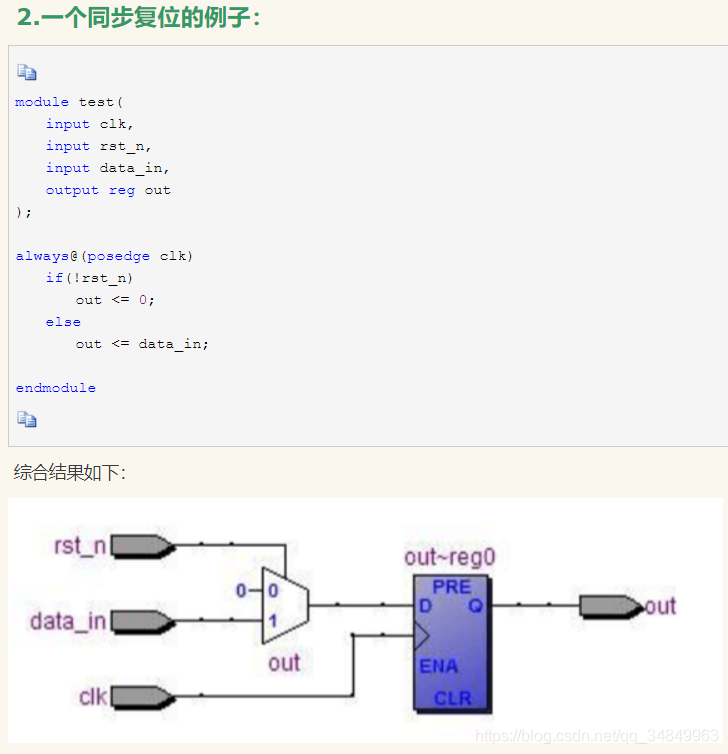

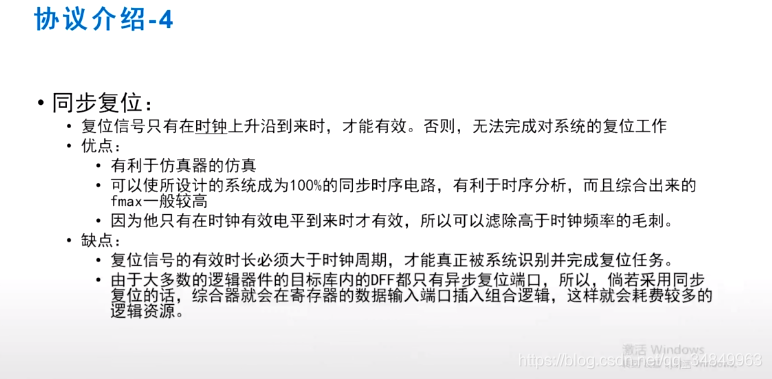

异步复位设计中,低电平有效得rst_n复位信号直接连接到端口上,节省资源。而同步复位综合得结果会在if语句中出现一个选择器,rst复位信号作为逻辑信号的使能信号,会开销资源。

二、同步复位

verilog代码

always@(posedge clk)

if(!rst_n)

b <= 1'b0;

else

b <= a;

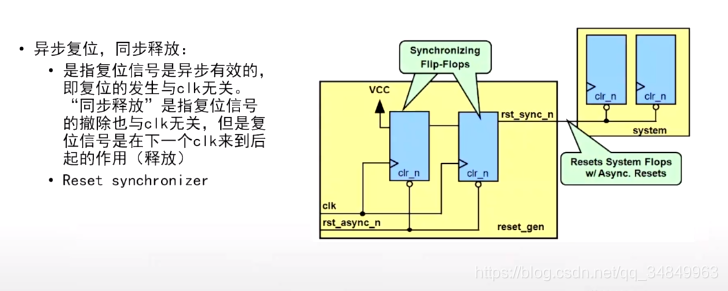

三、异步复位同步释放

2432

2432

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?