485自动收发电路(发零不发一电路)

RS-485是一种基于差分信号传送的串行通信链路层协议。它解决了RS-232协议传输距离太近(15m)的缺陷,是工业上广泛采用的较长距离数据通信链路层协议。

由于它使用一对双绞线传送差分信号,属半双工通信,所以需要进行接收和发送状态的转换。市场上485转化芯片有很多 3peak MAX485等等。

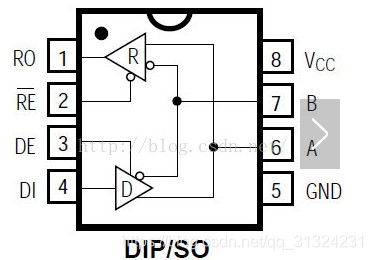

引脚图如图所示

引脚定义如下:

RO——接收数据的 TTL电平输出

RE非 ——低电平有效的接受允许

DE——高电平有效的发送允许

DI——发送数据的TTL电平输入

A——485差分信号的正向端

B——485差分信号的反向端的

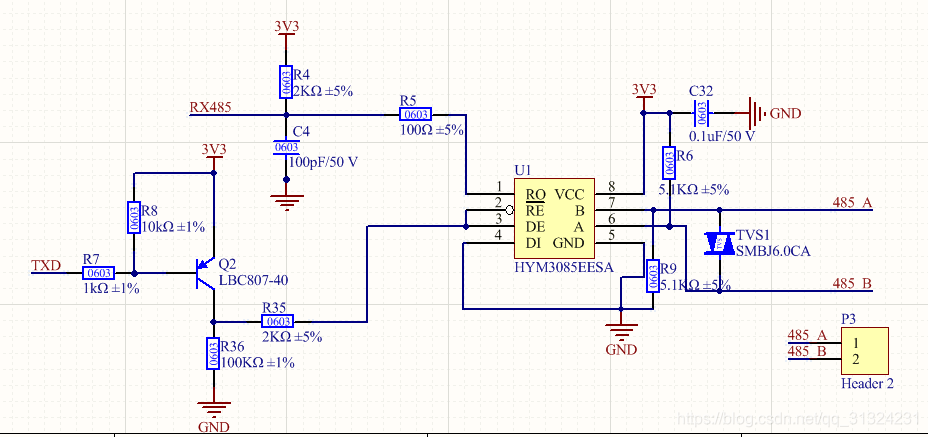

上图为一个简单的自动收发电路(亲测可用)

发送:

当TXD为0时,三极管Q2导通,DE为高电平,发送使能,DI接地所以发送1;当TXD为1时,三极管Q2截止,由R36将DE/RE非拉低,接收使能,此时485 AB端呈现高阻态,有外部的R9和R36的上下拉产生差分信号,总线发送1.

接收:

此时TXD默认上拉到高电平,处于接收态,接收总线上的差分信号。

此时有一个bug,就是在发送1的时候,芯片处于接收态,会不会有信号倒回,答案是不会,因为485是一个半双工的通信方式及发送接收不能同时进行。

也可以这样理解由于RS-485芯片处于接收状态,此时的发送信号必须是在总线上其它节点发送数据时,才能将高电平信号送出。所以,仍需要软件设计中做好总线仲裁

485自动收发电路

最新推荐文章于 2025-06-26 20:01:09 发布

本文深入解析了RS-485自动收发电路的工作原理,包括发送与接收状态转换,以及如何利用三极管和电阻实现发零不发一的功能。详细介绍了485芯片的引脚功能,并探讨了半双工通信机制下信号倒回的问题。

本文深入解析了RS-485自动收发电路的工作原理,包括发送与接收状态转换,以及如何利用三极管和电阻实现发零不发一的功能。详细介绍了485芯片的引脚功能,并探讨了半双工通信机制下信号倒回的问题。

4944

4944

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?