imem.v

module imem #(

// --------------------------------------------------------------------------

// Parameter Declarations

// --------------------------------------------------------------------------

parameter AW = 8

)

(

input CLK,

input CEN,

input WEN,

input [31:0]BWEN,

input [AW-1:0]A,

input [31:0]D,

output reg [31:0]Q

);

// -----------------------------------------------------------------------------

// Constant Declarations

// -----------------------------------------------------------------------------

//localparam AWT = ((1<<AW)-1);

// Memory Array

reg [31:0]mem[255:0];

initial $readmemh("D:/workspace/verilog/EDA/RISC-V_CPU_2019/RISC-V_CPU_2019.srcs/sources_1/new/riscv.hex", mem);

always @ (posedge CLK)

begin

if(CEN)

Q <= 32'h0;

else

Q <= mem[A];

end

always @ (posedge CLK)

begin

if(~CEN & ~WEN )

begin

if (~BWEN[0])

mem[A][0] <= D[0];

if (~BWEN[1])

mem[A][1] <= D[1];

if (~BWEN[2])

mem[A][2] <= D[2];

if (~BWEN[3])

mem[A][3] <= D[3];

if (~BWEN[4])

mem[A][4] <= D[4];

if (~BWEN[5])

mem[A][5] <= D[5];

if (~BWEN[6])

mem[A][6] <= D[6];

if (~BWEN[7])

mem[A][7] <= D[7];

if (~BWEN[8])

mem[A][8] <= D[8];

if (~BWEN[9])

mem[A][9] <= D[9];

if (~BWEN[10])

mem[A][10] <= D[10];

if (~BWEN[11])

mem[A][11] <= D[11];

if (~BWEN[12])

mem[A][12] <= D[12];

if (~BWEN[13])

mem[A][13] <= D[13];

if (~BWEN[14])

mem[A][14] <= D[14];

if (~BWEN[15])

mem[A][15] <= D[15];

if (~BWEN[16])

mem[A][16] <= D[16];

if (~BWEN[17])

mem[A][17] <= D[17];

if (~BWEN[18])

mem[A][18] <= D[18];

if (~BWEN[19])

mem[A][19] <= D[19];

if (~BWEN[20])

mem[A][20] <= D[20];

if (~BWEN[21])

mem[A][21] <= D[21];

if (~BWEN[22])

mem[A][22] <= D[22];

if (~BWEN[23])

mem[A][23] <= D[23];

if (~BWEN[24])

mem[A][24] <= D[24];

if (~BWEN[25])

mem[A][25] <= D[25];

if (~BWEN[26])

mem[A][26] <= D[26];

if (~BWEN[27])

mem[A][27] <= D[27];

if (~BWEN[28])

mem[A][28] <= D[28];

if (~BWEN[29])

mem[A][29] <= D[29];

if (~BWEN[30])

mem[A][30] <= D[30];

if (~BWEN[31])

mem[A][31] <= D[31];

end

end

endmodule

IF.v

module IF(

input clk,

input nrst,

input stall,

input br_en,

input [31:0 ] br_addr,

output [31:0] PC,

output [31:0] ins_out

);

reg CEN = 1'b0;

reg WEN = 1'b1;

reg BWEN = 32'h0;

reg [31:0] D = 32'h0;

reg [31:0] PC_reg = 32'h0;

imem imem0(

.CLK(clk),

.CEN(CEN),

.WEN(WEN),

.BWEN(BWEN),

.A(PC[9:2]),

.D(D),

.Q(ins_out)

);

always @ (posedge clk)

begin

if(~nrst)

begin

PC_reg = 32'h0;

end

else if(~stall)

PC_reg <= PC + 32'd4;

end

assign PC = br_en ? br_addr:PC_reg;

endmodule

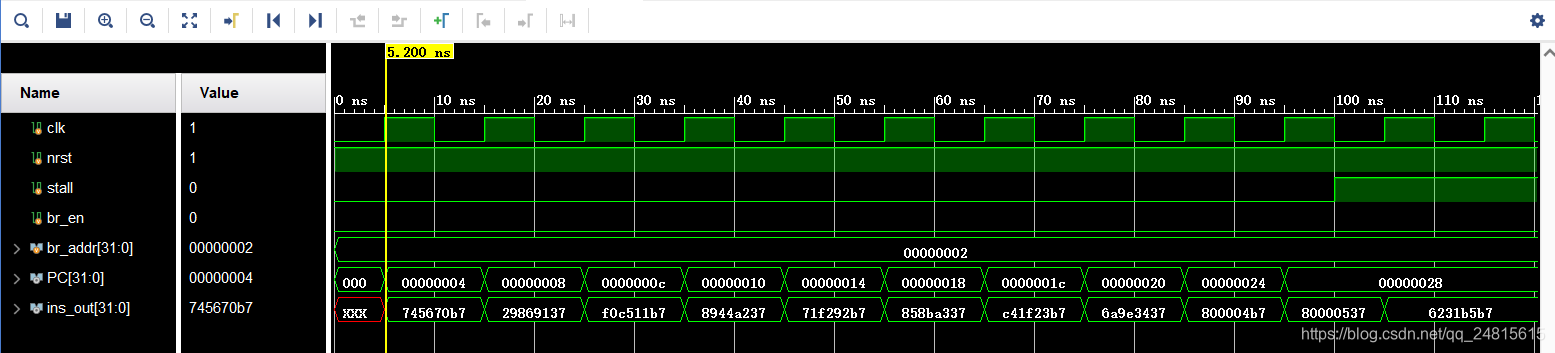

IF_tb.v

`timescale 1ns / 1ps

module IF_tb(

);

reg clk;

reg nrst;

reg stall;

reg br_en;

reg [31:0 ] br_addr;

wire [31:0] PC;

wire [31:0] ins_out;

IF IF1 (

.clk(clk),

.nrst(nrst),

.stall(stall),

.br_en(br_en),

.br_addr(br_addr),

.PC(PC),

.ins_out(ins_out)

);

initial

begin

clk = 0;

nrst = 1;

stall = 0;

br_en = 0;

br_addr = 32'h2;

#100 stall = 1;

#100 stall = 0;

#50 br_en = 1;

#50 br_en = 0;

end

always #5 clk = ~clk;

endmodule

博客内容展示了三个Verilog文件,分别为imem.v、IF.v和IF_tb.v,这些文件与Verilog HDL相关,属于嵌入式硬件领域的信息技术内容。

博客内容展示了三个Verilog文件,分别为imem.v、IF.v和IF_tb.v,这些文件与Verilog HDL相关,属于嵌入式硬件领域的信息技术内容。

931

931

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?