在SystemVerilog Assertions(SVA)中,|-> 和 |=> 是两种不同的隐式条件操作符,它们的用法和行为有所不同。

1. |->(重叠隐式条件操作符)

-

定义:

|->是一个重叠隐式条件操作符,用于检查条件是否在当前周期满足,并在同一个周期内触发后续的序列。 -

行为:如果条件在当前周期为真,则后续的序列会在当前周期开始执行。

-

语法:

-

property p; a |-> b; endproperty -

解释:如果

a在当前周期为真,则b必须在当前周期为真,否则断言失败。

2. |=>(非重叠隐式条件操作符)

-

定义:

|=>是一个非重叠隐式条件操作符,用于检查条件是否在当前周期满足,并在下一个周期触发后续的序列。 -

行为:如果条件在当前周期为真,则后续的序列会在下一个周期开始执行。

-

语法:

-

property p; a |=> b; endproperty -

解释:如果

a在当前周期为真,则b必须在下一个周期为真,否则断言失败。

3. 区别

-

触发时间点:

-

|->:条件和序列都在当前周期触发。 -

|=>:条件在当前周期触发,序列在下一个周期触发。

-

-

适用场景:

-

|->:用于检查条件和结果在同一个周期内发生的情况。 -

|=>:用于检查条件在当前周期发生,结果在下一个周期发生的情况。

-

4. 举例

// SVA断言:在tagError上升后,tErrorBit和mCheck需在后续某周期同时上升

property tag_error_check;

@(posedge clk)

//$rose(tagError) |-> ##[10:30] ($rose(tErrorBit) ##0 $rose(mCheck));

$rose(tagError) |=> ##[10:30] ($rose(tErrorBit) ##0 $rose(mCheck));

endproperty

// 断言实例化

assert property (tag_error_check)

$display("Assertion passed @ %0t", $time);

else $error("Assertion failed: tErrorBit and mCheck @ %0t!", $time);

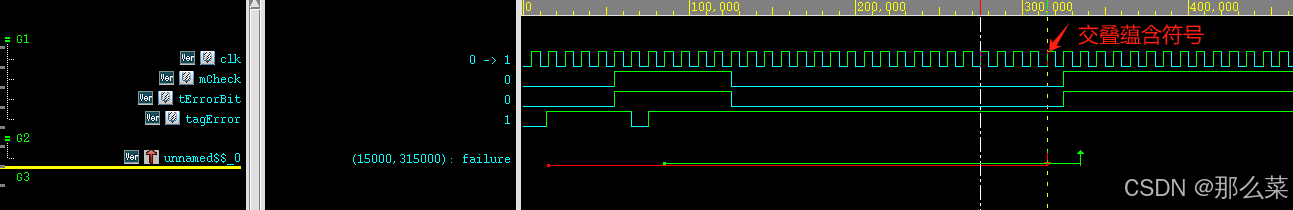

4.1 交叠蕴含符号

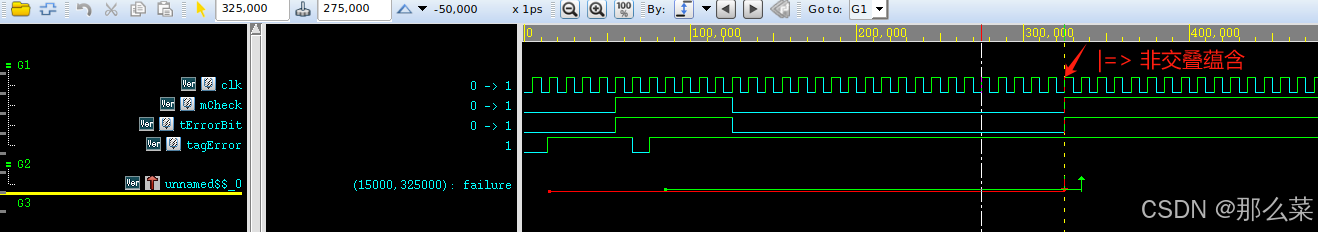

4.2 非交叠蕴含符号

5. 总结

-

|->:条件和结果在同一个周期内检查。 -

|=>:条件在当前周期检查,结果在下一个周期检查。

选择使用哪个操作符取决于你希望检查的条件和结果的时间关系。

802

802

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?