前言

之前的文章,有讲述过通过config_db方式,向interface 进行传递数据的方法。有没有其它方法呢?可不可以直接将类,作为interface 参数化的入口呢?今天,不妨试试看。

正文

相信,亲自搭建过基于systemverilog 验证平台的同仁们,都有过这种感觉:基于UVM 的验证平台的推广,确确实实给我们芯片验证人员,减轻了太多太多的担子。让我们集中精力写具体case,而不过多的花费去调试平台的框架,避免踩踏各种代码编写带来的陷阱。而往往这些陷阱,解决起来并不是那么容易。事事都具有两面性,UVM封装的过于完美,也让我们对其内部感到两眼发黑。而其内部究竟是如何实现的,如果能发掘一下,毕竟对自己上手亲自搭建验证平台,受益匪浅。

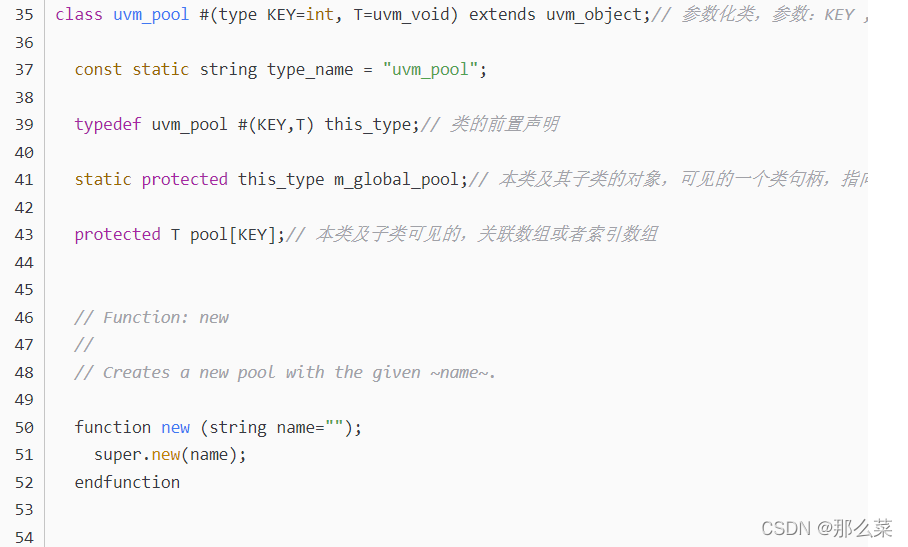

言归正传,研究过UVM 源码的同学,是否记得,SystemVerilog已经开始支持使用参数化类编写泛型代码。如下:

问题来了:那么interface 可不可以 具有同样类似的形式呢?那样不就是直接可以找到了新的一条路走。当然,我们

本文探讨了如何在SystemVerilog的UVM验证环境中,使用类参数化的方式对interface进行参数化设计。通过示例代码展示了如何传递`uvm_event_pool`和自定义配置类`u_cfg`,以实现接口的灵活配置和同步通信功能。文章旨在揭示UVM内部实现的一种可能途径,帮助读者更好地理解和应用UVM。

本文探讨了如何在SystemVerilog的UVM验证环境中,使用类参数化的方式对interface进行参数化设计。通过示例代码展示了如何传递`uvm_event_pool`和自定义配置类`u_cfg`,以实现接口的灵活配置和同步通信功能。文章旨在揭示UVM内部实现的一种可能途径,帮助读者更好地理解和应用UVM。

订阅专栏 解锁全文

订阅专栏 解锁全文

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?