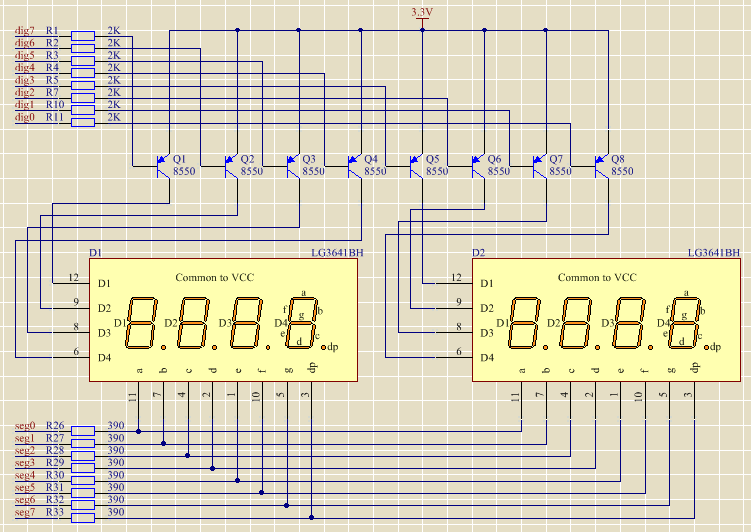

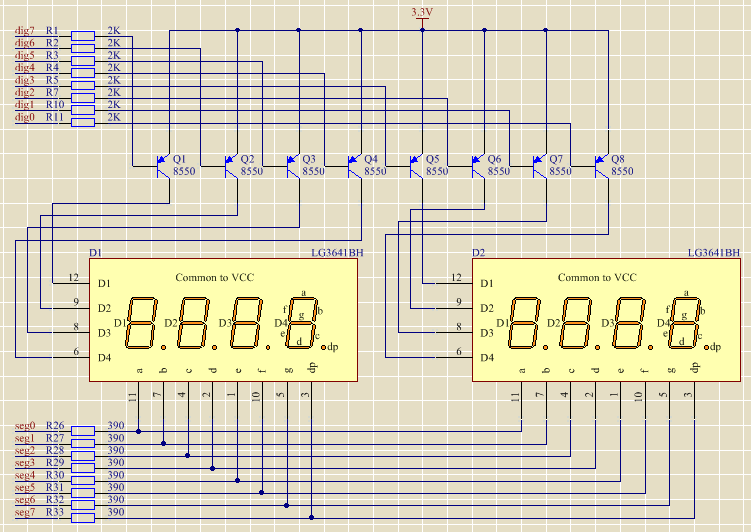

本日志继续介绍Verilog的层次化设计方法,数码管的位选,电路图不变,如下图所示。

该电路图由8位数码管组成,这8位数码管共用一组段选,所以为了让这8位数码管显示不同的数字,必须利用人眼的视觉暂留效应,在时间上的某一时刻,指选中1位数码管。

数码管的选通电路,采用PNP三极管,低电平有效,也就是说,我们希望选中的数码管需要置成0,而其它位都必须置成1。

Verilog代码如下:

解释如下:

1、定义模块,并取名为mod_dig,意为位选模块。

2、带有2个端口分别为number和dig,number用于传递需要选中的数码管位,dig用于真正操作数码管选中相应的位。

3、将端口number方向定义为输入(3位),将端口dig方向定义为输出(8位)。

4、 定义dig为寄存器型,以便于在always@中同时动作,以避免“竞争-冒险”现象的发生。

该电路图由8位数码管组成,这8位数码管共用一组段选,所以为了让这8位数码管显示不同的数字,必须利用人眼的视觉暂留效应,在时间上的某一时刻,指选中1位数码管。

数码管的选通电路,采用PNP三极管,低电平有效,也就是说,我们希望选中的数码管需要置成0,而其它位都必须置成1。

Verilog代码如下:

module mod_dig(number, dig);

input[3:0] number;

output[7:0] dig;

reg[7:0] dig;

parameter DIG7 = 8'b01111111;

parameter DIG6 = 8'b10111111;

parameter DIG5 = 8'b11011111;

parameter DIG4 = 8'b11101111;

parameter DIG3 = 8'b11110111;

parameter DIG2 = 8'b11111011;

parameter DIG1 = 8'b11111101;

parameter DIG0 = 8'b11111110;

parameter DIGN = 8'b11111111;

always @(number)

begin

case (number)

3'd7: dig <= DIG7;

3'd6: dig <= DIG6;

3'd5: dig <= DIG5;

3'd4: dig <= DIG4;

3'd3: dig <= DIG3;

3'd2: dig <= DIG2;

3'd1: dig <= DIG1;

3'd0: dig <= DIG0;

default: dig <= DIGN;

endcase

end

endmodule

解释如下:

1、定义模块,并取名为mod_dig,意为位选模块。

2、带有2个端口分别为number和dig,number用于传递需要选中的数码管位,dig用于真正操作数码管选中相应的位。

3、将端口number方向定义为输入(3位),将端口dig方向定义为输出(8位)。

4、 定义dig为寄存器型,以便于在always@中同时动作,以避免“竞争-冒险”现象的发生。

5、设置位选参数。

6、在 always@中完成数字到位选的转换。

优快云:http://blog.youkuaiyun.com/qingwufeiyang12346 。

6、在 always@中完成数字到位选的转换。

有任何问题欢迎留言,我尽最大可能予以解答,知而获智,智达高远。

原创性文章,转载请注明出处

http://user.qzone.qq.com/2756567163

。

优快云:http://blog.youkuaiyun.com/qingwufeiyang12346 。

本文介绍使用Verilog实现数码管位选的方法,通过位选参数设置和always@语句,实现不同数字对应的数码管选通。适用于初学者了解如何利用视觉暂留效应进行数码管显示。

本文介绍使用Verilog实现数码管位选的方法,通过位选参数设置和always@语句,实现不同数字对应的数码管选通。适用于初学者了解如何利用视觉暂留效应进行数码管显示。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?