目标:

bit[7:0] c = 8’hffff_ffff;//8bit无符号整数

byte d = 8’hfff_ffff; //8bit 有符号整数

文件名称:bit_logic_operator.sv

module bit_logic_operator();

bit [7:0] bi;

byte by;

$display ("bi=%d",bi);

$display ("bi=%d",by);

endmodule

命令:vcs -R -sverilog bit_logic_operator.sv

说明:多个.sv文件,在后面直接加就行

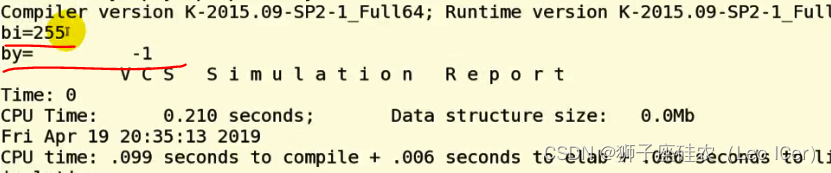

仿真结果,如下所示:

byte 有符号8位数,取反+1,存入的,反推回去是-1

该篇博客介绍了使用Verilog进行8位无符号整数(c)和有符号整数(d)的逻辑操作。在仿真中,8位无符号整数c被初始化为最大值,而8位有符号整数d被初始化为最大的负值(补码表示)。通过$display展示变量的值,展示了8位有符号数取反加1后得到-1的过程。

该篇博客介绍了使用Verilog进行8位无符号整数(c)和有符号整数(d)的逻辑操作。在仿真中,8位无符号整数c被初始化为最大值,而8位有符号整数d被初始化为最大的负值(补码表示)。通过$display展示变量的值,展示了8位有符号数取反加1后得到-1的过程。

3229

3229

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?