QuartusII调用PLL IP核实现分频、倍频(适用于17.1以上版本)

从Quartus 17.1开始,软件有一些重大更新内容,比如把一些Quartus内部集成的功能名字改了,让用户特别是初学者更容易理解这些功能的用处。本文在QuartusI18的基础上,使用小脚丫FPGA Max10M08SAM进行简单的调用PLL IP核心进行分、倍频率。

1.设置工程目录

2.选择器件

3.选择仿真工具

4.查看工程预设信息

5.Tools>>IP catalog,并在搜索框内输入“ALTPLL”;

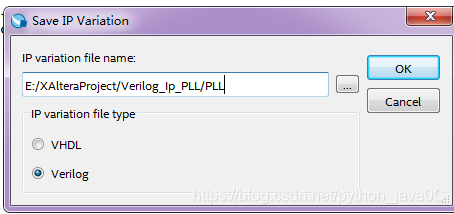

6.双击,在目录后面追加PLL,点击“OK”;

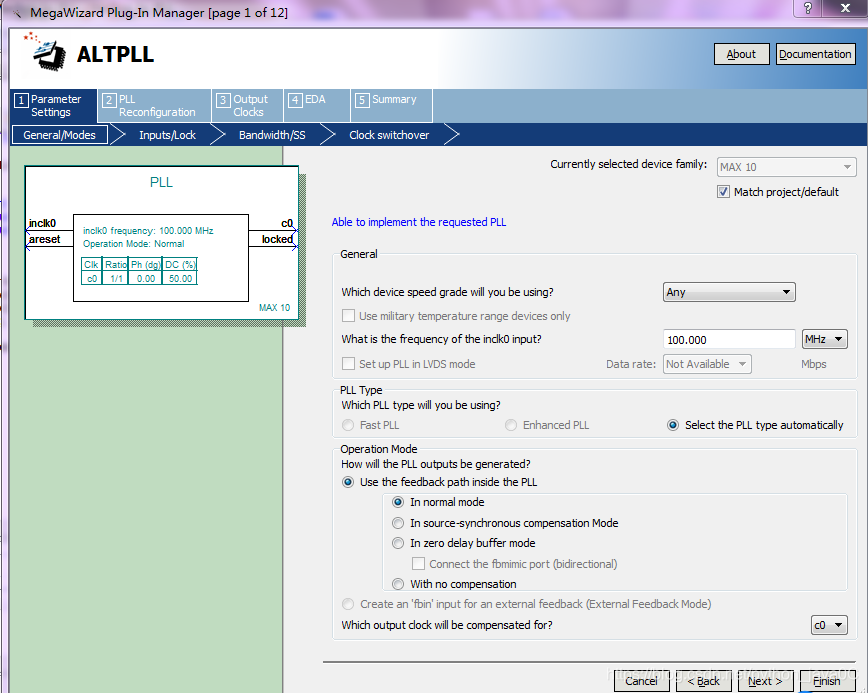

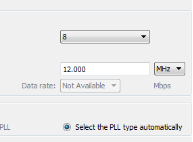

7.跳出如下页面,由于小脚丫FPGA MAX10外部时钟频率为!12MHZ,这里配置输入频率为12M,其他默认;

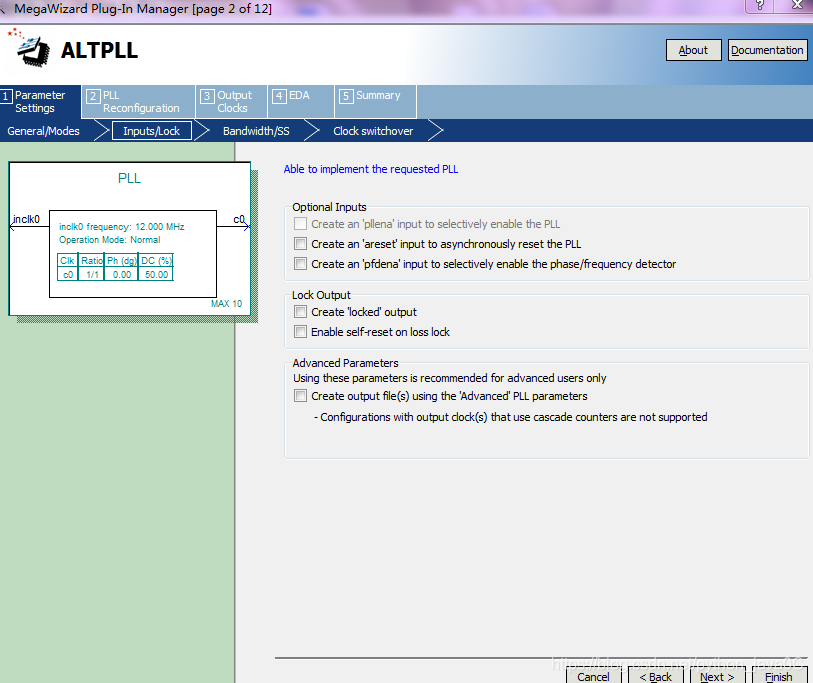

8.点击“next”,这里可以根据需要选择是否勾选;

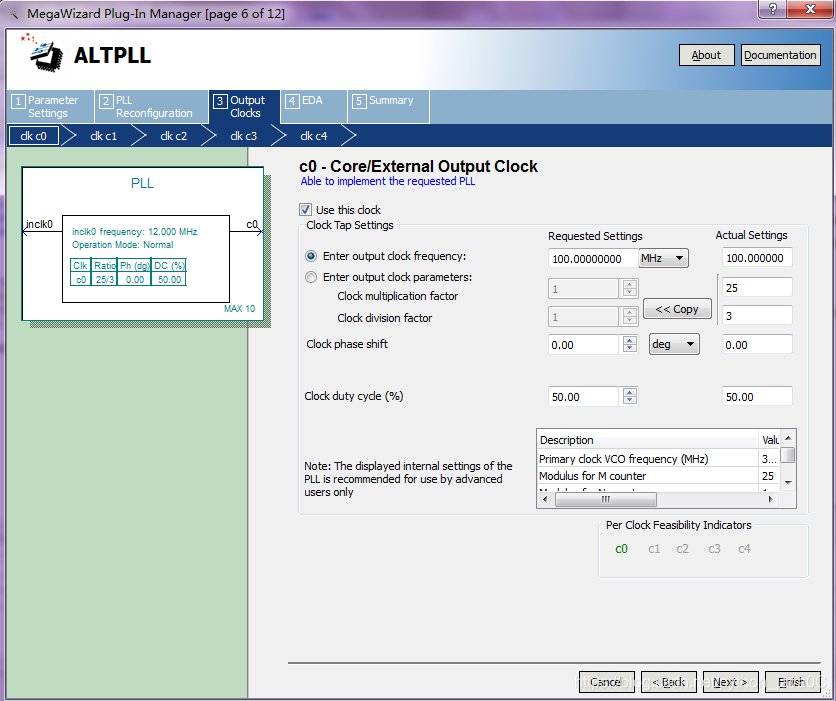

9.接下来一直点击“next”,即保持默认,当然可以根据需要选择是否配置;到如下界面时进行输出频率的配置;这里配置两个频率,倍频100M,分频1M。分别对应clk c0,clk c1,可以根据需要配置相位和占空比;

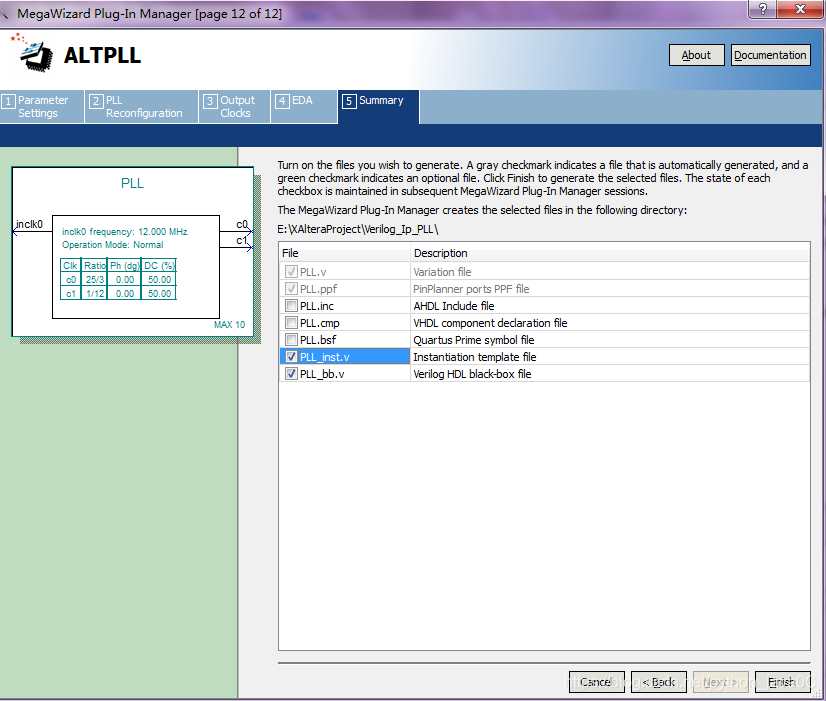

10.最后,配置输出文件,点击“Finish”;

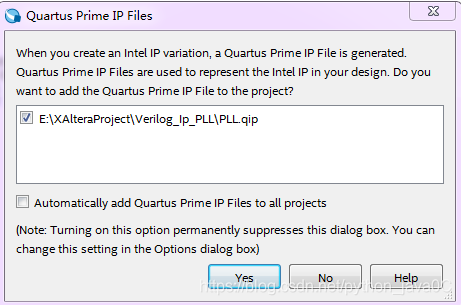

11.弹出对话框问“是否把IP文件加入到工程中?

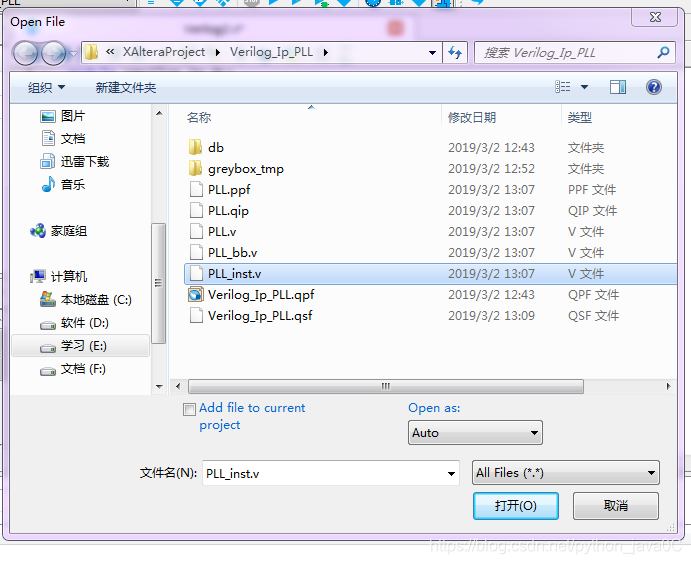

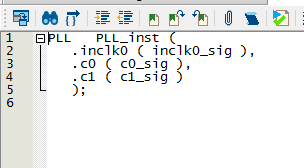

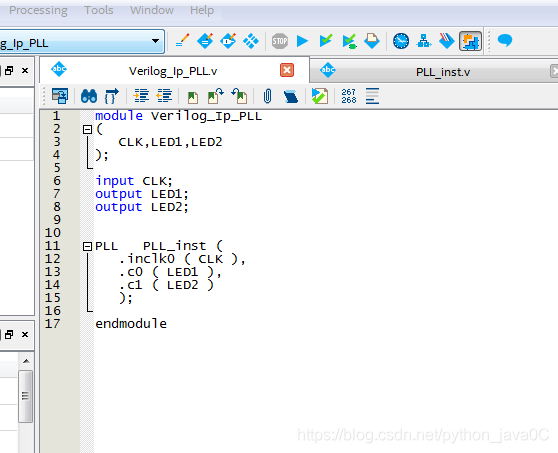

12.打开当前工程目录,找到PLL_inst.v文件,并打开,文件为PLL实例化模版;

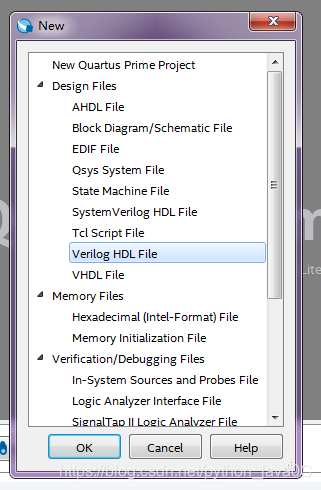

13.新建Verilog文件,复制PLL_inst.v文件中的实例模版,即可调用PLL IP核;我编写的实例代码如图所示;

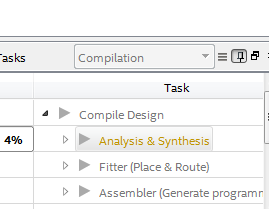

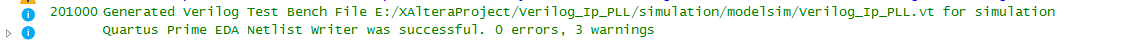

14.双击“Tasks”栏目中“Analysis&Synthesis”,看是否有错误;

15.点击菜单栏中的“Processing”>>“Start”>>“Start TestBench Template Writer”,用于生成仿真文件;生成成功后会打印相应信息;

16.找到生成的.vt文件,打开并修改激励代码如下,并保存;

`timescale 1 ps/ 1 ps

module Verilog_Ip_PLL_vlg_tst();

reg CLK; //输入12MHZ信号

wire LED1; //输出100MHZ信号

wire LED2; //输出1MHZ信号

Verilog_Ip_PLL i1 (

.CLK(CLK),

.LED1(LED1),

.LED2(LED2)

);

initial

begin

#0 CLK = 1'b0;

#10000000 $stop; //设置仿真时间为10000000ps

end

always #41667 CLK=~CLK; //生成12MHZ信号

endmodule

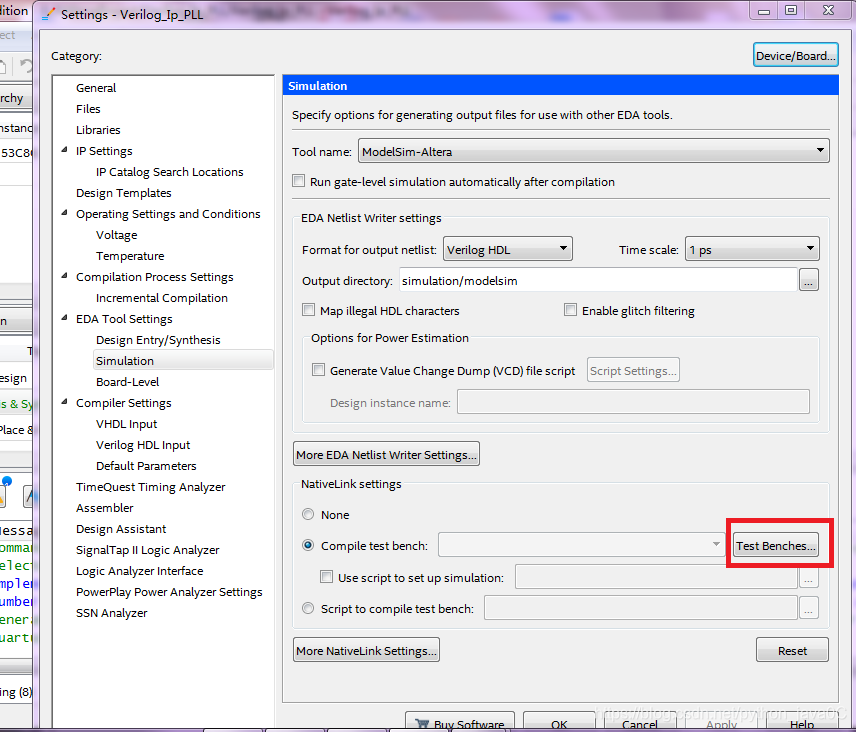

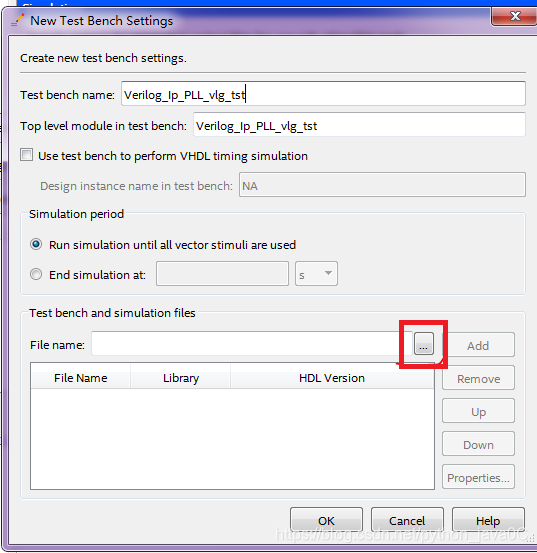

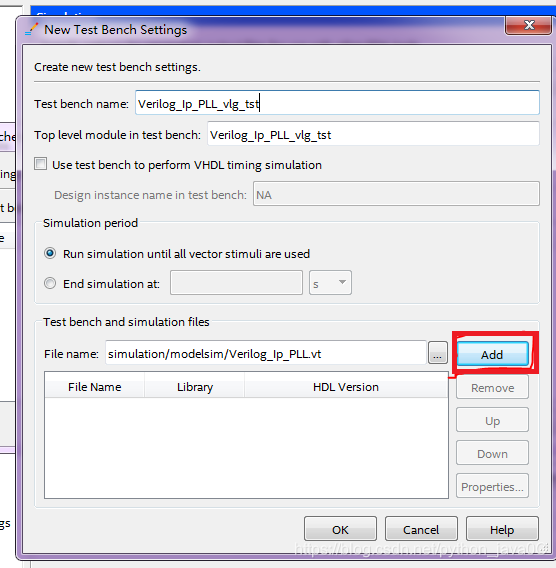

17.点击菜单栏中的“Assignment”>>“Settings”>>“Simulation”>>“Compile test bench”;

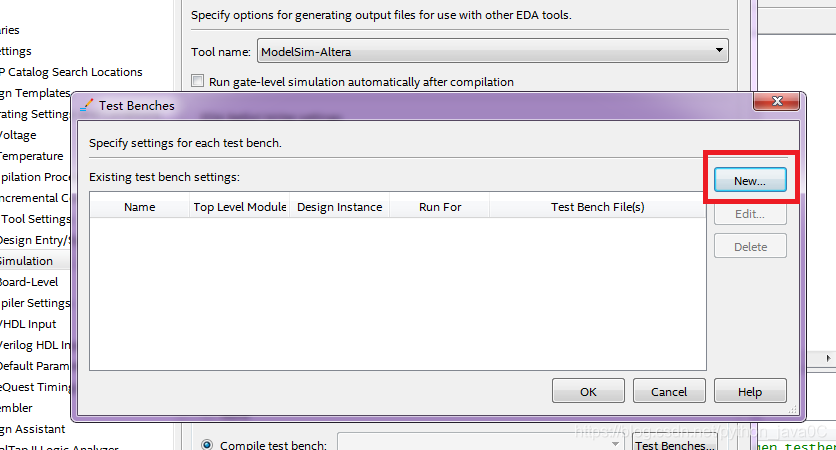

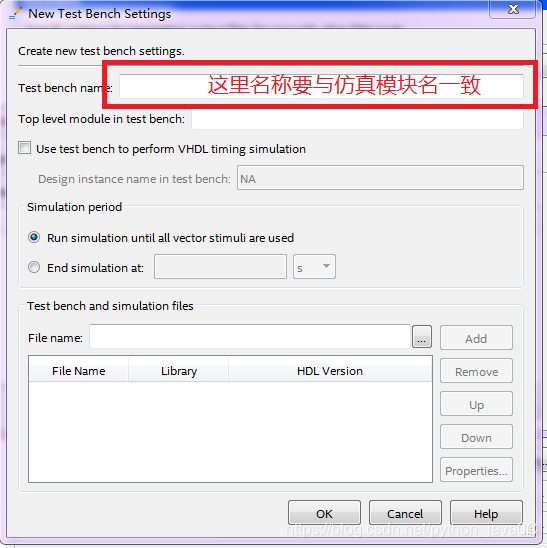

接下来跟随红框一步一步往下;

本例子中仿真模块名为Verilog_Ip_PLL_vlg_tst;

然后一路返回,点击“OK”或“Apply”;

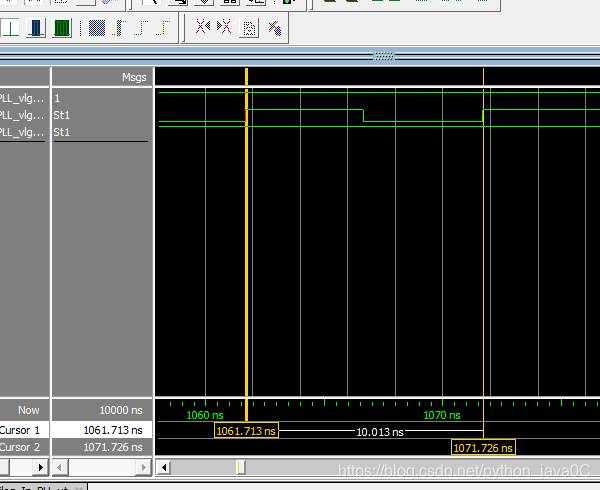

18.“Tools”>>“Run Simulation Tool”>>“RTL Simulation”,等待仿真完成;

19.仿真结果如下,可以看到100M倍频周期大约为1000你是,1M分频为10ns;

这篇博客介绍了如何在QuartusII 17.1及以上版本中调用PLL IP核,以实现FPGA MAX10M08SAM的分频和倍频操作。通过详细步骤,包括设置工程、选择器件、配置PLL参数、生成IP文件和进行仿真,展示了如何创建和验证100MHz倍频和1MHz分频的频率转换功能。

这篇博客介绍了如何在QuartusII 17.1及以上版本中调用PLL IP核,以实现FPGA MAX10M08SAM的分频和倍频操作。通过详细步骤,包括设置工程、选择器件、配置PLL参数、生成IP文件和进行仿真,展示了如何创建和验证100MHz倍频和1MHz分频的频率转换功能。

1万+

1万+