前言

有两年没写过东西了,做了两年天线相关的东西,最近换了工作,又准备开始写一点工作相关的东西了。

最近准备要做有关接收机的项目,先把相关的数字信号处理方面的内容学习一下。

项目简介

目前用的是一个基于AD9364的模块,想在此基础上实现信号源和频谱仪的基本功能。

1.硬件框图

信号接收部分主要流程如下

2.工作流程

首先实现频谱仪的功能,主要是对AD9364采样的数据进行FFT转换为频谱。

第一步,宽带扫描,主要流程如下

第二步,宽带扫描完成后,如果对捕获到的信号进行进一步分析,需要进行窄带扫描,主要是提高频谱分辨率。

我们知道FFT的分辨率是由采样率fs和FFT点数N共同决定的,Δf= N/fs,所以提高分辨率有两种方法

1.降低采样率fs,缺点:会导致采样时间变长,最高可分析频率变低;

2.增加采样点数N,缺点:会导致采样时间变长,增加FFT的计算复杂度和计算时间

我们采用的是第一种方法,具体实现不是直接改变ADC的采样率,而是对采样数据进行抽取,等效为降低fs,这样由于最高可分析频率变低,有可能会导致某些信号丢失,所以还需要增加一个DDC对信号进行下变频。

窄带扫描主要流程如下:

3.matlab仿真

3.1系统仿真框图

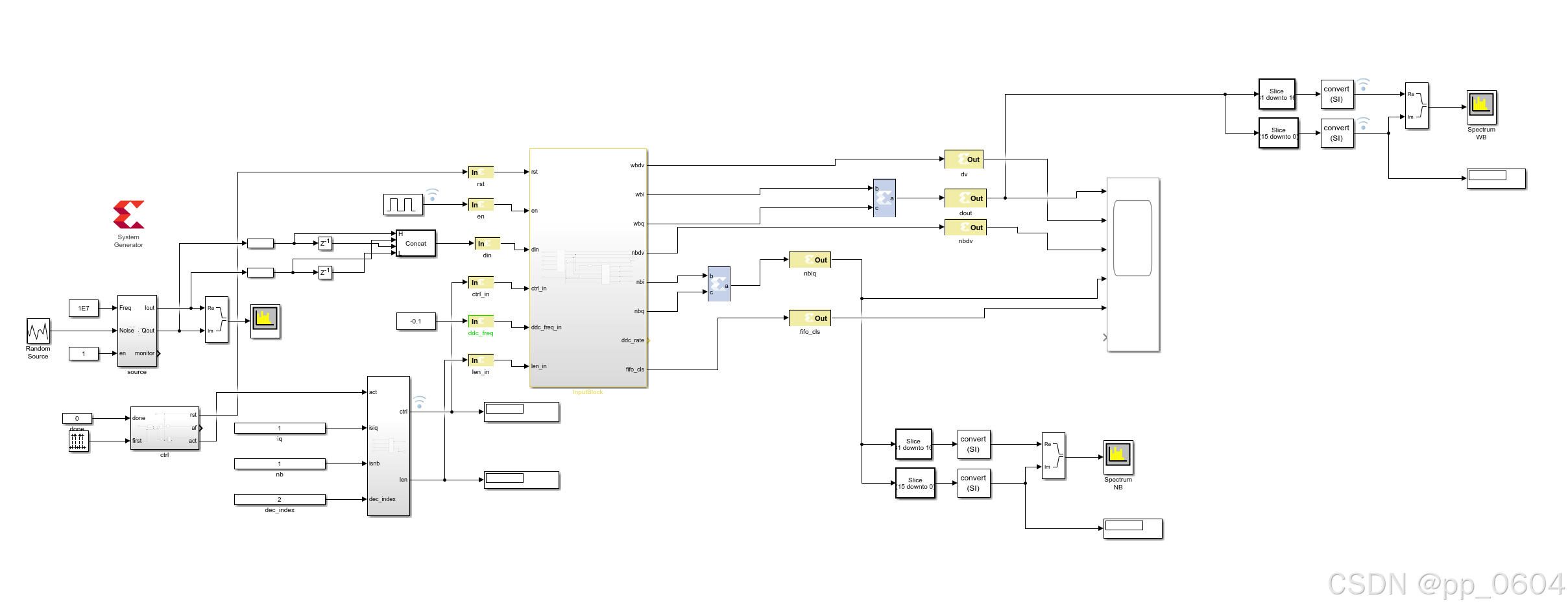

先用matlab对工作流程进行仿真,下图是系统仿真,外部输入端是模拟的一个DQPSK基带+随机噪声的一个组合信号,以及上位机的控制信号(包括开始采集,FFT计算参数,宽带窄带切换等命令)。输出端是采集的宽带IQ数据以及经过抽样滤波后的窄带IQ数据,分别用两个频谱仪进行观察。

3.2 DDC仿真框图

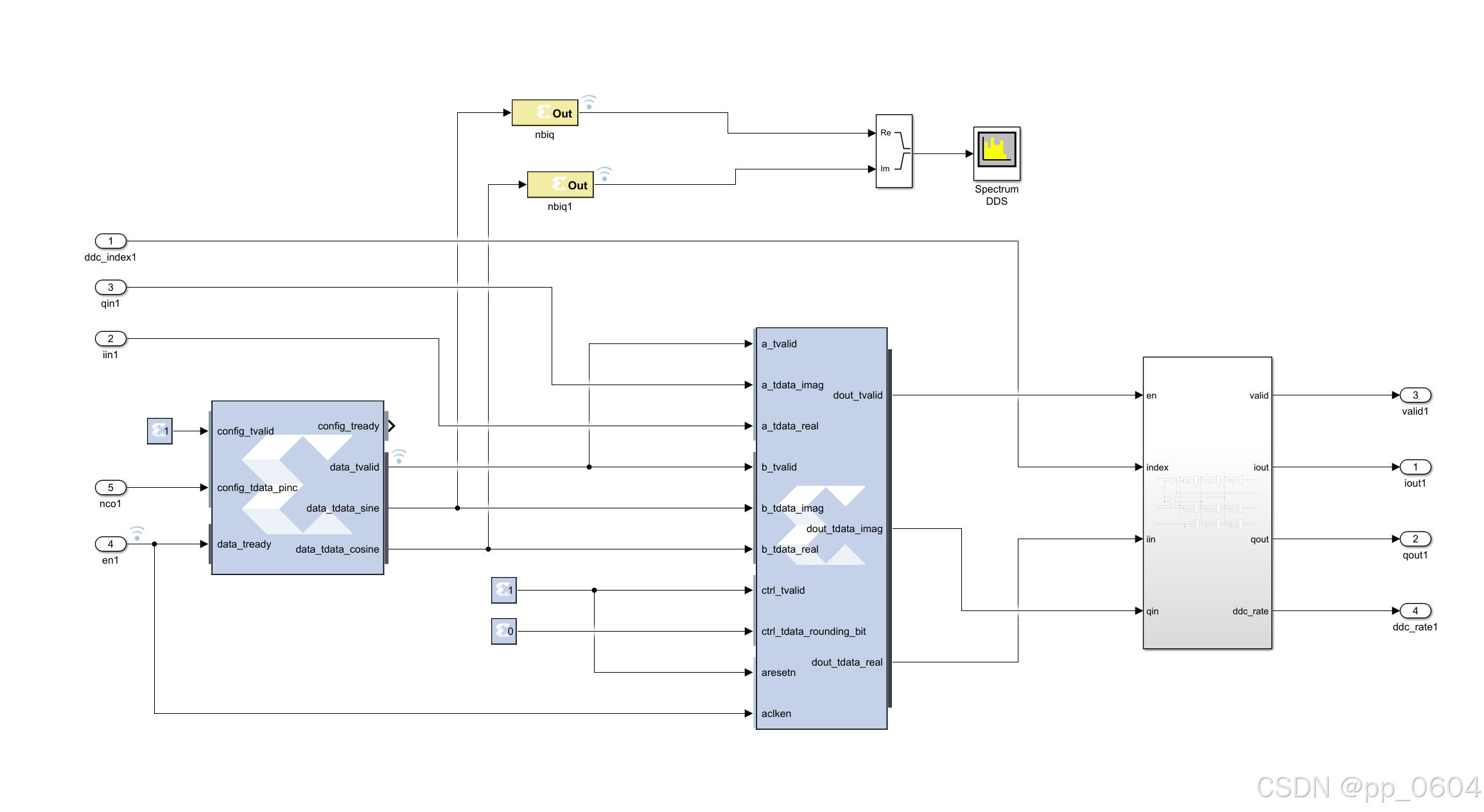

下图是系统仿真里面的DDC模块,主要包括一个DDS6.0频率发生器,一个Complex Multiplier 6.0 混频器和一个自己搭的抽取滤波模块。

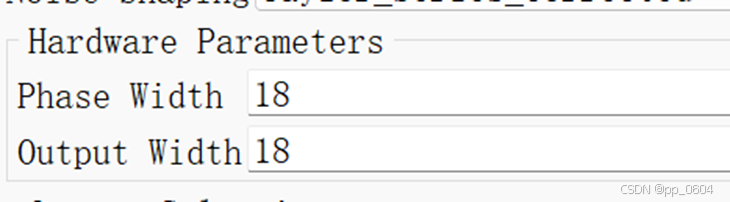

这里顺便写一下DDS6.0的设置吧,我也是弄了好久才弄明白。

首先他的输出频率主要用到的有两个模式,一种是固定值输出,一种是可配置输出。

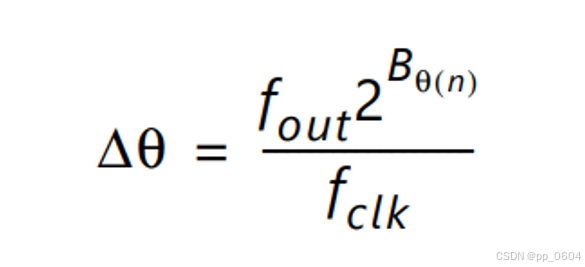

1)固定值输出在DDS模块内设置Δθ的值,这个值的计算公式如下,其中的Bθ(n)是指你设置的相位位宽Phase width,不是输出位宽output width。比如你时钟频率100MHz,如果想输出1MHz信号,计算得到Δθ的值应该是2621.44,转换成二进制大概就是101000111101。

2)如果是配置输入,就是外面输入一个ufix18_18数,这时你时钟频率100MHz,如果想输出1MHz信号,就直接输入0.01就行了。不过很奇怪的是我设置的0.01,输出的频率是-1MHz,必须要输入-0.01,才是1MHz的信号。这个原因我没找到。

3.3 仿真结果

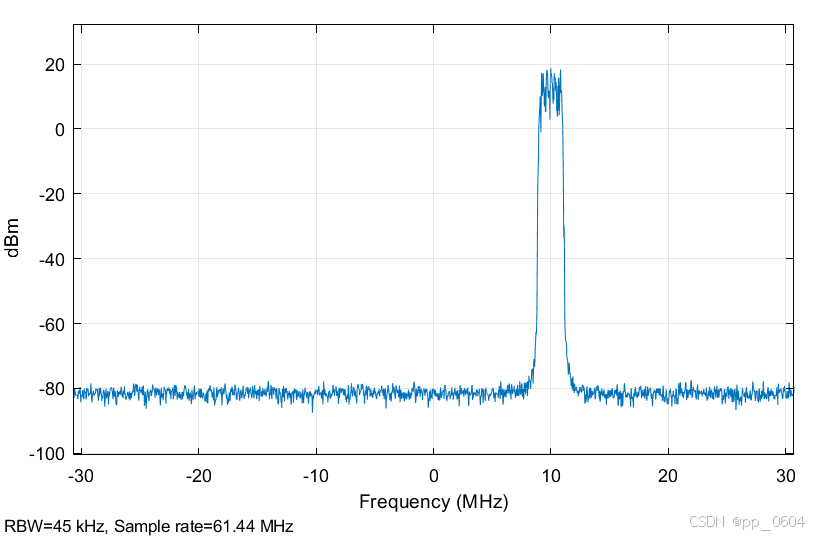

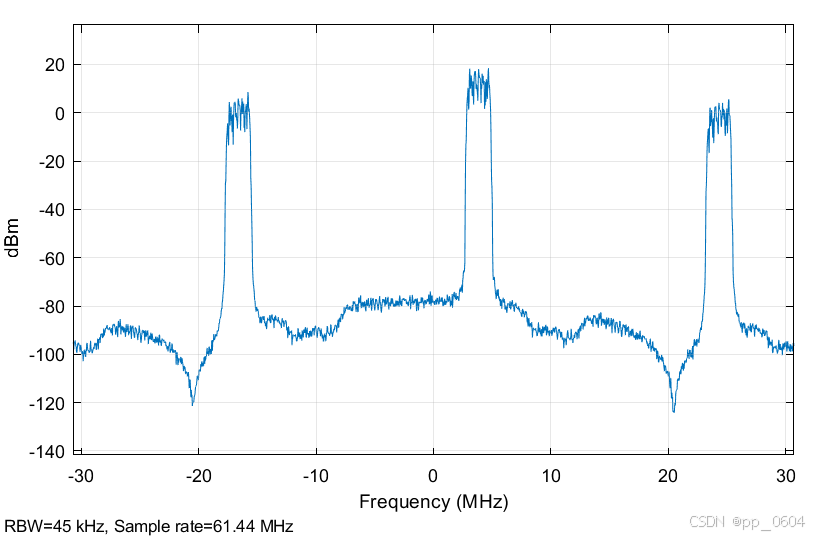

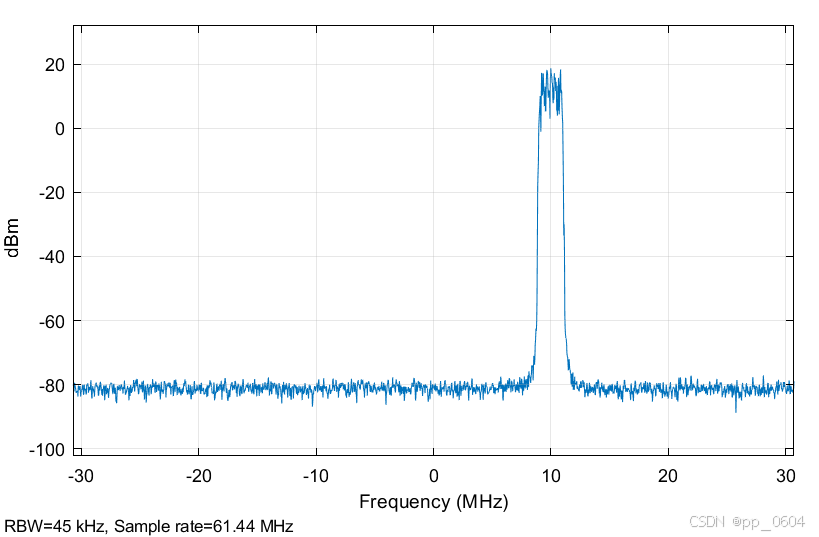

设置输入信号频率10MHz,DDS本振频率为6MH,以下是仿真结果,第一张图是输入信号频谱,第二张图是输出窄带信号频谱,第三张图是输出宽带信号频谱。可以看出宽带信号和输入完全一样。窄带信号频谱从10M下变频到4M,信号带宽没有变化,产生了两个镜频信号。

4 硬件调试

硬件调试后面再做,目前没有时间。

2567

2567

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?