教程参考:

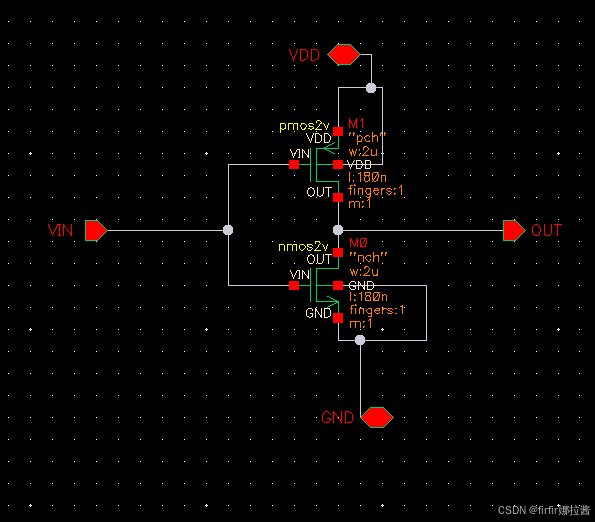

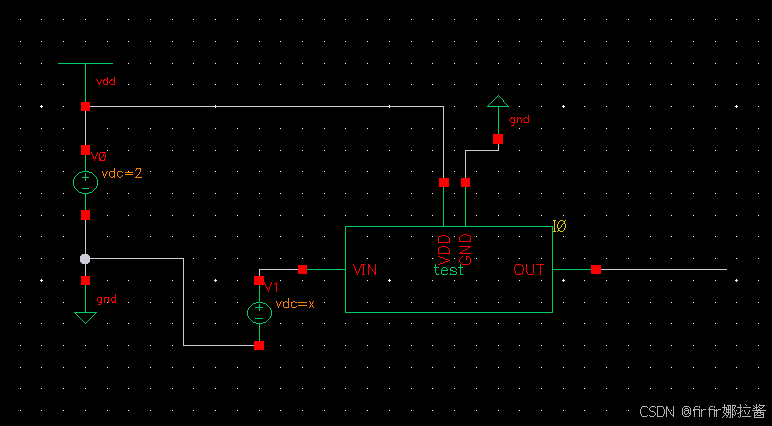

注:使用的反相器原理图如下,使用的是tsmc.18的库,注意pin一定要大写,不然后续提取参数可能会导致pin提取不出来。

绘制版图

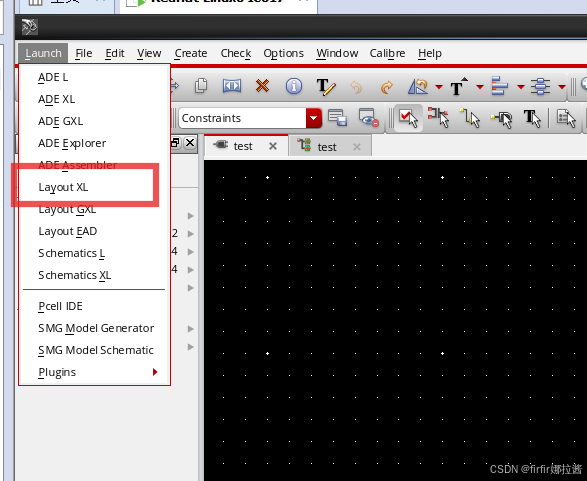

创建layout的文件

在原理图界面点击layoutXL创建

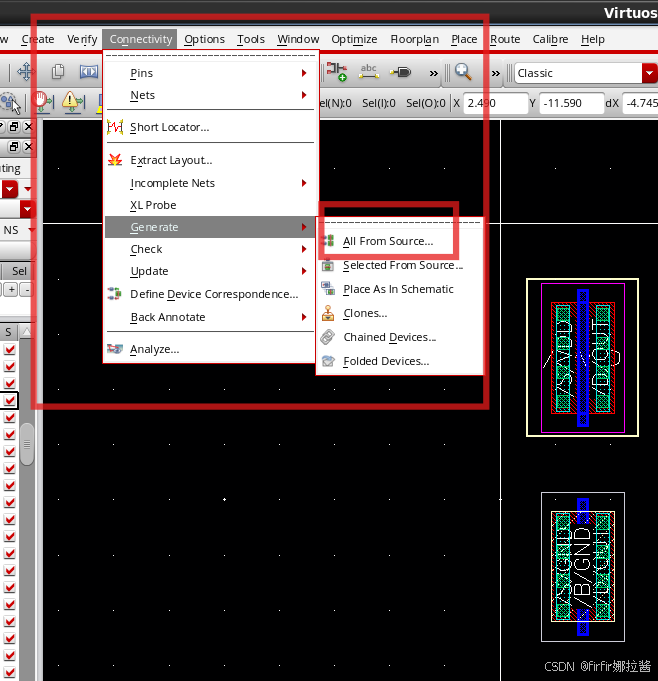

添加器件

connectivity_generate_all from source

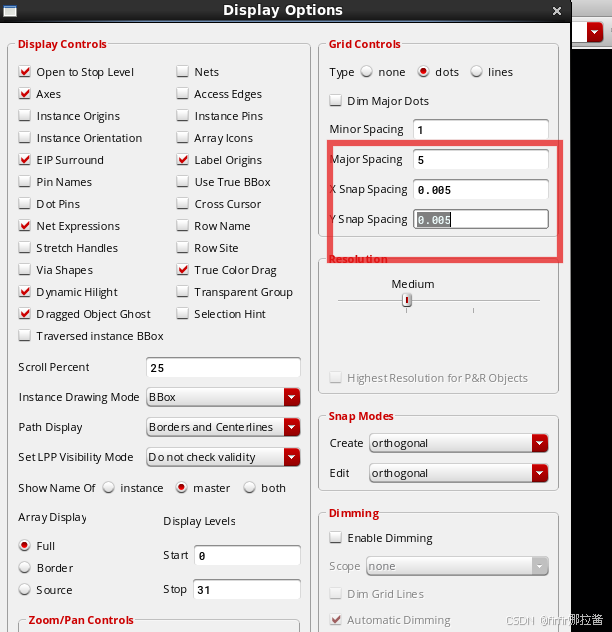

快捷键e:调整格点大小

快捷键p:连线

快捷键Fn_f3:调节连线宽度

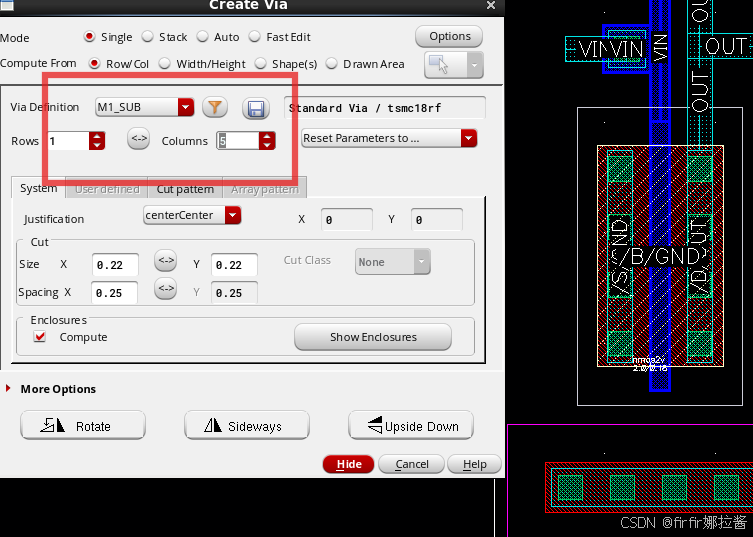

快捷键o:通孔

画GND用M1_SUB材料

画VDD用NWELL材料

快捷键F4:可以调整连线的位置

快捷键R:画一个n阱框起来NWELL

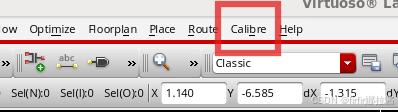

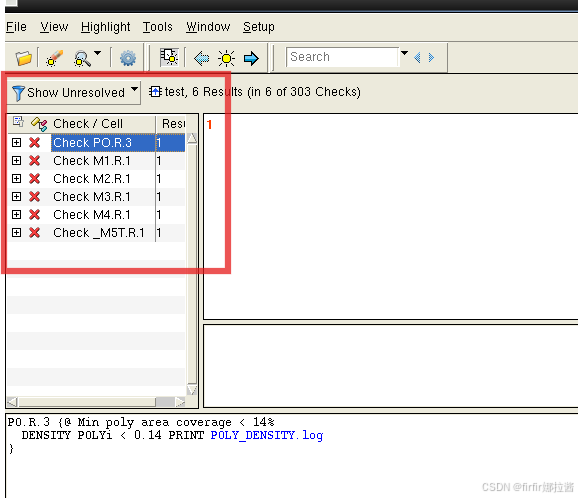

DRC

calibre→drc

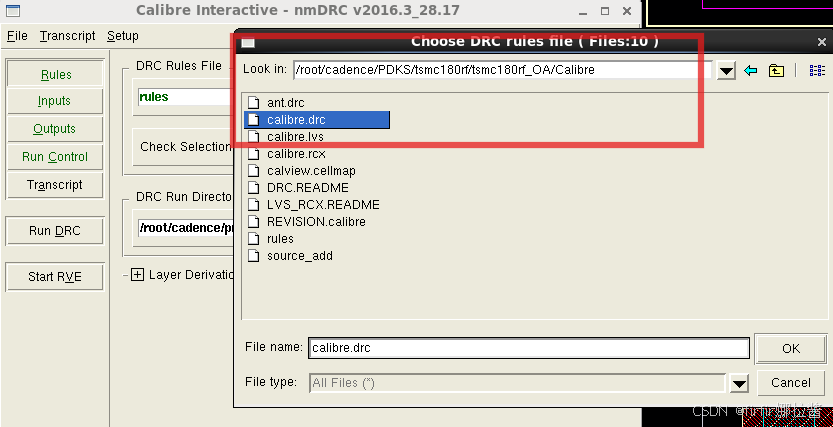

找到drc的rule,点击Run DRC即可

正确无误如图

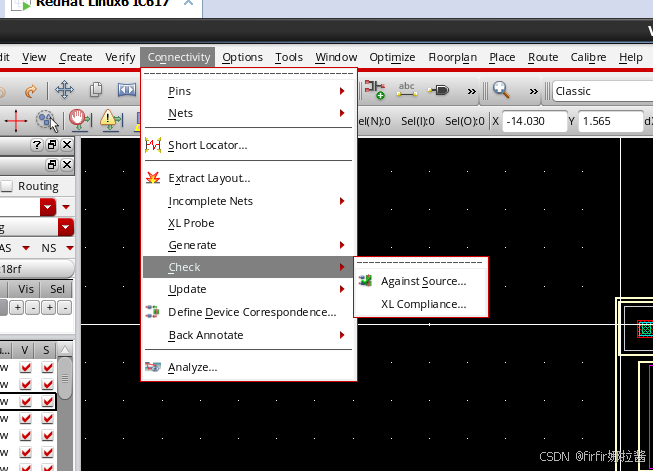

LVS

check一下和原理图是否相符

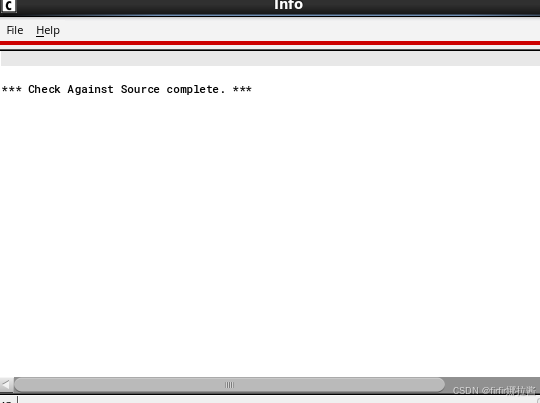

检查无误如图:

打pin:create→pin→名字etc

注:在打pin的时候不要打开你的大写锁定,这样没办法打pin成功

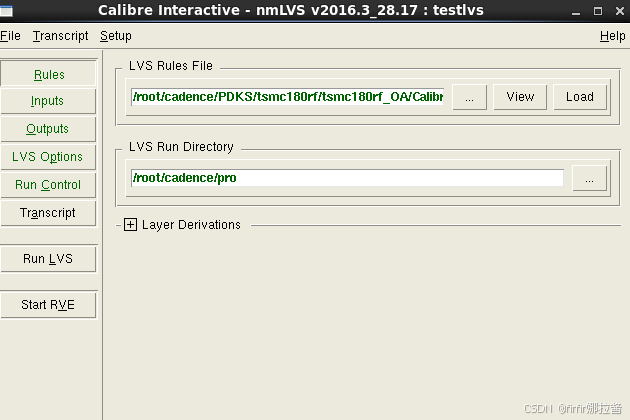

选好rules:在和上一个rules同一个文件夹里面

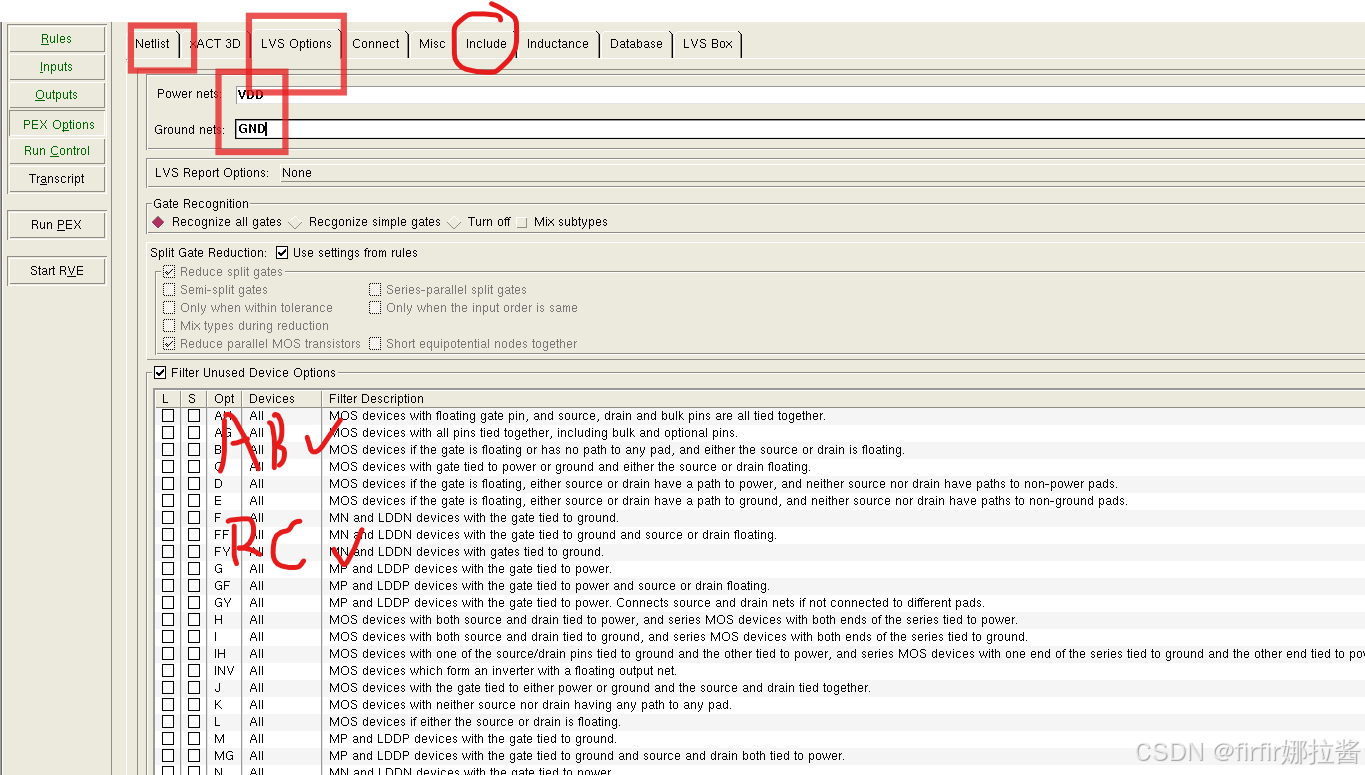

setup→lvs options→调整一下supply和gates

把vdd和gnd放进去;选择AB和RC

快捷键L:打上label

注意材料要用metal pin才可以哈

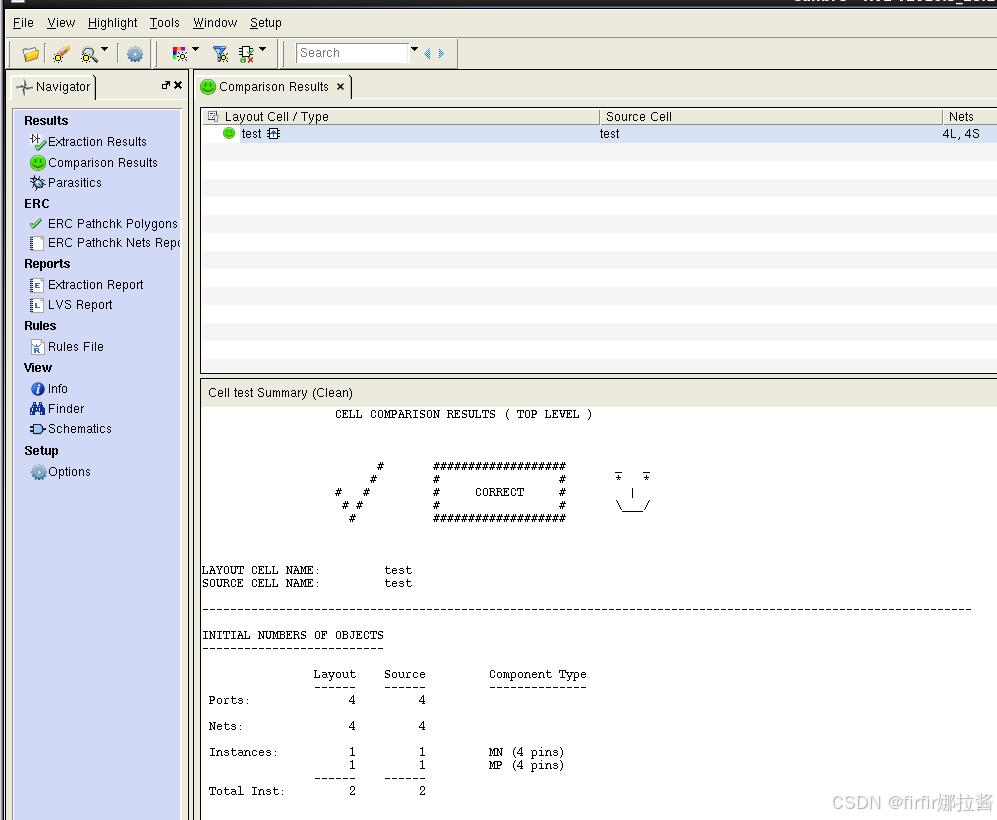

完全无误如图:

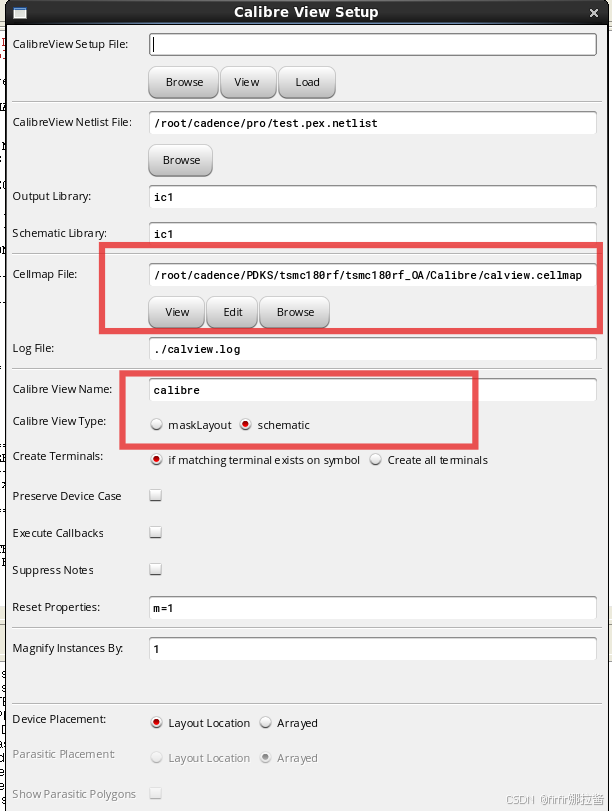

PEX参数提取

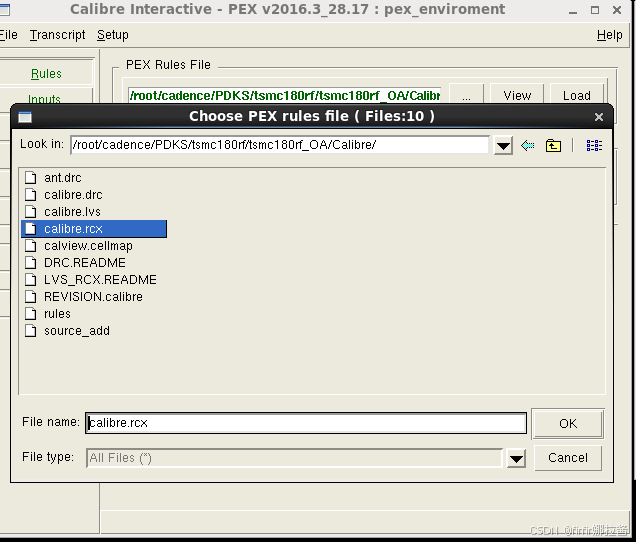

选定rules:rcx

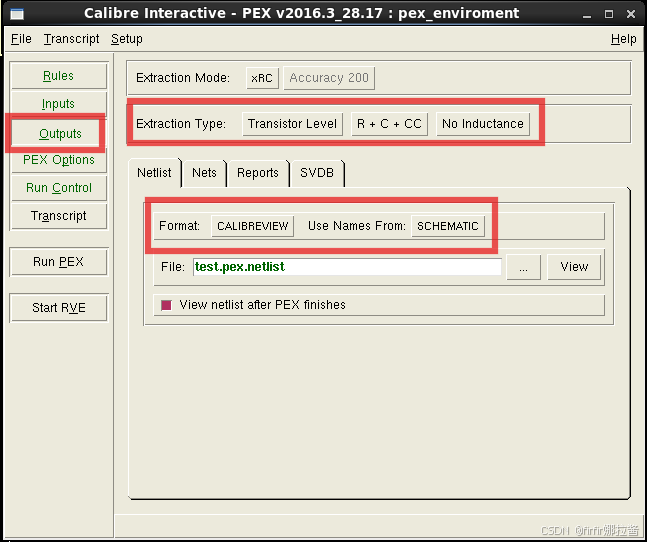

选择outputs

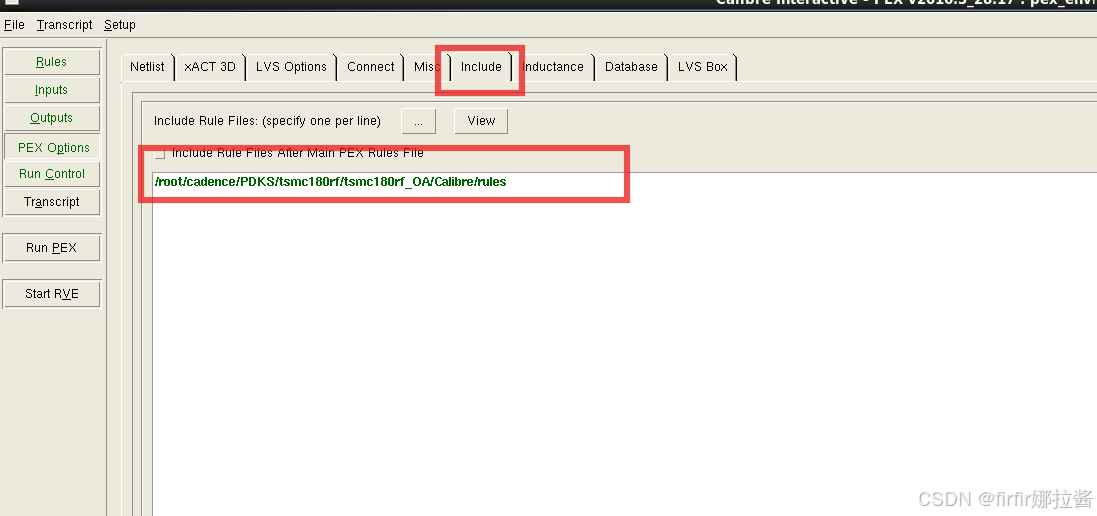

调节pex options:记得include导入rule

点击run pex并且导入cellmap

检查一下四个pin都在,ok!

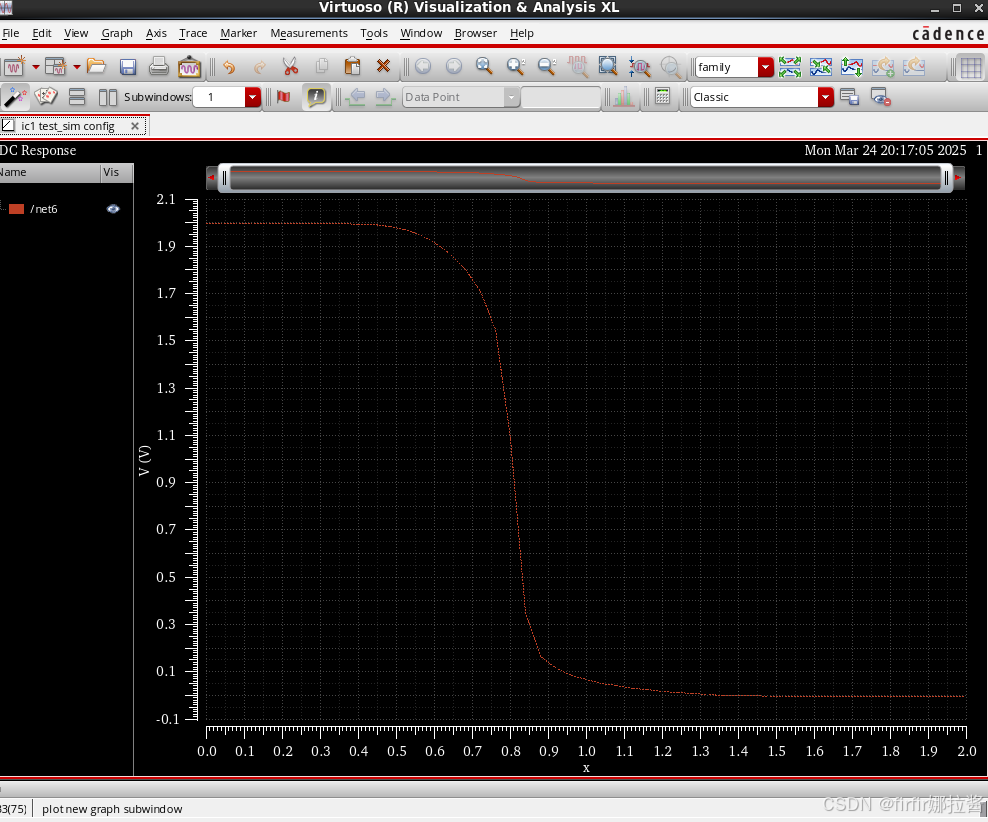

后仿真

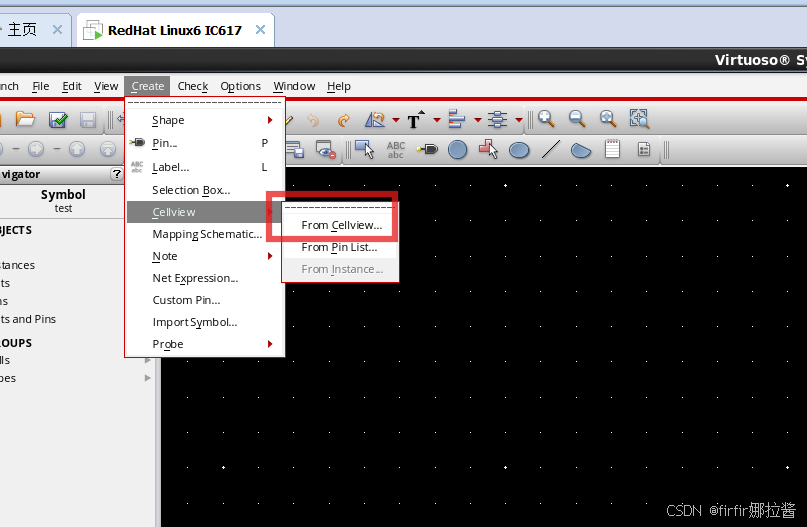

建立一下仿真的原理图(在你本来的原理图界面)

再建立一个原理图file,导入你刚刚集成的器件,给它设计外围测试电路。

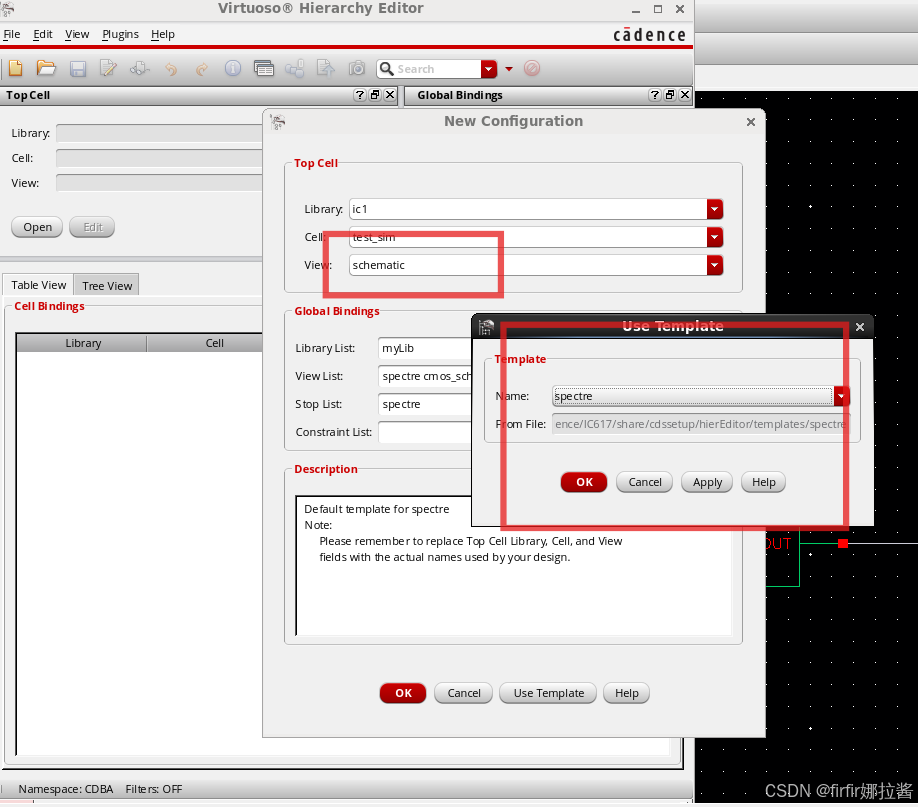

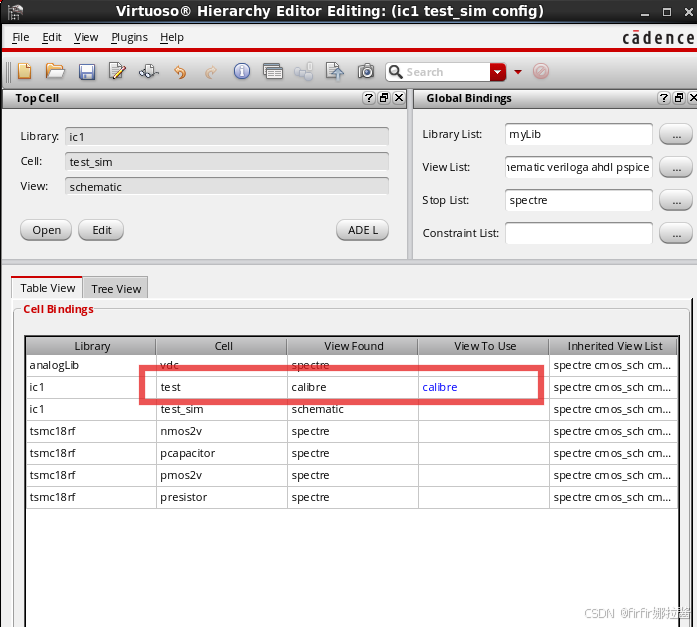

后仿方法1:config

建立一个sim文件的config格式

导入提取参数并且保存一下

重新打开config版本的sim原理图,重新仿真就ok!

别的仿真方法,等这个仿真用不了了我再来学吧。

4555

4555

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?