本文介绍了零延迟缓冲器的基础及如何通过负载来控制个输出的相位关系和布局布线的一些建议。

目录

一. 零延迟缓冲器基本

1.1零延时基础

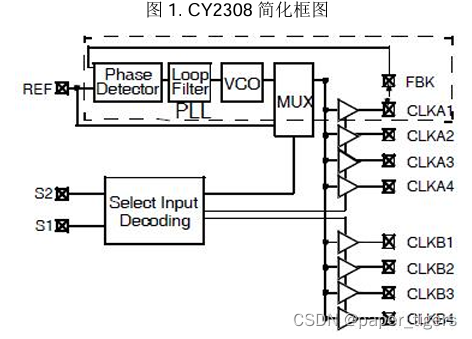

零延迟缓冲器由一个 PLL 构成,提供一个参考输入 REF 和反馈输入 FBK 及多个输出,FBK 由输出驱动。PLL 的相位检测器会检测反馈和参考之间的相位关系,将其转化为电压来调整压控振荡器VCO 的输出频率,保证参考和反馈输入之间不存在相位差异。因为 PLL 控制环包括了一个输出及其负载,所以它完全能够补偿该输出上连接的负载。无论驱动反馈的输出负载如何,PLL 中输入到该输出的延迟均为零。

该零延迟只应用于被反馈输入监控的输出;而所有其它输出则具有输入到输出延迟,该延迟是受输出负载的差异而影响的。以 CY2308 为例:

1.2 各输出延迟(相位)调整

通过对反馈输出提供合适的负载,可使其他输出超前或滞后于参考 REF。在该情况下,使用 PLL可使输出超前或滞后于其它输出。 请注意,CY2308 中有 REF 和 FBK 两个引脚(图 1),它们是PLL 的输入。参考时钟作为REF引脚的输入,而 FBK 引脚则用于在外部关闭反馈路径。 请参考下面所列出的PLL特点, 以便了解将任何输出连接到 FBK 引脚的特性。

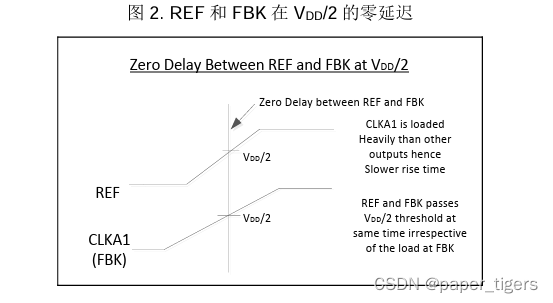

1. PLL 检测 FBK 引脚在阈值等于 VDD/2 的情况下的相位和 REF 引脚在相同的 VDD/2 阈值的情况下的相位,ZDB 始终使用 PLL 的特性进行自调整,使得 REF 和 FBK 同时到达 VDD/2(满足零延时)。

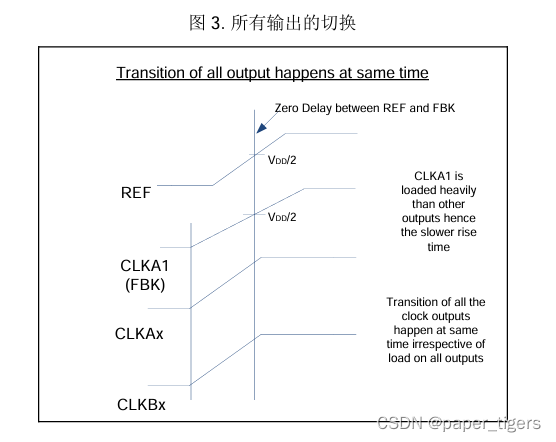

2. 所有输出 CLKB、CLKA(包括驱动 FBK 的输出 CLKA1)同时开始各自的切换。

因此,改变一个输出上的负载会改变它的上升时间,进而改变输出达到 VDD/2 阈值的时间。按此原

本文详细阐述了零延迟缓冲器的工作原理,包括PLL机制如何实现零延时以及如何通过负载控制输出相位。文章还介绍了负载与延时的关系、布线长度对时序的影响,以及优化布局和时钟信号路由的建议。

本文详细阐述了零延迟缓冲器的工作原理,包括PLL机制如何实现零延时以及如何通过负载控制输出相位。文章还介绍了负载与延时的关系、布线长度对时序的影响,以及优化布局和时钟信号路由的建议。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

886

886

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?